封装结构的制作方法

本技术是有关于一种封装结构。

背景技术:

1、由一或多个电子装置组成的当代高效能计算系统已经广泛用于各种高级电子应用中。当对集成电路组件或半导体芯片进行封装用于该些应用时,一或多个芯片封装一般被结合至用于电性连接至其他外部装置或电子组件的电路载体(例如,系统板、印刷电路板或类似载体)。为了对对于小型化、更高速度及更佳电性效能(例如,更低的传输损耗及插入损耗)的需求的增加作出响应,积极地研究更具创造性的封装及组装技术。

技术实现思路

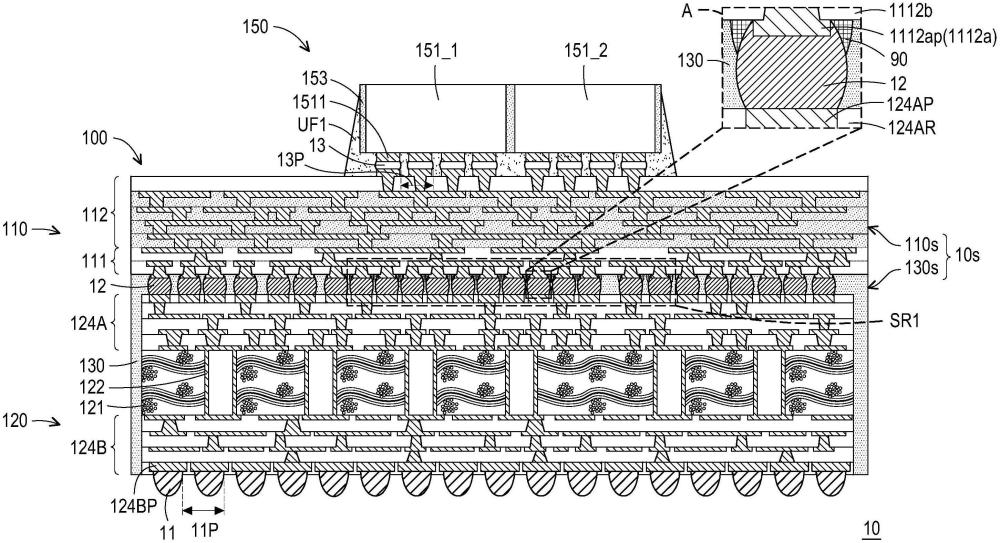

1、本实用新型实施例提供一种封装结构,包括:积体衬底,包括:衬底组件,在侧向上被绝缘包封体覆盖;重布线结构,设置于所述衬底组件及所述绝缘包封体之上;第一导电接头,将所述重布线结构耦合至所述衬底组件;及缓冲层,设置于所述重布线结构的最下部介电层上且向下延伸以覆盖所述第一导电接头中的每一者的上部部分,其中所述第一导电接头中的每一者的连接至所述上部部分的下部部分被所述绝缘包封体覆盖;以及封装组件,设置于所述重布线结构之上且电性耦合至所述重布线结构,所述封装组件包括在侧向上被包封剂覆盖的半导体晶粒。

2、本实用新型实施例提供一种封装结构,包括:积体衬底,包括:衬底组件,包括核心层、第一堆积结构及第二堆积结构,所述第一堆积结构及所述第二堆积结构设置于所述核心层的相对侧上且通过穿透所述核心层的核心穿孔彼此电性耦合;重布线结构,包括第一部分及第二部分,所述第一部分设置于所述衬底组件的所述第一堆积结构之上且电性耦合至所述衬底组件的所述第一堆积结构,所述第二部分堆栈于所述第一部分上且电性耦合至所述第一部分;第一导电接头及第二导电接头,设置于所述重布线结构的所述第一部分与所述衬底组件的所述第一堆积结构之间且电性连接至所述重布线结构的所述第一部分及所述衬底组件的所述第一堆积结构;缓冲层,设置于所述重布线结构的所述第一部分的最下部介电层上且部分地覆盖所述第一导电接头;以及绝缘包封体,介置于所述重布线结构的所述第一部分的所述最下部介电层与所述衬底组件的所述第一堆积结构之间,以覆盖所述缓冲层、所述第一导电接头及所述第二导电接头,且所述绝缘包封体沿着所述衬底组件的侧壁延伸。

技术特征:

1.一种封装结构,包括:

2.根据权利要求1所述的封装结构,其特征在于,在横截面中,所述缓冲层的厚度自所述重布线结构的所述最下部介电层与所述第一导电接头中的相应第一导电接头的所述上部部分之间的接口至所述相应第一导电接头的所述上部部分与所述下部部分之间的接口增大。

3.根据权利要求1所述的封装结构,其特征在于,所述绝缘包封体的一部分覆盖所述缓冲层,且所述缓冲层包括朝向所述绝缘包封体的所述部分凸出的弯曲外表面。

4.根据权利要求1所述的封装结构,其特征在于,覆盖所述第一导电接头中的一者的所述缓冲层的第一部分通过所述绝缘包封体与覆盖所述第一导电接头的相邻第一导电接头的所述缓冲层的第二部分分离。

5.根据权利要求1所述的封装结构,其特征在于,介置于所述第一导电接头中的相邻两个第一导电接头之间的所述缓冲层的一部分具有连接于所述第一导电接头中的所述相邻两个第一导电接头之间的相连外表面,且所述绝缘包封体与所述缓冲层的所述部分的所述相连外表面实体接触。

6.根据权利要求1所述的封装结构,其特征在于,所述衬底组件的侧壁被所述绝缘包封体覆盖,且所述绝缘包封体的侧壁与所述重布线结构的侧壁实质上对齐。

7.根据权利要求1所述的封装结构,其特征在于,所述重布线结构包括:

8.一种封装结构,包括:

9.根据权利要求8所述的封装结构,其特征在于,还包括:

10.根据权利要求8所述的封装结构,其特征在于,所述缓冲层与所述重布线结构的所述第一部分的所述最下部介电层的下表面的一部分及所述第一导电接头中的相应第一导电接头的外表面的一部分实体接触,且

技术总结

本技术提供一种封装结构。所述封装结构包括积体衬底及封装组件。积体衬底包括:衬底组件,在侧向上被绝缘包封体覆盖;重布线结构,设置于衬底组件及绝缘包封体之上;第一导电接头,将重布线结构耦合至衬底组件;以及缓冲层,设置于重布线结构的最下部介电层上且向下延伸以覆盖第一导电接头中的每一者的上部部分。第一导电接头中的每一者的连接至上部部分的下部部分被绝缘包封体覆盖。设置于重布线结构之上且电性耦合至重布线结构的封装组件包括在侧向上被包封剂覆盖的半导体晶粒。

技术研发人员:陈衿良,游济阳,梁裕民,侯皓程,郑荣伟,王宗鼎

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230707

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!