一种多芯片侧装集成封装结构及方法与流程

:本发明属于芯片封装,特别涉及一种多芯片侧装集成封装结构及方法。

背景技术

0、

背景技术:

1、3d晶圆级封装,英文简称(wlp),包括cis发射器、mems封装、标准器件封装。是指在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向叠放两个以上芯片的封装技术,它起源于快闪存储器(nor/nand)及sdram的叠层封装。主要特点包括:多功能、高效能;大容量高密度,单位体积上的功能及应用成倍提升以及低成本。

2、在尺寸和重量方面,3d设计替代单芯片封装缩小了器件尺寸、减轻了重量。与传统封装相比,使用3d技术可缩短尺寸、减轻重量达40-50倍;在速度方面,3d技术节约的功率可使3d元件以每秒更快的转换速度运转而不增加能耗等等。

3、常规的3d封装一般是垂直方向进行堆叠封装,如图1所示。垂直平铺时两颗芯片一般是相对独立的,芯片与芯片之间通过基板走线互连,并且平铺时也要求芯片与芯片之间有一定的距离,而这就导致了产品内部的空间利用率较低,对于产品小型化要求较高的电子产品,则难以满足要求。基于上述不足,本申请提出一种新的封装结构,能够节约大量互连空间,单位面积内可以集成更多的芯片,可以有效提升芯片集成度。

4、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

0、

技术实现要素:

1、本发明的目的在于提供一种多芯片侧装集成封装结构及方法,从而克服上述现有技术中的缺陷。

2、为了实现上述目的,本发明提供了一种多芯片侧装集成封装结构,包括:

3、基板;

4、主芯片,所述主芯片焊接在基板上;

5、侧装芯片,所述侧装芯片通过胶黏剂贴装在基板上,所述主芯片和侧装芯片侧面互联;

6、塑封料,所述塑封料对主芯片和侧装芯片进行封装。

7、进一步的,作为优选,所述侧装芯片至少有一层。

8、进一步的,作为优选,所述侧装芯片的侧面制作有侧面管脚,所述侧面管脚用于与主芯片互联。

9、进一步的,作为优选,所述侧装芯片的表面附有胶膜,所述胶膜用于熔融填充。

10、进一步的,作为优选,所述基板上制作有植球,所述植球用于与主芯片互联。

11、本发明还提供一种多芯片侧装集成封装方法,包括以下步骤:

12、第一步:将主芯片焊接到基板上;

13、第二步:在侧装芯片的侧面制作管脚,表面制作植球并覆盖胶膜;

14、第三步:在基板上点胶后将侧装芯片装到基板上;

15、第四步:采用回流焊的工艺将主芯片和侧装芯片互联,同时侧装芯片表面的胶膜熔融后对空隙进行填充;

16、第五步:在基板上填充塑封料,将主芯片和侧装芯片完全封装在塑封料内;

17、第六步:在基板上制作植球,植球与主芯片互联。

18、进一步的,作为优选,所述第四步侧装芯片至少有一层。

19、与现有技术相比,本发明的一个方面具有如下有益效果:

20、本发明将侧装芯片侧装在主芯片的侧面,可以提高封装体内部的利用空间,从而提升产品的集成度,可满足电子产品日趋小型化的要求。

21、附图说明:

22、图1为本发明的现有技术的垂直堆叠封装的示意图;

23、图2为本发明的实施例1将主芯片焊接到基板上的示意图;

24、图3为本发明的实施例1在侧装芯片上制作管脚、侧装植球和覆盖胶膜的示意图;

25、图4、图5为本发明的实施例1将侧装芯片装到基板上的示意图;

26、图6为本发明的实施例1将主芯片和侧装芯片互联的示意图;

27、图7为本发明的实施例1在基板上填充塑封料的示意图;

28、图8为本发明的实施例1在基板上制作植球的示意图;

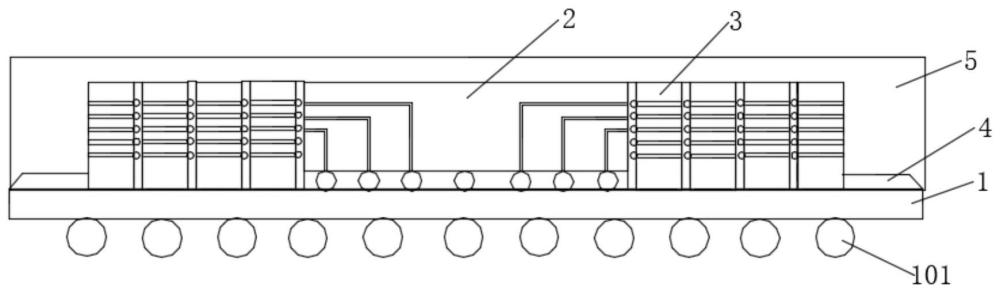

29、图9为本发明的实施例1一种多芯片侧装集成封装结构的示意图;

技术特征:

1.一种多芯片侧装集成封装结构,其特征在于,包括:

2.根据权利要求1所述的一种多芯片侧装集成封装结构,其特征在于,所述侧装芯片至少有一层。

3.根据权利要求1或2所述的一种多芯片侧装集成封装结构,其特征在于,所述侧装芯片的侧面制作有侧面管脚,所述侧面管脚用于与主芯片互联。

4.根据权利要求1或2所述的一种多芯片侧装集成封装结构,其特征在于,所述侧装芯片的表面附有胶膜,所述胶膜用于熔融填充。

5.根据权利要求1所述的一种多芯片侧装集成封装结构,其特征在于,所述基板上制作有植球,所述植球用于与主芯片互联。

6.一种多芯片侧装集成封装方法,其特征在于,包括以下步骤:

7.根据权利要求6所述的一种多芯片侧装集成封装方法,其特征在于,所述第三步侧装芯片至少有一层。

技术总结

本发明公开了一种多芯片侧装集成封装结构及方法,所述结构包括:基板;主芯片,所述主芯片焊接在基板上;侧装芯片,所述侧装芯片通过胶黏剂贴装在基板上,所述主芯片和侧装芯片侧面互联;塑封料,所述塑封料对主芯片和侧装芯片进行封装;所述方法包括以下步骤:第一步:将主芯片焊接到基板上;第二步:在侧装芯片的侧面制作管脚,表面制作植球并覆盖胶膜;第三步:在基板上点胶后将侧装芯片装到基板上;第四步:采用回流焊的工艺将主芯片和侧装芯片互联,同时侧装芯片表面的胶膜熔融后对空隙进行填充;第五步:在基板上填充塑封料,将主芯片和侧装芯片完全封装在塑封料内;第六步:在基板上制作植球,植球与主芯片互联。

技术研发人员:李鹏飞,刘卫东

受保护的技术使用者:华天科技(南京)有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!