半导体装置结构的制作方法

本技术实施例涉及半导体技术,尤其涉及半导体装置结构。

背景技术:

1、集成电路(integrated circuit,ic)产业已经历了快速成长。在集成电路材料和设计上的技术进步产生了数代集成电路,每一代都比前一代具有更小且更复杂的电路。在集成电路的发展史中,功能密度(即每一芯片区互连的装置数目)增加,同时几何尺寸(即制造过程中所产生的最小的组件或线路)缩小。此元件尺寸微缩化的工艺提供增加生产效率与降低相关费用的益处。此元件尺寸微缩化也带来了新的挑战。举例来说,已提出使用纳米线通道的晶体管,以实现增加的装置密度、更大的载子移动率及装置中的驱动电流。随着装置尺寸缩小,不断需要改善加工及制造集成电路。

技术实现思路

1、本实用新型的目的在于提出一种半导体装置结构,以解决上述至少一个问题。

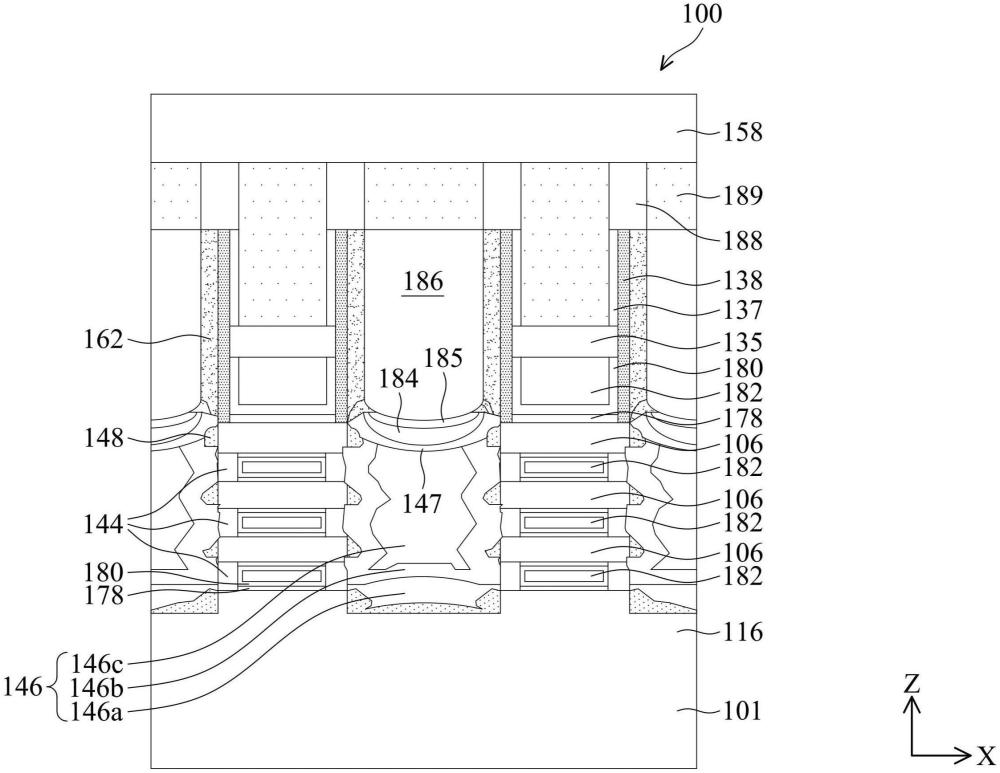

2、在一些实施例中,提供半导体装置结构,半导体装置结构包含源极/漏极外延部件,设置于基底上方,其中源极/漏极外延部件包含:第一外延层;第二外延层,接触第一外延层,第二外延层具有第一掺杂物浓度;及第三外延层,具有被第二外延层包围的侧壁,第三外延层具有大于第一掺杂物浓度的第二掺杂物浓度;源极/漏极盖层,设置于第二外延层及第三外延层之上并接触第二外延层及第三外延层,源极/漏极盖层具有大于第二掺杂物浓度的第三掺杂物浓度;以及硅化物层,设置于源极/漏极盖层之上并接触源极/漏极盖层。

3、根据本公开其中的一个实施方式,该源极/漏极外延部件位于该基底的一p型装置区,且该源极/漏极盖层为硼掺杂硅。

4、根据本公开其中的一个实施方式,该源极/漏极盖层具有硼原子百分比在约4at.%至约15at.%的范围中。

5、根据本公开其中的一个实施方式,该第三外延层为具有一第一硼浓度的硼掺杂硅锗,且该源极/漏极盖层具有比该第一硼浓度更大约10%至约30%的一第二硼浓度。

6、根据本公开其中的一个实施方式,该源极/漏极盖层还包括锗掺杂物。

7、根据本公开其中的一个实施方式,该源极/漏极盖层具有一第一锗浓度,且该第三外延层具有大于该第一锗浓度的一第二锗浓度。

8、根据本公开其中的一个实施方式,该硅化物层包括锗掺杂物,且该硅化物层具有小于该第一锗浓度的一第三锗浓度。

9、根据本公开其中的一个实施方式,接触该第一外延层的该第二外延层的底部具有一第一宽度,且接触该第三外延层的该源极/漏极盖层的底部小于该第一宽度的一第二宽度。

10、在一些实施例中,提供半导体装置结构,半导体装置结构包含两个或更多个半导体层,垂直堆叠于基底上方;栅极电极层,围绕两个或更多个半导体层的其中一者的一部分;源极/漏极外延部件,设置于基底上方,并相邻于两个或更多个半导体层,源极/漏极外延部件包含:第一外延层,设置于基底上方;及第二外延层,具有接触第一外延层的至少三个表面,第二外延层具有第一掺杂物浓度;以及源极/漏极盖层,设置于第一外延层及第二外延层之上并接触第一外延层及第二外延层,源极/漏极盖层具有大于第一掺杂物浓度的第二掺杂物浓度,源极/漏极盖层接触第二外延层的第一侧面的部分定义第一界面,源极/漏极盖层接触第二外延层的第二侧面的部分定义第二界面,其中第一界面沿第一方向延伸,第二界面沿第二方向延伸,且第一方向相对于第二方向形成角度小于约90度。

11、根据本公开其中的一个实施方式,还包括:一刻面结构,设置于该源极/漏极盖层与该两个或更多个半导体层的一最顶部半导体层之间,并接触该源极/漏极盖层及该两个或更多个半导体层的该最顶部半导体层。

技术特征:

1.一种半导体装置结构,其特征在于,包括:

2.如权利要求1所述的半导体装置结构,其特征在于,该源极/漏极外延部件位于该基底的一p型装置区,且该源极/漏极盖层为硼掺杂硅。

3.如权利要求2所述的半导体装置结构,其特征在于,该源极/漏极盖层具有硼原子百分比在约4at.%至约15at.%的范围中。

4.如权利要求3所述的半导体装置结构,其特征在于,该第三外延层为具有一第一硼浓度的硼掺杂硅锗,且该源极/漏极盖层具有比该第一硼浓度更大10%至30%的一第二硼浓度。

5.如权利要求4所述的半导体装置结构,其特征在于,该源极/漏极盖层还包括锗掺杂物。

6.如权利要求5所述的半导体装置结构,其特征在于,该源极/漏极盖层具有一第一锗浓度,且该第三外延层具有大于该第一锗浓度的一第二锗浓度。

7.如权利要求6所述的半导体装置结构,其特征在于,该硅化物层包括锗掺杂物,且该硅化物层具有小于该第一锗浓度的一第三锗浓度。

8.如权利要求1至7中任一项所述的半导体装置结构,其特征在于,接触该第一外延层的该第二外延层的底部具有一第一宽度,且接触该第三外延层的该源极/漏极盖层的底部小于该第一宽度的一第二宽度。

9.一种半导体装置结构,其特征在于,包括:

10.如权利要求9所述的半导体装置结构,其特征在于,还包括:

技术总结

一种半导体装置结构,包含源极/漏极外延部件,设置于基底上方,其中源极/漏极外延部件包括:第一外延层;第二外延层,接触第一外延层,其中第二外延层具有第一掺杂物浓度;及第三外延层,具有被第二外延层包围的侧壁,其中第三外延层具有大于第一掺杂物浓度的第二掺杂物浓度。半导体装置结构也包含源极/漏极盖层,设置于第二外延层及第三外延层之上并接触第二外延层及第三外延层,其中源极/漏极盖层具有大于第二掺杂物浓度的第三掺杂物浓度;以及硅化物层,设置于源极/漏极盖层之上并接触源极/漏极盖层。

技术研发人员:张正伟,沙哈吉·B·摩尔,梁顺鑫,王菘豊,刘奕莹

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230810

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!