具有空间调制缓冲结构的SiCMOSFET元胞结构、器件及制备方法与流程

本发明涉及半导体器件,尤其涉及一种具有空间调制缓冲结构的sicmosfet元胞结构、器件及制备方法。

背景技术:

1、碳化硅是一种第三代半导体材料,与第一代半导体材料硅相比,具有较大的禁带宽度、较大的临界击穿场强、较快的电子饱和漂移速度、较高的热导率。因此,碳化硅功率半导体器件,特别是碳化硅mosfet,可以更好地工作在高温、高压、高频条件下,显著提升电力电子系统的能量效率,改善系统散热,缩减系统体积。

2、碳化硅mosfet面临的一个关键挑战是在碳化硅/二氧化硅界面处存在界面态和陷阱电荷对电子的散射效应,导致沟道迁移率较低,导通电阻较大,对此,采用沟槽型碳化硅mosfet结构可以消除平面型碳化硅mosfet结构的jfet区域电阻,并可以在另一晶向提高沟道迁移率,还可以减小元胞尺寸、增大元胞密度,共同促进导通电阻减小。但沟槽型碳化硅mosfet结构的栅极沟槽底部存在电场集中效应,导致临界击穿电压降低,栅极介质层存在可靠性问题。

3、双沟槽型碳化硅mosfet结构可以较好地实现临界击穿电压和导通电阻之间的折衷,但栅极沟槽底部中间位置的电场集中效应依然较严重,且栅漏电容较高,限制了工作频率和系统效率的提高。

技术实现思路

1、本发明意在提供一种具有空间调制缓冲结构的sic mosfet元胞结构、器件及制备方法,以解决现有技术中存在的不足,本发明要解决的技术问题通过以下技术方案来实现。

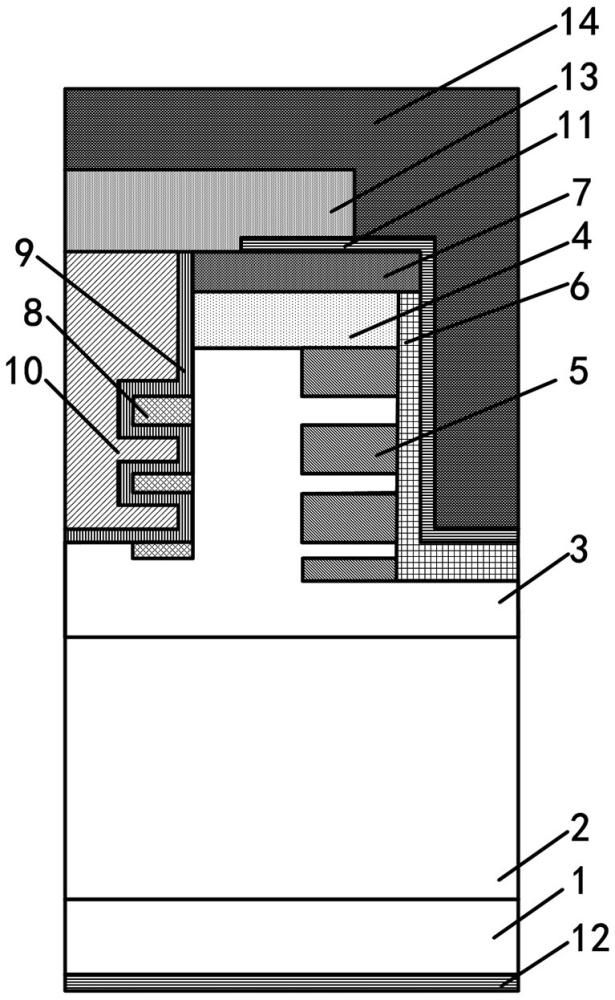

2、本发明提供的具有空间调制缓冲结构的sic mosfet元胞结构包括n+型sic衬底、依次设置在n+型sic衬底上方的n-型外延层和n型外延层、分别位于n型外延层上方左右两侧位置处的栅极沟槽和源极沟槽,栅极沟槽具有部分向内凸起的侧壁;

3、在栅极沟槽和源极沟槽之间具有n++型源区;

4、在n++型源区的右侧下方具有包裹源极沟槽底部以及裸露侧壁的p+型源极沟槽屏蔽层;

5、在n++型源区的下方以及栅极沟槽与p+型源极沟槽屏蔽层之间具有p型基区;

6、在p型基区下方且靠近p+型源极沟槽屏蔽层左侧具有设定宽度和间距的多个p+型源极沟槽互补屏蔽环;

7、在栅极沟槽侧壁外部以及底部下方具有多个p+型沟槽侧壁空间调制缓冲结构填充层;

8、在栅极沟槽的底部和内侧壁上覆盖有栅氧化层。

9、在上述的方案中,多个p+型沟槽侧壁空间调制缓冲结构填充层中各个p+型沟槽侧壁空间调制缓冲结构填充层的厚度与多个p+型源极沟槽互补屏蔽环中各个p+型源极沟槽互补屏蔽环之间的间距一一对应。

10、在上述的方案中,多个p+型沟槽侧壁空间调制缓冲结构填充层中各个p+型沟槽侧壁空间调制缓冲结构填充层的厚度均不小于0.2μm。

11、在上述的方案中,多个p+型沟槽侧壁空间调制缓冲结构填充层中各个p+型沟槽侧壁空间调制缓冲结构填充层的宽度相同且小于元胞结构中栅极沟槽宽度的80%。

12、在上述的方案中,多个p+型沟槽侧壁空间调制缓冲结构填充层中各个p+型沟槽侧壁空间调制缓冲结构填充层之间的间距均不小于0.2μm。

13、在上述的方案中,多个p+型沟槽侧壁空间调制缓冲结构填充层的最上方与所述p型基区的底部之间的间距不小于0.1μm。

14、在上述的方案中,n型外延层的掺杂浓度至少是n-型外延层的掺杂浓度的5倍,且n型外延层的底部比多个p+型源极沟槽互补屏蔽环的底部至少低0.5μm。

15、在上述的方案中,多个p+型源极沟槽互补屏蔽环的最上方与所述p型基区的底部平齐,多个p+型源极沟槽互补屏蔽环的最下方与所述p+型源极沟槽屏蔽层的底部平齐,多个p+型源极沟槽互补屏蔽环中各个p+型源极沟槽互补屏蔽环的宽度相同,且多个p+型源极沟槽互补屏蔽环与所述栅极沟槽的间距不小于0.2μm。

16、本发明提供的具有空间调制缓冲结构的sic mosfet器件,包括如上所述的具有空间调制缓冲结构的sic mosfet元胞结构。

17、本发明提供一种如上所述的具有空间调制缓冲结构的sic mosfet元胞结构的制备方法,包括:

18、提供一n+型sic衬底,并在所述n+型sic衬底上方依次形成n-型外延层和n型外延层;

19、在所述n型外延层中制备出p型基区,并在所述p型基区右侧的下方位置的n型外延层中制备出具有设定宽度和间距的多个p+型源极沟槽互补屏蔽环;

20、在所述p型基区右侧、p型基区右侧下方位置的n型外延层以及p型基区右侧下方位置的n型外延层中的多个p+型源极沟槽互补屏蔽环中制备出p+型源极沟槽屏蔽层,在所述p型基区以及p+型源极沟槽屏蔽层中制备出n++型源区;

21、对所述n++型源区的右侧及其下方的p+型源极沟槽屏蔽层进行部分刻蚀,形成源极沟槽,对所述n++型源区的左侧、所述n++型源区的左侧下方的p型基区以及部分n型外延层进行刻蚀,形成初级栅极沟槽;

22、采用局部刻蚀法,在初级栅极沟槽的侧壁进行横向刻蚀,形成具有部分向内凸起的侧壁的栅极沟槽;

23、在具有部分向内凸起的侧壁的栅极沟槽的侧壁外部以及底部下方形成p+型沟槽侧壁空间调制缓冲结构填充层;

24、在具有部分向内凸起的侧壁的栅极沟槽的底部和内侧壁上形成栅氧化层。

25、本发明实施例包括以下优点:

26、本发明实施例提供的具有空间调制缓冲结构的sic mosfet元胞结构、器件及制备方法,通过采用靠近n+型sic衬底、掺杂浓度较低的n-型外延层,以及设置在n-型外延层上方的掺杂浓度较高的n型外延层,可在确保sic mosfet器件有足够阻断电压的同时在沟道附近提供更高浓度的导电电子,降低器件导通电阻,优化综合特性;通过在栅极沟槽侧壁外部以及底部下方设置多个p+型沟槽侧壁空间调制缓冲结构填充层,通过在栅极沟槽的底部和内侧壁上覆盖栅氧化层,在sicmosfet器件的垂直承压方向上,人为制造多个栅氧化层的拐角,每个拐角处都存在电场集中效应,从而可以将栅氧化层中的电场峰值点从一个增加到多个,降低每个点的电场大小并且让整体电场分布更加均匀,优化高压下栅氧化层中的应力,从而延长sic mosfet器件的使用寿命;通过在栅极沟槽侧壁外部以及底部下方设置多个p+型沟槽侧壁空间调制缓冲结构填充层,在各个栅氧化层的拐角处实现对漏电压的屏蔽,可以进一步降低栅氧化层中的电场峰值从而提升器件可靠性;通过在p型基区下方且靠近p+型源极沟槽屏蔽层左侧设置多个p+型源极沟槽互补屏蔽环,且多个p+型沟槽侧壁空间调制缓冲结构填充层中各个p+型沟槽侧壁空间调制缓冲结构填充层的厚度与多个p+型源极沟槽互补屏蔽环中各个p+型源极沟槽互补屏蔽环之间的间距一一对应,加强对栅氧化层中没有被多个p+型沟槽侧壁空间调制缓冲结构填充层进行屏蔽的薄弱区的保护,并降低了栅极寄生电容;通过多个p+型沟槽侧壁空间调制缓冲结构填充层与多个p+型源极沟槽互补屏蔽环之间的互补效果可以减缓对电流通道的压缩,提升保护的效率,同时多个p+型源极沟槽互补屏蔽环通过p+型源极沟槽屏蔽层与源极欧姆接触电极相连,可以实现在开关过程中有更快的空间电荷区响应速度,从而优化器件综合性能;在短路条件下,多个p+型源极沟槽互补屏蔽环和多个p+型沟槽侧壁空间调制缓冲结构填充层空间电荷区的连接可以夹断电流通道,降低sic mosfet器件的饱和电流,避免了高瞬时功率损坏器件。

- 还没有人留言评论。精彩留言会获得点赞!