LDMOS器件的制作方法

本申请涉及半导体集成电路制造,具体涉及一种ldmos器件。

背景技术:

1、横向扩散金属氧化物半导体(ldmos,laterally diffused metal oxidesemiconductor)是一种常用的功率场效应晶体管机构,其原理是在功率器件的表面形成一个侧向扩散的掺杂区,该侧向扩散的结构增加了器件的电流承载能力,降低器件电阻,从而提高功率放大效果。

2、但是当ldmos器件在高的漏端电压和栅端电压下工作时,ldmos器件沟道内会产生较大的电场,尤其是在靠近漏端的沟道内较大的纵向电场使得载流子获得较高能量,成为热载流子,进而引发器件的热载流子效应,导致器件的阈值电压、饱和电流等电学特性发生退化,影响器件的可靠性,最终导致器件失效。

技术实现思路

1、本申请提供了一种ldmos器件,可以解决相关技术中存在靠近漏端存在热载流子效应的问题。

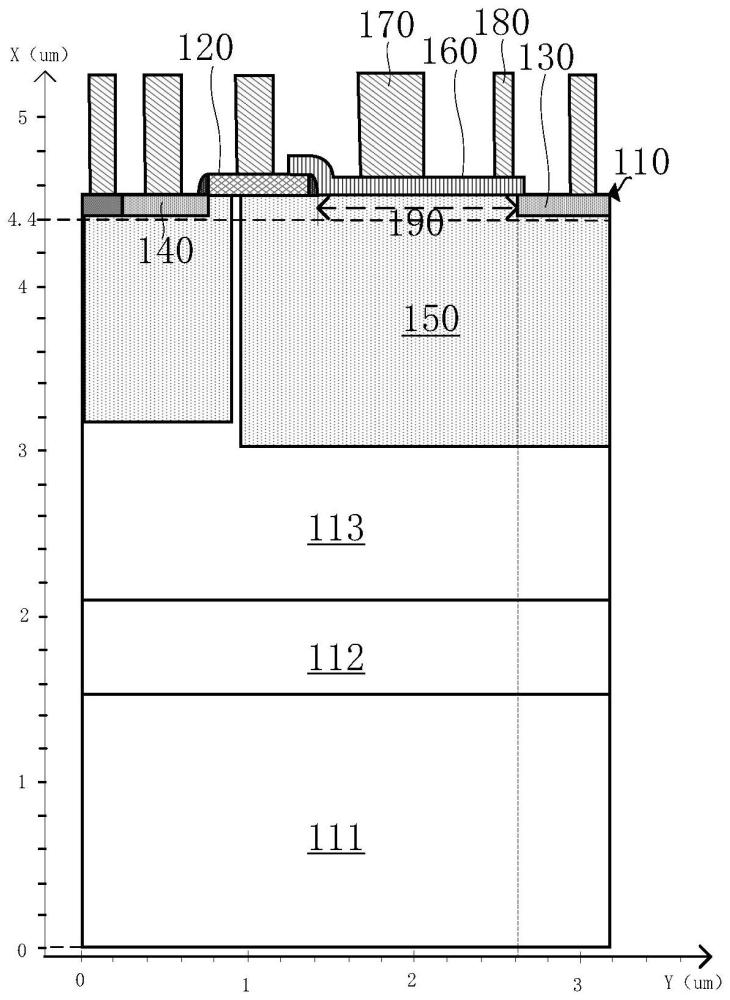

2、为了解决背景技术中所述的技术问题,本申请提供一种ldmos器件,所述ldmos器件包括:

3、基底层;

4、栅极结构,所述栅极结构形成于所述基底层上;

5、漏端掺杂区,所述漏端掺杂区形成于所述栅极结构一侧的基底层中,且所述漏端掺杂区与所述栅极结构之间形成间隔区;

6、源端掺杂区,所述源端掺杂区形成于所述栅极结构另一侧的基底层中;

7、漂移区,所述漂移区形成于所述栅极结构与所述漏端掺杂区之间的基底层中,且所述漏端掺杂区位于所述漂移区中,所述漂移区与所述栅极结构的部分交叠;

8、金属硅化物阻挡层,所述金属硅化物阻挡层跨接所述栅极结构和所述漏端掺杂区,且所述金属硅化物阻挡层至少覆盖在所述间隔区位置处的基底层上;

9、源端接触孔式场板,所述源端接触孔式场板靠近所述栅极结构的一侧设置,且所述源端接触孔式场板的下端与所述金属硅化物阻挡层接触;

10、漏端接触孔式场板,所述漏端接触孔式场板靠近所述漏端掺杂区的一侧设置,且所述漏端接触孔式场板的下端与所述金属硅化物阻挡层接触;其中,远离所述漏端掺杂区的漏端接触孔式场板一端边缘在横向上的位置为:位于所述漏端掺杂区外的所述漂移区中。

11、可选地,漏端接触孔式场板第一边缘与漏端掺杂区第一边缘上下对齐;

12、其中,所述漏端接触孔式场板第一边缘为所述漏端接触孔式场板靠近所述漏端掺杂区的边缘,所述漏端掺杂区第一边缘为所述漏端掺杂区靠近所述漏端接触孔式场板的边缘。

13、可选地,所述漏端接触孔式场板与所述漏端掺杂区之间相间隔;

14、其中,所述漏端接触孔式场板第一边缘为所述漏端接触孔式场板靠近所述漏端掺杂区的边缘,所述漏端掺杂区第一边缘为所述漏端掺杂区靠近所述漏端接触孔式场板的边缘。

15、可选地,所述漏端接触孔式场板与所述漏端掺杂区之间相交叠;

16、其中,所述漏端接触孔式场板第一边缘为所述漏端接触孔式场板靠近所述漏端掺杂区的边缘,所述漏端掺杂区第一边缘为所述漏端掺杂区靠近所述漏端接触孔式场板的边缘。

17、可选地,所述源端接触孔式场板与所述源端掺杂区短接。

18、可选地,所述漏端接触孔式场板与所述漏端掺杂区短接。

19、可选地,所述漏端掺杂区第一边缘的电场强度为3.27v/cm;

20、所述漏端掺杂区第一边缘为所述漏端掺杂区靠近所述漏端接触孔式场板的边缘。

21、本申请技术方案,至少包括如下优点:本实施例提供的ldmos器件,其靠近所述漏端掺杂区一侧设置的漏端接触孔式场板,其远离所述漏端掺杂区的漏端接触孔式场板一端边缘在横向上的位置为:位于所述漏端掺杂区外的所述漂移区中,从而能够改善器件靠近漏端掺杂区的表面电场分布,降低漏端掺杂区周围的电场强度、降低isub特性曲线第一峰后器件中的衬底电流,进而降低器件热载流子注入(hci)效应。

技术特征:

1.一种ldmos器件,其特征在于,所述ldmos器件包括:

2.如权利要求1所述的ldmos器件,其特征在于,漏端接触孔式场板第一边缘与漏端掺杂区第一边缘上下对齐;

3.如权利要求1所述的ldmos器件,其特征在于,所述漏端接触孔式场板与所述漏端掺杂区之间相间隔;

4.如权利要求1所述的ldmos器件,其特征在于,所述漏端接触孔式场板与所述漏端掺杂区之间相交叠;

5.如权利要求1所述的ldmos器件,其特征在于,所述源端接触孔式场板与所述源端掺杂区短接。

6.如权利要求1所述的ldmos器件,其特征在于,所述漏端接触孔式场板与所述漏端掺杂区短接。

7.如权利要求1所述的ldmos器件,其特征在于,所述漏端掺杂区第一边缘的电场强度为3.27v/cm;

技术总结

本申请涉及半导体集成电路制造技术领域,具体涉及一种LDMOS器件。包括:栅极结构形成于基底层上;漏端掺杂区形成于栅极结构一侧的基底层中,且漏端掺杂区与栅极结构之间形成间隔区;源端掺杂区形成于栅极结构另一侧的基底层中;漂移区形成于栅极结构与漏端掺杂区之间的基底层中,且漏端掺杂区位于漂移区中,漂移区与栅极结构的部分交叠;金属硅化物阻挡层跨接栅极结构和漏端掺杂区,且金属硅化物阻挡层至少覆盖在间隔区位置处的基底层上;源端接触孔式场板靠近栅极结构的一侧设置,且源端接触孔式场板的下端与金属硅化物阻挡层接触;漏端接触孔式场板靠近漏端掺杂区的一侧设置,且漏端接触孔式场板的下端与金属硅化物阻挡层接触。

技术研发人员:田甜,许昭昭,方明旭

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!