一种氮化镓器件的制作方法

本发明涉及半导体,尤其涉及一种氮化镓器件。

背景技术:

1、如图1所示,图1是现有技术提供的一种氮化镓器件的结构示意图,现有技术中经常采用碳原子掺杂的ⅲ-ⅴ族半导体层作为缓冲层,但是在通过mocvd工艺(mocvd是在气相外延生长(vpe)的基础上发展起来的一种新型气相外延生长技术)生长缓冲层、沟道层、势垒层和p型氮化物层的过程中,附着在腔体表面的碳原子掺杂的ⅲ-ⅴ族半导体层会脱落在沟道层、势垒层和p型氮化物层的表面,从而影响了沟道层、势垒层和p型氮化物层的良率,进而影响了氮化镓器件的电学性能的稳定性。其中,图1中的附图标记如下:100-衬底,101-缓冲层,102-沟道层,103-势垒层,104-p型氮化物层,105-栅极,106-源极,107-漏极。

技术实现思路

1、本发明提供了一种氮化镓器件,以提高沟道层、势垒层和p型氮化物层的良率,提升氮化镓器件的电学性能的稳定性。

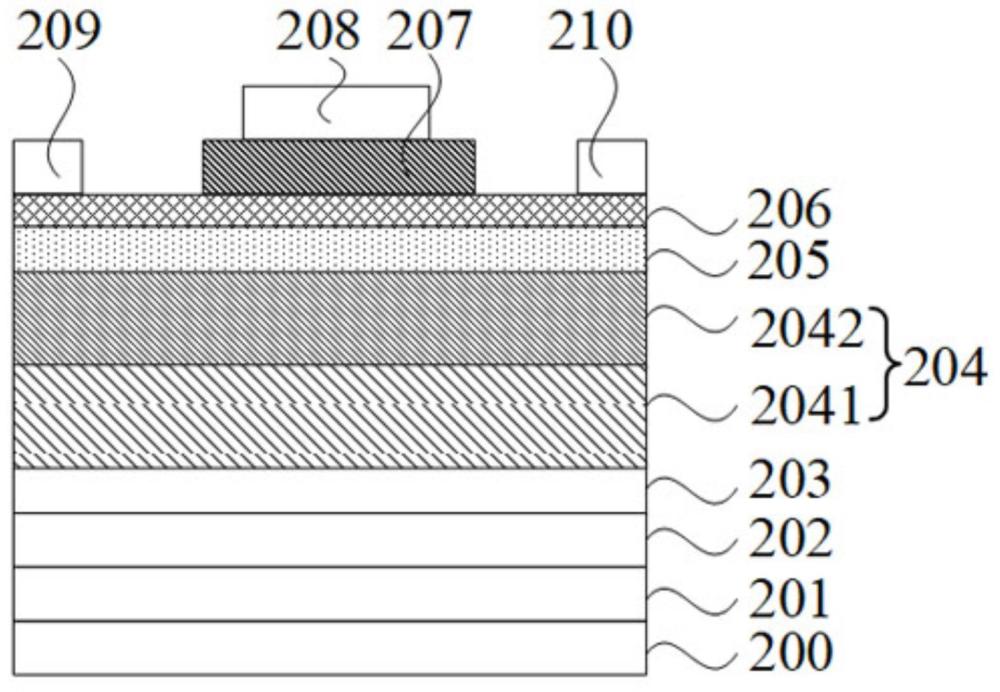

2、根据本发明的一方面,提供了一种氮化镓器件,包括:衬底;缓冲层,所述缓冲层位于所述衬底之上;沟道层,所述沟道层位于所述缓冲层远离所述衬底的表面;所述缓冲层包括相对设置的第一表面和第二表面, 所述缓冲层的第一表面为靠近所述衬底的表面,所述缓冲层的第二表面为所述缓冲层和所述沟道层接触的表面,所述缓冲层的第二表面侧的材料至少包括铝原子掺杂的ⅲ-ⅴ族半导体材料,其中,所述铝原子和第ⅲ主族原子的比值大于或等于2%,且小于或等于5%,所述缓冲层的第一表面侧的材料至少包括碳原子掺杂的ⅲ-ⅴ族半导体材料;所述缓冲层包括一层或者多个子层;势垒层,所述势垒层位于所述沟道层远离所述缓冲层的表面;p型氮化物层,所述p型氮化物层位于所述势垒层远离所述沟道层的表面;栅极,所述栅极位于所述p型氮化物层远离所述势垒层的表面;源极,所述源极位于所述势垒层远离所述沟道层的表面;漏极,所述漏极位于所述势垒层远离所述沟道层的表面。

3、可选地,所述缓冲层包括两个子层,所述缓冲层包括碳原子掺杂的ⅲ-ⅴ族半导体层和铝原子掺杂的ⅲ-ⅴ族半导体层的叠层;所述碳原子掺杂的ⅲ-ⅴ族半导体层位于所述衬底之上;所述碳原子掺杂的ⅲ-ⅴ族半导体层的表面和内部均包括掺杂有碳原子的ⅲ-ⅴ族半导体材料;所述铝原子掺杂的ⅲ-ⅴ族半导体层位于所述碳原子掺杂的ⅲ-ⅴ族半导体层远离所述衬底的表面,且和所述沟道层接触;所述铝原子掺杂的ⅲ-ⅴ族半导体层的表面和内部均包括掺杂有铝原子的ⅲ-ⅴ族半导体材料。

4、可选地,所述碳原子掺杂的ⅲ-ⅴ族半导体层包括碳原子掺杂的氮化镓层。

5、可选地,所述碳原子掺杂的ⅲ-ⅴ族半导体层包括碳原子掺杂的氮化镓铝层。

6、可选地,所述碳原子掺杂的氮化镓铝层中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

7、可选地,所述铝原子掺杂的ⅲ-ⅴ族半导体层包括铝原子掺杂的氮化镓层。

8、可选地,所述缓冲层包括一层,所述缓冲层的第二表面侧的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料,所述缓冲层的第一表面侧的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料;其中,所述缓冲层的第一表面侧的材料中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

9、可选地,所述缓冲层位于第一表面侧和第二表面侧之间的材料为所述缓冲层内部的材料,所述缓冲层内部的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料,所述缓冲层内部的材料中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

10、可选地,所述缓冲层包括碳原子和铝原子掺杂的氮化镓层,所述碳原子和铝原子掺杂的氮化镓层的表面和内部均包括掺杂有碳原子和铝原子的氮化镓材料。

11、可选地,所述衬底包括硅衬底或者氮化硅衬底。

12、本发明实施例提供的技术方案,缓冲层包括相对设置的第一表面和第二表面,缓冲层的第一表面为靠近衬底的表面,缓冲层的第二表面为缓冲层和沟道层接触的表面,缓冲层的第二表面侧的材料至少包括铝原子掺杂的ⅲ-ⅴ族半导体材料,其中,铝原子和第ⅲ主族原子的比值大于或等于2%,且小于或等于5%,缓冲层的第一表面侧的材料至少包括碳原子掺杂的ⅲ-ⅴ族半导体材料。因此,在通过mocvd工艺制备缓冲层的过程中,先形成缓冲层的第一表面侧的材料,然后再形成缓冲层的第二表面侧的材料。在通过mocvd工艺生长沟道层、势垒层和p型氮化物层的过程中,附着在腔体表面的膜层包括缓冲层的第一表面侧的材料和缓冲层的第二表面侧的材料,且缓冲层的第一表面侧的材料位于腔体表面和缓冲层的第二表面侧的材料之间,而至少包括铝原子掺杂的ⅲ-ⅴ族半导体材料的缓冲层的第二表面侧的材料不容易从腔体表面脱落,其中,铝原子和第ⅲ主族原子的比值大于或等于2%,且小于或等于5%。由于在通过mocvd工艺生长沟道层、势垒层和p型氮化物层的过程中,覆盖腔体最上层表面的材料是不容易从腔体表面脱落的膜层,可以有效避免有膜层会脱落在沟道层、势垒层和p型氮化物层的表面,从而提高了沟道层、势垒层和p型氮化物层的良率,进而提升了氮化镓器件的电学性能的稳定性。

13、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种氮化镓器件,其特征在于,包括:

2.根据权利要求1所述的氮化镓器件,其特征在于,所述缓冲层包括两个子层,所述缓冲层包括碳原子掺杂的ⅲ-ⅴ族半导体层和铝原子掺杂的ⅲ-ⅴ族半导体层的叠层;

3.根据权利要求2所述的氮化镓器件,其特征在于,所述碳原子掺杂的ⅲ-ⅴ族半导体层包括碳原子掺杂的氮化镓层。

4.根据权利要求2所述的氮化镓器件,其特征在于,所述碳原子掺杂的ⅲ-ⅴ族半导体层包括碳原子掺杂的氮化镓铝层。

5.根据权利要求4所述的氮化镓器件,其特征在于,所述碳原子掺杂的氮化镓铝层中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

6.根据权利要求2所述的氮化镓器件,其特征在于,所述铝原子掺杂的ⅲ-ⅴ族半导体层包括铝原子掺杂的氮化镓层。

7.根据权利要求1所述的氮化镓器件,其特征在于,所述缓冲层包括一层,所述缓冲层的第二表面侧的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料,所述缓冲层的第一表面侧的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料;其中,所述缓冲层的第一表面侧的材料中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

8.根据权利要求7所述的氮化镓器件,其特征在于,所述缓冲层位于第一表面侧和第二表面侧之间的材料为所述缓冲层内部的材料,所述缓冲层内部的材料包括碳原子和铝原子掺杂的ⅲ-ⅴ族半导体材料,所述缓冲层内部的材料中,所述铝原子和第ⅲ主族原子的比值大于或等于大于或等于2%,且小于或等于5%。

9.根据权利要求8所述的氮化镓器件,其特征在于,所述缓冲层包括碳原子和铝原子掺杂的氮化镓层,所述碳原子和铝原子掺杂的氮化镓层的表面和内部均包括掺杂有碳原子和铝原子的氮化镓材料。

10.根据权利要求1所述的氮化镓器件,其特征在于,所述衬底包括硅衬底或者氮化硅衬底。

技术总结

本发明公开了一种氮化镓器件。该氮化镓器件包括:衬底;缓冲层位于衬底之上;沟道层,沟道层位于缓冲层远离衬底的表面;缓冲层的第一表面为靠近衬底的表面,缓冲层的第二表面为缓冲层和沟道层接触的表面,缓冲层的第二表面侧的材料至少包括铝原子掺杂的Ⅲ‑Ⅴ族半导体材料,铝原子和第Ⅲ主族原子的比值大于或等于2%,且小于或等于5%,缓冲层的第一表面侧的材料至少包括碳原子掺杂的Ⅲ‑Ⅴ族半导体材料;缓冲层包括一层或者多个子层;势垒层位于沟道层远离缓冲层的表面;P型氮化物层位于势垒层远离沟道层的表面。本发明实施例提供的技术方案提高了沟道层、势垒层和P型氮化物层的良率,提升了氮化镓器件的电学性能的稳定性。

技术研发人员:汪可,李啓珍

受保护的技术使用者:英诺赛科(珠海)科技有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!