一种LED芯片及其制备方法与流程

本发明涉及半导体,特别涉及一种led芯片及其制备方法。

背景技术:

1、高压led芯片因为iso隔离槽较深,在进行tcl光刻时,需要使用较大的曝光量,以使沟槽处的光刻胶显影干净,但是较大的曝光量会使非沟槽处的光刻胶过曝,实际线宽与设计线宽相差较多,使得tcl距离mesa较远,浪费一部分发光面积。

2、具体的,常规制作高压led的流程为:1、mesa,去除部分p型半导体及发光层,裸露出n型半导体;2、iso,制作隔离槽;3、cbl,制作电流阻挡层;4、tcl,制作透明导电层;5、pad,蒸镀电极;6、psv,保护层制作。其中,mesa与tcl分为两道光刻,设计要求为两道光刻预留3μm~7μm距离,以保证二者的安全距离,芯粒不会漏电、短路等失效,同时,因为高压iso槽的原因,需要使用较大的曝光量,使非沟槽处的光刻胶过曝,实际线宽与设计线宽相差2μm~5μm,导致最终mesa与tcl的实际距离在5μm~12μm。

技术实现思路

1、基于此,本发明的目的是提供一种led芯片及其制备方法,旨在控制mesa与tcl的实际距离,避免在制作过程中浪费发光面积,导致发光效率达不到最佳。

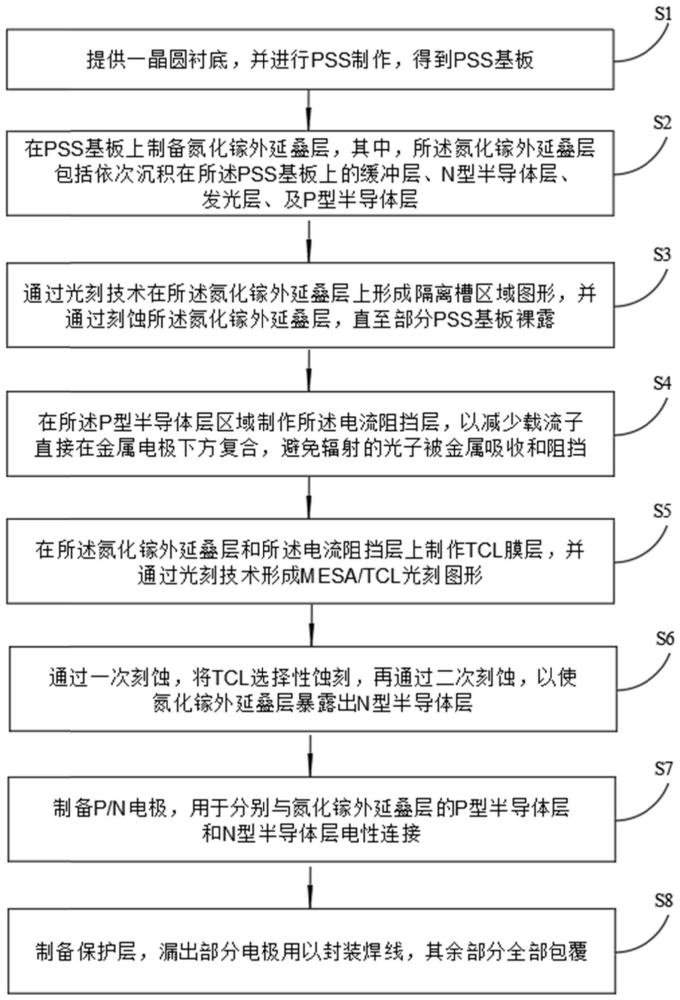

2、根据本发明实施例当中的一种led芯片制备方法,所述方法包括:

3、提供一半成品led芯片,所述半成品led芯片包括pss基板,以及依次沉积在所述pss基板上的氮化镓外延叠层和电流阻挡层;

4、在所述氮化镓外延叠层和所述电流阻挡层上制作tcl膜层,并通过光刻技术形成mesa/tcl光刻图形;

5、通过湿法刻蚀,将tcl选择性蚀刻,再通过干法刻蚀,以使氮化镓外延叠层暴露出n型半导体层;

6、制备p/n电极,用于分别与氮化镓外延叠层的p型半导体层和n型半导体层电性连接;

7、制备保护层,漏出部分电极用以封装焊线,其余部分全部包覆。

8、进一步的,所述提供一半成品led芯片,所述半成品led芯片包括pss基板,以及依次沉积在所述pss基板上的氮化镓外延叠层和电流阻挡层的步骤包括:

9、提供一晶圆衬底,并进行pss制作,得到pss基板;

10、在pss基板上制备氮化镓外延叠层,其中,所述氮化镓外延叠层包括依次沉积在所述pss基板上的缓冲层、n型半导体层、发光层、及p型半导体层;

11、通过光刻技术在所述氮化镓外延叠层上形成隔离槽区域图形,并通过刻蚀所述氮化镓外延叠层,直至部分pss基板裸露;

12、在所述p型半导体层区域制作所述电流阻挡层,以减少载流子直接在金属电极下方复合,避免辐射的光子被金属吸收和阻挡。

13、进一步的,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,mesa与tcl的实际距离为3μm~5μm。

14、进一步的,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,实际刻蚀的tcl与tcl设计图形相比,间距为0μm~1μm。

15、进一步的,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,实际刻蚀的mesa与mesa设计图形相比,间距为1μm~3μm。

16、进一步的,电流阻挡层的材料为sio2,电流阻挡层的厚度为150nm~420nm。

17、进一步的,tcl膜层的材料为铟锡氧化物或铟锌氧化物中的一种,tcl膜层的厚度为25nm~150nm。

18、进一步的,所述一次刻蚀为湿法刻蚀,所述二次刻蚀为干法刻蚀。

19、根据本发明实施例当中的一种led芯片,根据上述的led芯片制备方法制备得到。

20、进一步的,mesa与tcl的实际距离为3μm~5μm。

21、本发明实施例提供的一种led芯片及其制备方法,该方法包括提供一半成品led芯片,半成品led芯片包括pss基板,以及依次沉积在pss基板上的氮化镓外延叠层和电流阻挡层;在氮化镓外延叠层和电流阻挡层上制作tcl膜层,并通过光刻技术形成mesa/tcl光刻图形;通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层;制备p/n电极,用于分别与氮化镓外延叠层的p型半导体层和n型半导体层电性连接;制备保护层,漏出部分电极用以封装焊线,其余部分全部包覆,具体的,将mesa与tcl两道工序的光刻合为一道,可以更好地控制二者的距离,大大增加了发光面积,有效提高芯片光效,还可以减少制作步骤,提高产能。

技术特征:

1.一种led芯片制备方法,其特征在于,所述方法包括:

2.根据权利要求1所述的led芯片制备方法,其特征在于,所述提供一半成品led芯片,所述半成品led芯片包括pss基板,以及依次沉积在所述pss基板上的氮化镓外延叠层和电流阻挡层的步骤包括:

3.根据权利要求2所述的led芯片制备方法,其特征在于,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,mesa与tcl的实际距离为3μm~5μm。

4.根据权利要求3所述的led芯片制备方法,其特征在于,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,实际刻蚀的tcl与tcl设计图形相比,间距为0μm~1μm。

5.根据权利要求4所述的led芯片制备方法,其特征在于,所述通过一次刻蚀,将tcl选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出n型半导体层的步骤中,实际刻蚀的mesa与mesa设计图形相比,间距为1μm~3μm。

6.根据权利要求5所述的led芯片制备方法,其特征在于,电流阻挡层的材料为sio2,电流阻挡层的厚度为150nm~420nm。

7.根据权利要求6所述的led芯片制备方法,其特征在于,tcl膜层的材料为铟锡氧化物或铟锌氧化物中的一种,tcl膜层的厚度为25nm~150nm。

8.根据权利要求1所述的led芯片制备方法,其特征在于,所述一次刻蚀为湿法刻蚀,所述二次刻蚀为干法刻蚀。

9.一种led芯片,其特征在于,根据权利要求1至8中任一项所述的led芯片制备方法制备得到。

10.根据权利要求9所述的led芯片,其特征在于,mesa与tcl的实际距离为3μm~5μm。

技术总结

本发明提供一种LED芯片及其制备方法,该方法包括提供一半成品LED芯片,半成品LED芯片包括PSS基板,以及依次沉积在PSS基板上的氮化镓外延叠层和电流阻挡层;在氮化镓外延叠层和电流阻挡层上制作TCL膜层,并通过光刻技术形成MESA/TCL光刻图形;通过一次刻蚀,将TCL选择性蚀刻,再通过二次刻蚀,以使氮化镓外延叠层暴露出N型半导体层;制备P/N电极,用于分别与氮化镓外延叠层的P型半导体层和N型半导体层电性连接;制备保护层,漏出部分电极用以封装焊线,其余部分全部包覆,具体的,将MESA与TCL两道工序的光刻合为一道,可以更好地控制二者的距离,大大增加了发光面积,有效提高芯片光效。

技术研发人员:张亚,张星星,林潇雄,胡加辉,金从龙

受保护的技术使用者:江西兆驰半导体有限公司

技术研发日:

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!