半导体器件及其制备方法、半导体集成电路及其制备方法与流程

本发明涉及半导体,特别涉及一种半导体器件及其制备方法、半导体集成电路及其制备方法。

背景技术:

1、现有技术中,常用的整流器一般包括肖特基势垒整流器和超势垒整流器(sbr,super barrier rectifier),其中超势垒整流器sbr可以为mos沟道中的多数载流子提供一个低势垒的环境,能够达到更低的反向电压和更低的反向漏电流,并且由于超势垒整流器sbr具有较高的稳定性和可靠性等优点从而被广泛应用于功率半导体器件中。

2、以屏蔽栅场效应晶体管(shielded gate trench,sgt)为例,其在栅电极的下方设置有屏蔽电极,从而可以大幅降低栅漏电容并优化器件电场,提高击穿电压,并且sgt器件的漂流区中还具有较高的杂质载流子浓度,相应的可以降低导通电阻。其中,针对具有屏蔽栅场效应晶体管的半导体器件而言,在关断晶体管时为了实现其快速开关、提高其反向恢复速度和降低功耗,则可在半导体器件中还额外设置超势垒整流器sbr,以在晶体管的关断过程中,提高器件的关断速度。

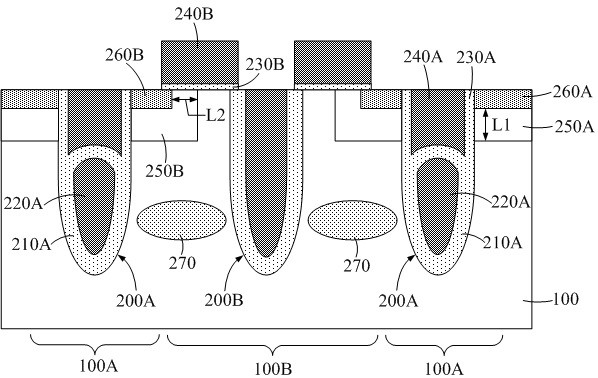

3、目前,在集成设置超势垒整流器sbr时,通常是以类似于集成设置的晶体管器件的结构设置,并将超势垒整流器sbr中的栅极介质层和晶体管器件中的栅极介质层分别设置为不同厚度。例如参考图5所示,图5中示意出了在sgt器件中集成设置有超势垒整流器sbr的结构,sgt器件包括设置在第一沟槽20a内的第一栅极介质层23a和第一栅电极24a,超势垒整流器sbr包括设置在第二沟槽20b内的第二栅极介质层23b和第二栅电极24b。其中,第二栅极介质层23b的厚度小于第一栅极介质层23a的厚度,以使超势垒整流器sbr具有较低的开启电压,从而能够在sgt器件关断时导通,以作为电流泄放通道。

4、由于超势垒整流器sbr中的第二栅极介质层23b和sgt器件中的第一栅极介质层23a需要设置为不同的厚度以满足各自器件的需求。为此,在制备第一栅极介质层23a和第二栅极介质层23b时,一般需要在制备第一栅极介质层23a之后,再额外去除第二沟槽20b内的介质材料,并重新制备第二栅极介质层23b在第二沟槽20b的侧壁上,其制备工艺繁杂、成本较高。

技术实现思路

1、本发明的目的在于提供一种半导体器件,该半导体器件的制备工艺易于被简化,有利于降低其制备成本。

2、为此,本发明提供一种半导体器件,包括:衬底,所述衬底定义有元胞区和整流区;第一晶体管器件,形成在所述元胞区中,所述第一晶体管器件包括:形成在所述衬底内的第一沟槽;形成在所述第一沟槽内的第一栅极介质层和第一栅电极;以及,超势垒整流器,形成在所述整流区中,所述超势垒整流器包括:形成在衬底顶表面上的第二栅极介质层和第二栅电极,其中所述第二栅极介质层的厚度小于所述第一栅极介质层的厚度。

3、可选的,所述第一晶体管器件包括屏蔽栅场效应晶体管,在所述第一沟槽内还形成有屏蔽电极,所述屏蔽电极位于所述第一栅电极的下方。

4、可选的,所述第一晶体管器件还包括第一阱区和第一源区,形成在第一沟槽侧边的衬底中,并且所述第一阱区相对于所述第一源区延伸至所述衬底的更深位置,以使所述第一栅电极与所述第一阱区具有相互重叠的部分。所述超势垒整流器还包括第二阱区和第二源区,形成在第二栅电极侧边的衬底中并往所述第二栅电极的方向延伸至所述第二栅电极的下方,并且所述第二阱区相对于所述第二源区在所述第二栅电极的下方延伸出更大尺寸,以使所述第二栅电极与所述第二阱区具有相互重叠的部分。

5、可选的,所述第二栅电极与所述第二阱区相互重叠的部分在宽度方向的尺寸小于等于所述第一栅电极和所述第一阱区相互重叠的部分在高度方向上的尺寸。

6、可选的,在所述整流区内还形成有第二沟槽,所述第二沟槽形成在所述第二栅极结构背离第二源区的一侧,并且在所述第二沟槽内形成有导电材料层。

7、可选的,在同一整流区内设置有至少两个整流单元,所述第二沟槽设置在相邻的整流单元之间。

8、可选的,在同一整流区内设置有至少两个整流单元,所述整流区中形成有至少一个第二栅电极,所述第二栅电极构成其两侧的两个整流单元共用的栅电极。

9、可选的,所述半导体器件具有包含多个元胞区的器件区域,在所述器件区域内的部分相邻的元胞区之间设置有所述整流区;和/或,在所述器件区域的边缘设置有所述整流区。

10、可选的,在所述整流区的衬底内还形成有反型掺杂区,所述反型掺杂区的导电类型与所述衬底的导电类型相反。

11、本发明还提供了一种半导体器件的制备方法,包括:提供一衬底,所述衬底定义有元胞区和整流区;刻蚀所述衬底,以至少在所述元胞区的衬底内形成第一沟槽;形成第一栅极介质层和第一栅电极在所述元胞区的第一沟槽内,用于形成第一晶体管器件;以及,形成第二栅极介质层和第二栅电极在所述整流区的衬底顶表面上,用于形成超势垒整流器,其中所述第二栅极介质层的厚度小于所述第一栅极介质层的厚度。

12、可选的,所述制备方法还包括:在刻蚀所述衬底以形成所述第一沟槽时,还在所述整流区的衬底内形成第二沟槽;以及,在所述第二沟槽内填充导电材料层。

13、可选的,形成第一栅极介质层和第一栅电极在所述元胞区的第一沟槽内之前还包括:在所述第一沟槽和所述第二沟槽内填满导电材料层,并回刻蚀所述第一沟槽内的导电材料层,以降低所述第一沟槽内的导电材料层的高度形成屏蔽电极;之后,形成所述第一栅极介质层和所述第一栅电极在所述第一沟槽高于所述屏蔽电极的空间中。

14、可选的,所述制备方法还包括:形成第一阱区和第二阱区,所述第一阱区形成在所述元胞区的衬底内,所述第二阱区形成在所述整流区的衬底内;以及,分别形成第一源区和第二源区在所述第一阱区和所述第二阱区内。

15、可选的,所述制备方法还包括:形成反型掺杂区在所述整流区的衬底内,所述反型掺杂区的导电类型与所述衬底的导电类型相反。

16、本发明还提供了一种半导体集成电路,包括:衬底,所述衬底定义有第一区域和第二区域;如上所述的半导体器件,所述半导体器件中的第一晶体管器件设置在所述第一区域的元胞区内,所述半导体器件中的超势垒整流器设置在所述第一区域的整流区内;以及,第二晶体管器件,设置在所述第二区域中,所述第二晶体管器件包括:形成在衬底顶表面上的第三栅极介质层和第三栅电极。其中,所述超势垒整流器中的第二栅极介质层和所述第二晶体管器件中的第三栅极介质层的厚度相同,并且均小于所述第一晶体管器件中的第一栅极介质层的厚度。

17、可选的,所述半导体集成电路包括设置在所述第二区域内的bcd器件,所述bcd器件包括所述第二晶体管器件。

18、本发明还提供了一种半导体集成电路的制备方法,包括:提供一衬底,所述衬底定义有第一区域和第二区域;采用如上所述的半导体器件的制备方法,在所述第一区域的元胞区内形成第一晶体管器件,在所述第一区域的整流区内形成超势垒整流器;以及,所述制备方法还包括:在所述第二区域的衬底顶表面上形成第三栅极介质层和第三栅电极,用于形成第二晶体管器件;其中,在制备所述第三栅极介质层的同时,还在所述整流区内形成所述第二栅极介质层,并使所述第二栅极介质层和所述第三栅极介质层的厚度均小于所述第一栅极介质层的厚度。

19、可选的,在制备所述第三栅电极的同时,还在所述整流区内形成所述第二栅电极。

20、可选的,所述半导体集成电路包括形成在所述第二区域内的bcd器件,所述bcd器件包括所述第二晶体管器件。

21、在本发明提供的半导体器件中,在元胞区内设置有第一晶体管器件,在整流区内形成有超势垒整流区,其中第一晶体管器件的栅极结构(包括第一栅极介质层和第一栅电极)形成在第一沟槽内,而超势垒整流器的栅极结构(包括第二栅极介质层和第二栅电极)则形成在衬底的顶表面上,使得超势垒整流器中位于衬底顶表面上的栅极结构可以更灵活的制备,有利于简化工艺。

22、进一步的,还可将超势垒整流器的栅极结构与其他器件的平面型栅极结构的制备工艺相互结合。例如,针对还集成有bcd器件的半导体集成电路而言,则可根据bcd器件中的cmos管的栅极介质层的厚度需要,同时制备cmos管的栅极介质层和超势垒整流器的栅极介质层。即,基于本公开中的超势垒整流器的结构特征,使得其栅极结构可利用集成设置的其他器件(例如bcd器件)的平面型栅极结构的制备工艺寄生形成,大大简化了集成电路的制备工艺,有效降低了制备成本。

- 还没有人留言评论。精彩留言会获得点赞!