超结半导体器件及其制造方法与流程

本发明涉及半导体,特别涉及一种超结半导体器件及其制造方法。

背景技术:

1、超结半导体器件采用多个p型柱和n型柱的交替结构作为漂移区,在反向电压击穿之前,p型柱和n型柱能够完全耗尽,漂移区相当于本征外延层,使得耐压仅和外延层厚度有关,而和外延层掺杂浓度无关,这样使得漂移区可以具有很浓的掺杂浓度,从而大大降低了导通电阻。

2、超结半导体器件可以通过多层外延堆叠工艺形成,多层外延堆叠工艺可以通过光刻定义cd的大小,然而工艺过程中的离子注入、外延沉积和光刻cd的波动都会引起p型柱和n型柱的失配,从而导致耐压的下降;而且,如果想要提高耐压,多层外延堆叠工艺需要进行更多次的外延沉积/光刻/离子注入,大大增加了工艺成本。

3、或者,超结半导体器件也可以通过深沟槽填充的工艺形成,对于深沟槽超结,深宽比是一个关键参数,若深宽比过大,会影响外延在深沟槽中的填充形貌,在深沟槽结构中产生细缝或空洞,影响耐压平衡曲线,因此,很难通过增加沟槽深度来提高器件耐压;同时,深沟槽超结元胞宽度也受到深宽比限制,很难做到更小宽度。

4、因此,如何在提高超结半导体器件耐压的同时,还能够降低工艺成本且缩小器件尺寸是目前亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种超结半导体器件及其制造方法,使得在提高耐压的同时,还能够降低工艺成本且缩小器件尺寸。

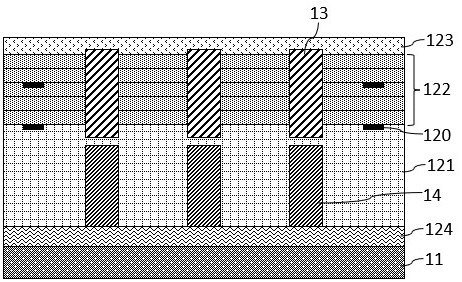

2、为实现上述目的,本发明提供了一种超结半导体器件,包括:

3、衬底;

4、第一外延层和第二外延层,形成于所述衬底上,所述第二外延层包括多层堆叠的子外延层,所述第一外延层比所述第二外延层更靠近所述衬底,或者,所述第二外延层比所述第一外延层更靠近所述衬底;

5、沟槽填充结构和离子掺杂区,所述沟槽填充结构形成于所述第一外延层中,所述离子掺杂区形成于所述第二外延层中,所述沟槽填充结构包括掺杂的外延材料,所述沟槽填充结构与所述离子掺杂区至少部分对准,所述沟槽填充结构和所述离子掺杂区构成第一导电类型柱,相邻所述沟槽填充结构之间的所述第一外延层以及相邻所述离子掺杂区之间的所述第二外延层构成第二导电类型柱。

6、可选地,所述沟槽填充结构与所述离子掺杂区之间间隔有部分厚度的所述第一外延层。

7、可选地,所述第一导电类型柱的导电类型为p型,所述第二导电类型柱的导电类型为n型。

8、可选地,所述超结半导体器件还包括:

9、第三外延层,当所述第一外延层比所述第二外延层更靠近所述衬底时,所述第三外延层形成于所述第二外延层远离所述第一外延层的一面,所述离子掺杂区的两端分别延伸进入所述第一外延层和所述第三外延层中;当所述第二外延层比所述第一外延层更靠近所述衬底时,所述第三外延层形成于所述第一外延层远离所述第二外延层的一面;所述第三外延层的导电类型与所述第二导电类型柱的导电类型相同。

10、可选地,所述超结半导体器件还包括:

11、第四外延层,当所述第一外延层比所述第二外延层更靠近所述衬底时,所述第四外延层形成于所述第一外延层与所述衬底之间;当所述第二外延层比所述第一外延层更靠近所述衬底时,所述第四外延层形成于所述第二外延层与所述衬底之间;所述第四外延层的导电类型与所述第二导电类型柱的导电类型相同。

12、可选地,部分层的所述子外延层中形成有对准标记。

13、本发明还提供一种超结半导体器件的制造方法,包括:

14、形成第一外延层、第二外延层、沟槽填充结构和离子掺杂区,所述第一外延层和所述第二外延层形成于所述衬底上,所述第二外延层包括多层堆叠的子外延层,所述第一外延层比所述第二外延层更靠近所述衬底,或者,所述第二外延层比所述第一外延层更靠近所述衬底;所述沟槽填充结构形成于所述第一外延层中,所述离子掺杂区形成于所述第二外延层中,所述沟槽填充结构包括掺杂的外延材料,所述沟槽填充结构与所述离子掺杂区至少部分对准,所述沟槽填充结构和所述离子掺杂区构成第一导电类型柱,相邻所述沟槽填充结构之间的所述第一外延层以及相邻所述离子掺杂区之间的所述第二外延层构成第二导电类型柱。

15、可选地,所述第一外延层比所述第二外延层更靠近所述衬底时,形成第一外延层、第二外延层、沟槽填充结构和离子掺杂区的步骤包括:

16、提供一基底,所述基底上形成有第一外延层;

17、形成第二外延层于所述第一外延层上,且形成离子掺杂区于所述第二外延层中;

18、去除所述基底;

19、形成沟槽填充结构于所述第一外延层中;

20、形成衬底于所述第一外延层远离所述第二外延层的一面上,所述衬底覆盖所述沟槽填充结构;

21、所述第二外延层比所述第一外延层更靠近所述衬底时,形成第一外延层、第二外延层、沟槽填充结构和离子掺杂区的步骤包括:

22、提供一衬底;

23、形成第二外延层于所述衬底上,且形成离子掺杂区于所述第二外延层中;

24、形成第一外延层于所述第二外延层和所述离子掺杂区上;

25、形成沟槽填充结构于所述第一外延层中。

26、可选地,所述沟槽填充结构与所述离子掺杂区之间间隔有部分厚度的所述第一外延层。

27、可选地,所述第一导电类型柱的导电类型为p型,所述第二导电类型柱的导电类型为n型。

28、与现有技术相比,本发明的技术方案具有以下有益效果:

29、1、本发明的超结半导体器件,由于包括:第一外延层和第二外延层,形成于所述衬底上,所述第二外延层包括多层堆叠的子外延层,所述第一外延层比所述第二外延层更靠近所述衬底,或者,所述第二外延层比所述第一外延层更靠近所述衬底;沟槽填充结构和离子掺杂区,所述沟槽填充结构形成于所述第一外延层中,所述离子掺杂区形成于所述第二外延层中,所述沟槽填充结构包括掺杂的外延材料,所述沟槽填充结构与所述离子掺杂区至少部分对准,所述沟槽填充结构和所述离子掺杂区构成第一导电类型柱,相邻所述沟槽填充结构之间的所述第一外延层以及相邻所述离子掺杂区之间的所述第二外延层构成第二导电类型柱,使得在提高耐压的同时,还能够降低工艺成本且缩小器件尺寸。

30、2、本发明的超结半导体器件的制造方法,通过形成第一外延层、第二外延层、沟槽填充结构和离子掺杂区,所述第一外延层和所述第二外延层形成于所述衬底上,所述第二外延层包括多层堆叠的子外延层,所述第一外延层比所述第二外延层更靠近所述衬底,或者,所述第二外延层比所述第一外延层更靠近所述衬底;所述沟槽填充结构形成于所述第一外延层中,所述离子掺杂区形成于所述第二外延层中,所述沟槽填充结构包括掺杂的外延材料,所述沟槽填充结构与所述离子掺杂区至少部分对准,所述沟槽填充结构和所述离子掺杂区构成第一导电类型柱,相邻所述沟槽填充结构之间的所述第一外延层以及相邻所述离子掺杂区之间的所述第二外延层构成第二导电类型柱,使得在提高耐压的同时,还能够降低工艺成本且缩小器件尺寸。

- 还没有人留言评论。精彩留言会获得点赞!