一种高压抗核辐射功率晶体管结构及制备方法与流程

本发明涉及高压功率半导体器件,特别涉及一种高压抗核辐射功率晶体管结构及制备方法。

背景技术:

1、功率晶体管由多个晶体管原胞组成,以便达到高的功率容量,同时硅功率双极晶体管具有技术成熟,成本低,可靠性高的特点,广泛应用于各行业电器系统中。同时在实际应用领域中,核辐射会对半导体材料造成损伤,造成晶体管基区少数载流子寿命大幅减小,电流增益显著下降,器件的电特性迅速退化,辐射积累到一定程度时导致器件功能失效,电器系统无法工作。

2、减轻核辐射对半导体器件参数影响的主要方法:1)更换半导体材料,2)采用窄发射极、薄基区、基区掺金或铂、电子辐照等,3)表面钝化技术。这些方法各自具备一些特点,可以起到降低晶体管电流增益的变化和改善器件表面对辐射的敏感度,但针对高压晶体管这一类具有宽基区和低掺杂浓度的外延层结构特点的功率器件,其抗核辐射性能难以得到明显提升。

技术实现思路

1、本发明的目的在于提供一种高压抗核辐射功率晶体管结构及制备方法,以解决功率晶体管核辐射条件下晶体管电流放大、击穿电压等电参数退化大、功能失效等问题,改善高压功率晶体管的抗核辐射性能。

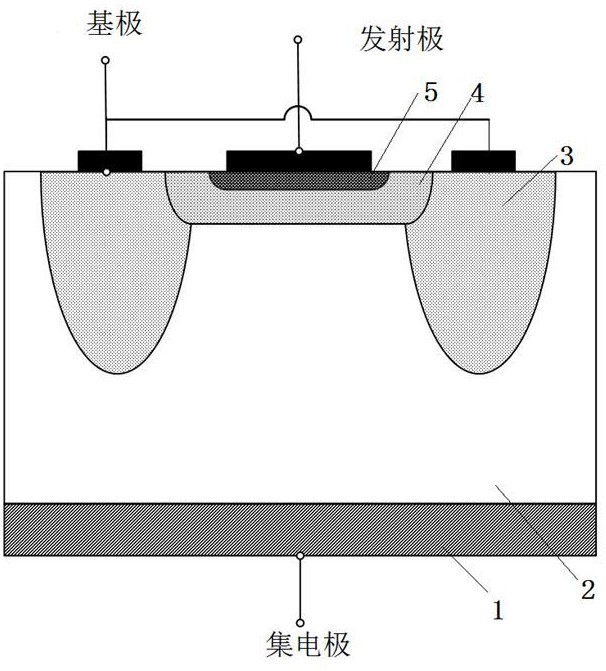

2、为解决上述技术问题,本发明提供了一种高压抗核辐射功率晶体管结构,包括:

3、n型高浓度衬底;

4、n型低浓度外延层,布设于所述n型高浓度衬底上;

5、深p型掺杂栅区,两个所述深p型掺杂栅区对称布设于所述n型低浓度外延层内的顶部外侧;

6、薄p型掺杂基区,布设于所述n型低浓度外延层内的顶部中部,且所述薄p型掺杂基区的两端分别与所述深p型掺杂栅区的顶部相交叠;

7、n型高浓度发射区,布设于所述薄p型掺杂基区内的顶部中部;

8、金属电极,包括集电极、基极和发射极;分别布设于所述n型高浓度衬底的底部、所述深p型掺杂栅区的顶部和所述n型高浓度发射区的顶部。

9、优选的,所述n型低浓度外延层的掺杂浓度为1e13cm-3~2e14cm-3,所述n型低浓度外延层的厚度为10um~60um。

10、优选的,所述深p型掺杂栅区的p型杂质注入浓度为2e13cm-2~1e15cm-2。

11、优选的,所述薄p型掺杂基区的p型杂质注入浓度为1e14cm-2~5e15cm-2。

12、优选的,所述n型高浓度发射区的n+离子注入浓度1e15cm-2~1e16cm-2。

13、优选的,所述n型低浓度外延层的顶部还包括布设的二氧化硅隔离介质层,以实现将所述基极和所述发射极进行隔离。

14、优选的,所述深p型掺杂栅区的栅间距wg需满足小于高压工作条件下二分之一深p型掺杂栅区的耗尽宽度wd,即2 wd>wg。

15、本发明还提供了一种高压抗核辐射功率晶体管结构的制备方法,包括如下步骤:

16、步骤1:在n型高浓度衬底上制备n型低浓度外延层;

17、步骤2:在n型低浓度外延层上生长0.5um~1um厚度的场氧化层,其退火工艺温度为950℃~1150℃;

18、步骤3:在场氧化层的表面涂敷光刻胶,曝光后湿法腐蚀形成深p型掺杂栅区的区域;

19、步骤4:在深p型掺杂栅区的区域进行0.01um~0.1um厚度的缓冲氧化层生长,其退火工艺温度为900℃~1000℃;

20、步骤5:通过离子注入机进行p型杂质的注入与退火,高温完成深p型掺杂栅区的扩散,其退火工艺温度为1100℃~1200℃;

21、步骤6:在深p型掺杂栅区的表面涂敷光刻胶,曝光后湿法腐蚀形成薄p型掺杂基区的区域,再进行基区p型杂质的注入与退火,其退火工艺温度为950℃~1050℃;

22、步骤7:在薄p型掺杂基区的表面涂敷光刻胶,曝光后湿法腐蚀形成n型高浓度发射区的区域,再进行n+离子注入与退火,其退火工艺温度为900℃~1000℃;

23、步骤8:在n型高浓度发射区和深p型掺杂栅区的表面涂敷光刻胶,曝光后湿法腐蚀形成接触孔;

24、步骤9:在接触孔上进行1um~2um厚度的金属铝淀积并光刻腐蚀形成相对应的基极和发射极;

25、步骤10:对n型高浓度衬底的背面进行减薄,在减薄后对其背面进行金属化并光刻腐蚀形成相对应的集电极。

26、本发明与现有技术相比,具有如下有益效果:

27、本发明以半导体器件物理为理论基础,在结构设计上运用电荷平衡理论,提出了一种具有薄基区特征,可以实现高耐压,并能在核辐射环境下可靠工作的功率晶体管结构及制备方法,能有效抑制核辐射条件下晶体管电流放大、击穿电压等电参数退化,使其抗核辐射性能得到明显提高。

技术特征:

1.一种高压抗核辐射功率晶体管结构,其特征在于,包括:

2.如权利要求1所述的一种高压抗核辐射功率晶体管结构,其特征在于,所述n型低浓度外延层的顶部还包括布设的二氧化硅隔离介质层,以实现将所述基极和所述发射极进行隔离。

3.一种高压抗核辐射功率晶体管结构的制备方法,用于制备如权利要求1或2所述的一种高压抗核辐射功率晶体管结构,其特征在于,包括如下步骤:

技术总结

本发明涉及高压功率半导体器件技术领域,特别涉及一种高压抗核辐射功率晶体管结构及制备方法。包括:N型高浓度衬底;N型低浓度外延层,布设于N型高浓度衬底上;深P型掺杂栅区,两个深P型掺杂栅区对称布设于N型低浓度外延层内的顶部外侧;薄P型掺杂基区,布设于N型低浓度外延层内的顶部中部,且薄P型掺杂基区的两端分别与深P型掺杂栅区的顶部相交叠;N型高浓度发射区,布设于薄P型掺杂基区内的顶部中部;金属电极。本发明以解决功率晶体管核辐射条件下晶体管电流放大、击穿电压等电参数退化大、功能失效等问题,改善高压功率晶体管的抗核辐射性能。

技术研发人员:蔡树军,吴建伟,张明

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:

技术公布日:2024/5/10

- 还没有人留言评论。精彩留言会获得点赞!