一种MOSFET栅极负反馈有源驱动电路

一种mosfet栅极负反馈有源驱动电路

技术领域

1.本实用新型涉及一种mosfet栅极负反馈有源驱动电路。

背景技术:

2.基于碳化硅(sic)、氮化镓(gan)等宽禁带材料的mosfet的高开关速度使变换器获得效率、功率密度优势,是高性能电力电子变换领域的重要技术保障。但更高开关速度带来更大干扰,成为制约sic/gan mosfet充分发挥快速特性的主要瓶颈之一。

3.国内外学者对栅极电压干扰抑制方法进行了研究,可以大致归纳为无源类抑制方法和有源类抑制方法。

4.无源类方法,采用无源元件对栅极寄生振荡进行抑制,主要包括:在栅源极之间增加辅助电容、栅极驱动采用负向关断电压等,参见文献[1

‑

3]。虽然在栅源极之间增加辅助电容,可以分担源自米勒电容的干扰电流,避免其流入栅极,抑制了栅极干扰,但是附加的辅助电容会使开关速度变慢、开关损耗增大,导致开关性能变差。栅极驱动采用负向关断电压的方法,由于增加了栅极电压的负向偏置,有效防止了栅极干扰触发误导通,但代价是恶化了栅极电压的负向应力。

[0005]

为达到更好的mosfet栅极电压干扰抑制效果,研究人员引入栅极前馈控制,研究了多种有源抑制技术。文献[4]引入四个开关管组成的辅助电路,构成多电平有源驱动(multi

‑

level active gate driver,multi

‑

level agd)通过fpga(field programmable gate arrays)控制器检测器件的干扰信号,基于器件参数模型预测振荡趋势,以避免干扰影响,文献中的实测波形显示,在dv/dt=5v/ns时,multi

‑

level agd技术可以有效抑制栅极干扰。然而,考虑到sic/gan mosfet的开关时间和栅极干扰振荡周期短至几十纳秒,采样的传播延迟与开关时间、振荡周期可能是可比的,甚至更长,检测信号的传播延迟问题是一项挑战。文献[2,3,5]研究了有源米勒钳位技术(active miller clamp,amc),其工作原理是在检测到栅极电压高于钳位阈值后,主动使能在栅源极之间的辅助晶体管,将栅极直接钳位于负向偏置电压。然而,在快速开关瞬态过程中,检测信号的抗干扰问题是一项挑战,这是因为更大的dv/dt引发更高频率的栅极干扰振荡,由于共源电感、检测回路杂散电感的干扰,检测所得信号容易产生较大偏差。文献[2]研究表明amc技术在dv/dt低于20v/ns时,可以显著改善栅极干扰振荡,但是,在较高的dv/dt情况下,对于栅极干扰振荡,特别是负向振荡的缓解作用有限。文献[6]提出了两种米勒电容耦合振荡抑制方法:一是,栅极阻抗调节技术(gate impedance regulation,gir),由一个开关管和一个电容组成的辅助电路,根据驱动信号规律预测栅极振荡趋势,通过逻辑信号发生器控制辅助开关管,在开关瞬态过程中降低栅极阻抗,从而钳位栅极电压,抑制栅极干扰,dv/dt可达24.4v/ns;二是,栅极电压控制技术(gate voltage control,gvc),由两个开关管和一个二极管组成的辅助电路,根据驱动信号规律预测栅极振荡趋势,通过逻辑信号发生器控制辅助开关管,在开关瞬态之前对栅源电容进行预充电,从而反向抵消干扰振荡趋势,dv/dt可达24.9v/ns。在后续研究中,文献[7]提出了智能栅极驱动器(intelligent gate drive,igd),由两个开关管和两

个二极管组成的辅助电路,在不同的开关瞬态下,根据驱动信号规律预测栅极振荡趋势,通过逻辑信号发生器控制辅助开关管,通过改变功率器件的栅极电压和栅极阻抗,抑制栅极干扰。实测波形显示,在dv/dt=40v/ns时,igd技术可以有效抑制栅极干扰。然而,不同工况下,mosfet承受的电压和电流不同,栅极干扰振荡幅值和频率也不尽相同。mosfet的运行工况变化时,根据固定规律预测栅极干扰振荡趋势易出现过补偿或欠补偿,影响前馈控制精度。利用前馈控制栅极电压抑制干扰的方法,一般通过检测栅极电压或干扰源,根据驱动信号规律或根据mosfet参数模型预测振荡趋势,提前采取措施,避免寄生振荡。然而,高速开关干扰使得栅极寄生振荡具有高频特性,因此,检测信号易受干扰且存在明显误差;振荡趋势受mosfet工作环境影响,难以精确预测,容易造成前馈控制的不准确。

[0006]

综上所述,鉴于栅极干扰的高频特性及前馈控制精度限制,典型栅极前馈控制下mosfet可承受的电压变化率(dv/dt)有限,因此,通过控制栅极电压以有源抑制栅极寄生振荡,目前仍是一项极具挑战的工作。栅极干扰现象因而更加显著,成为充分发挥sic/gan mosfet快速特性的主要瓶颈之一。

[0007]

参考文献如下:

[0008]

[1]zeng z,li x.comparative study on multiple degrees offreedom of gate drivers for transient behavior regulation of sic mosfet[j].ieee transactions on power electronics,2018,33(10):8754

‑

8763.

[0009]

[2]stmicroelectronics an

‑

5355.mitigation technique of the sic mosfet gate voltage glitches with miller clamp[eb/ol].available online at https://www.st.com(accessed on 18 march,2020).

[0010]

[3]avago technologies an

‑

5314.active miller clamp[eb/ol].available online at http://www.avagotech.com(accessed on 18 march,2020).

[0011]

[4]zhao s,dearien a,wu y,et al.adaptive multi

‑

level active gate drivers for sic power devices[j].ieee transactions on power electronics,2020,35(2):1882

‑

1898.

[0012]

[5]chen z,danilovic m,boroyevich d,et al.modularized design consideration of a general

‑

purpose,high

‑

speed phase

‑

leg pebb based on sic mosfets:proceedings ofthe 201114th european conference on power electronics and applications[c].birmingham,uk:30 aug.

‑

1 sept.2011.

[0013]

[6]zhang z,wang f,tolbert l m,et al.active gate driver for crosstalk suppression of sic devices in a phase

‑

leg configuration[j].ieee transactions on power electronics,2014,29(4):1986

‑

1997.

[0014]

[7]zhang z,dix j,wang f,et al.intelligent gate drive for fast switching and crosstalk suppression of sic devices[j].ieee transactions on power electronics,2017,32(12):9319

‑

9332.

技术实现要素:

[0015]

本实用新型要解决的技术问题,在于提供一种mosfet栅极负反馈有源驱动电路,使得在不牺牲mosfet开关速度以及不增加电路复杂性的前提下,自动抑制栅源电压干扰。

[0016]

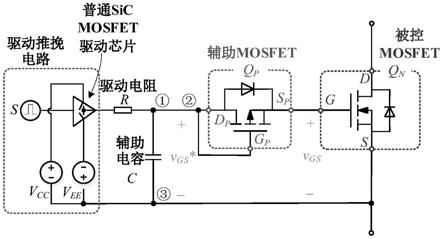

本实用新型是这样实现的:一种mosfet栅极负反馈有源驱动电路,用于连接驱动信号,进行控制被控mosfet的开和关,包括:

[0017]

一辅助mosfet,所述辅助mosfet为p沟道mosfet,所述辅助mosfet源极与被控mosfet栅极相连接,用于构造负反馈调节机制,所述辅助mosfet漏极连接到驱动电压;所述驱动电压为驱动芯片经过无源网络滤波后的电压。

[0018]

进一步地,还包括:第一节点、第二节点以及第三节点;

[0019]

驱动推挽电路,用于提供驱动电流以驱动被控mosfet,所述驱动信号连接至所述驱动推挽电路,所述驱动推挽电路与第三节点串联;

[0020]

驱动电阻r,所述驱动电阻r一端与驱动推挽电路串联,另一端与第一节点相连,用于限制驱动推挽电路对辅助电容c的充放电电流,第一节点与被控mosfet源极之间的电压差为驱动电压;

[0021]

辅助电容c,所述辅助电容c一端与第一节点相连接,另一端通过第三节点与被控mosfet源极相连接,与驱动电阻r构成无源网络,用于调节被控mosfet的开关速度;

[0022]

所述辅助mosfet漏极和栅极通过第二节点与所述驱动电阻r串联,所述辅助mosfet源极与被控mosfet栅极相连接,用于构造负反馈调节机制。

[0023]

进一步地,所述驱动推挽电路包括一mosfet驱动芯片、开通偏置电压v

cc

以及关断偏置电压v

ee

;所述mosfet驱动芯片输出电源正端口连接至开通偏置电压v

cc

的正极,所述mosfet驱动芯片输出电源负端口连接至关断偏置电压v

ee

的负极,所述mosfet驱动芯片的驱动输出端口连接至所述驱动电阻r的一端,所述驱动芯片的驱动输入端口连接至驱动信号;所述开通偏置电压v

cc

的负极以及关断偏置电压v

ee

的正极均连接至所述第三节点;在驱动能力上,mosfet的驱动芯片输出电流应不小于(v

cc

‑

v

ee

)/r

g

,其中r

g

为被控mosfet的栅极寄生电阻。

[0024]

进一步地,所述辅助mosfet的漏源击穿电压不小于v

cc

‑

v

ee

,且承受的连续漏极电流不小于(v

cc

‑

v

ee

)/r

g

。

[0025]

本实用新型的优点在于:一种mosfet栅极负反馈有源驱动电路,结构简单,易于实现,不依赖额外的电路,仅采用普通的mosfet的驱动芯片、驱动电阻、辅助mosfet和辅助电容即可实现。在功能上,该mosfet栅极负反馈有源驱动电路能够在不牺牲mosfet开关速度的前提下,自动抑制栅源电压干扰,实现高速开关下的栅压稳定。在后续的实例中,相比传统的无源抑制方案,该mosfet栅极负反馈有源驱动电路可以实现更大幅度的栅源电压振荡抑制,而且,不会以牺牲开关速度为代价,开关速度尚有一定程度的提高。

附图说明

[0026]

下面参照附图结合实施例对本实用新型作进一步的说明。

[0027]

图1是本实用新型所述的一种mosfet栅极负反馈有源驱动电路的结构示意图;

[0028]

图2是本实用新型所述的一种mosfet栅极负反馈有源驱动电路的控制框图;

[0029]

图3为根据本实用新型实施例的桥臂结构中的栅极负反馈有源驱动;

[0030]

图4a是根据本实用新型实施例的栅极负反馈有源驱动的q

h

开通过程的原理波形;

[0031]

图4b是根据本实用新型实施例的栅极负反馈有源驱动的q

h

关断过程的原理波形;

[0032]

图5a是根据本实用新型实施例的一种mosfet栅极负反馈有源驱动电路对照的无

任何抑制措施的实验电路图;

[0033]

图5b是根据本实用新型实施例的一种mosfet栅极负反馈有源驱动电路对照的采用被动抑制措施的实验电路图;

[0034]

图5c是根据本实用新型实施例的一种mosfet栅极负反馈有源驱动电路对照的采用负反馈有源驱动的实验电路图;

[0035]

图6a是根据本实用新型实施例的无干扰抑制的传统驱动电路中一个开关周期内的实验波形;

[0036]

图6b是根据本实用新型实施例的无干扰抑制的传统驱动电路中v

ds2

上升沿放大的实验波形;

[0037]

图6c是根据本实用新型实施例的无干扰抑制的传统驱动电路中v

ds2

下降沿放大的实验波形;

[0038]

图7a是根据本实用新型实施例的采用无源抑制方法的驱动电路中一个开关周期内的实验波形;

[0039]

图7b是根据本实用新型实施例的采用无源抑制方法的驱动电路中v

ds2

上升沿放大的实验波形;

[0040]

图7c是根据本实用新型实施例的采用无源抑制方法的驱动电路中v

ds2

下降沿放大的实验波形;

[0041]

图8a是根据本实用新型实施例的采用mosfet栅极负反馈有源驱动电路中一个开关周期内的实验波形;

[0042]

图8b是根据本实用新型实施例的采用mosfet栅极负反馈有源驱动电路中v

ds2

上升沿放大的实验波形;

[0043]

图8c是根据本实用新型实施例的采用mosfet栅极负反馈有源驱动电路中v

ds2

下降沿放大的实验波形。

具体实施方式

[0044]

本实用新型一种实施方式:

[0045]

如图1所示,采用所述mosfet栅极负反馈有源驱动电路驱动mosfet q

n

。若被控mosfet q

n

为桥臂电路中的主动管,导通开始时刻,pwm信号s从低电平变为高电平,驱动芯片输出端连接到导通偏置电压v

cc

,驱动芯片经过驱动电阻r为辅助电容c充电,驱动电压v

gs

*增大,逐渐从v

ee

上升到v

cc

。初始时刻,由于被控mosfet q

n

的栅源电压v

gs

仍然处于关断偏置电压v

ee

,这使得d

p

的电位高于s

p

的电位,电位差超过阈值电压后,q

p

寄生体二极管正向导通,驱动芯片通过q

p

寄生体二极管为q

n

的输入电容c

iss

充电,q

n

的栅源电压v

gs

增大;倘若v

gs

过大使得s

p

的电位高于d

p

的电位,当该电位差达到q

p

导通阈值电压时,q

p

沟道导通,为q

n

的输入容c

iss

放电,v

gs

则会随之减小;由于该负反馈机制的存在,导通过程中,q

n

的栅源电压v

gs

将紧紧跟随驱动电压v

gs

*变化。同理,关断开始时刻,pwm信号s从高电平变为低电平,驱动芯片输出端连接到关断偏置电压v

ee

,驱动芯片为辅助电容c放电,驱动电压v

gs

*减小,逐渐从v

cc

下降到v

ee

。初始时刻,由于被控mosfet q

n

的栅源电压v

gs

仍然处于导通偏置电压v

cc

,这使得s

p

的电位高于d

p

的电位,电位差超过阈值电压后,q

p

沟道导通,驱动芯片通过q

p

的沟道为q

n

的输入电容c

iss

放电,q

n

的栅源电压v

gs

减小;倘若v

gs

过小使得d

p

的电位高于s

p

的电位,

电位差高于阈值电压时,q

p

寄生体二极管导通,为q

n

的输入容c

iss

充电,v

gs

则会随之增大;由于该负反馈机制的存在,关断过程中,q

n

的栅源电压v

gs

将紧紧跟随驱动电压v

gs

*变化。

[0046]

若被控mosfet q

n

为桥臂电路中的被动管,则需要关断钳位,抵抗外界干扰。此时,pwm信号s一直是低电平,栅极驱动芯片的输出电压为关断偏置电压v

ee

,驱动电压v

gs

*=v

ee

。q

n

的栅源电压v

gs

在稳态时等于关断偏置电压v

ee

;当q

n

的栅源电压v

gs

受到干扰出现波动时,触发负反馈机制。若q

n

的栅源电压v

gs

受干扰升高,当s

p

的电位高于d

p

的电位,且电位差超过阈值电压时,q

p

沟道导通,驱动芯片通过q

p

的沟道为q

n

的输入电容c

iss

放电,q

n

的栅源电压v

gs

减小;若q

n

的栅源电压v

gs

受干扰降低,当d

p

的电位高于s

p

的电位,且电位差超过阈值电压时,q

p

寄生体二极管导通,为q

n

的输入容c

iss

充电,v

gs

则会随之增大。由于该负反馈机制的存在,q

n

的栅源电压v

gs

受到干扰出现波动时,q

n

的栅源电压v

gs

将紧紧钳位于驱动电压v

gs

*=v

ee

。

[0047]

如图2所示,是本实用新型所述电路所特有的负反馈调节机制。本实用新型所述驱动电路通过该机制屏蔽脉冲电压、脉冲电流的干扰,实现高速开关下的栅压稳定。驱动电压v

gs

*作为栅源极的参考信号,输入栅极负反馈控制回路。参考信号与被控mosfet的栅源电压v

gs

之差,通过辅助mosfet的跨导增益g

m

,控制被控mosfet输入电容c

iss

、栅极内电阻r

g

共同构成的被控对象。考虑外界的脉冲电压、脉冲电流的干扰n(s),一般通过米勒电容产生位移电流,对被控mosfet的c

iss

充放电干扰栅源电压。若v

gs

增大(或减小),则与参考值v

gs

*之差增大,经过驱动管跨导增益的调节后,对输入电容c

iss

放电(或充电),被控mosfet的栅源电压v

gs

恢复稳定。栅极负反馈控制的目标是让被控mosfet的栅源电压v

gs

跟踪驱动信号v

gs

*的变化,并屏蔽脉冲电压、脉冲电流的干扰n(s)。在不牺牲开关速度的前提下,自动抑制栅源电压干扰,实现高速开关下的栅压稳定。

[0048]

如图3所示,本实施例展示了用于桥臂结构的负反馈有源驱动电路。其中,桥臂上管q

h

和桥臂下管q

l

均采用结电容的形式表示,以便于使用者理解mosfet栅极负反馈有源驱动电路的工作原理。在图3中,为区分上管和下管,分别增添角标“1”和“2”,或分别增添角标“l”和“h”。r1和r2分别代表上管和下管的驱动电阻,c1和c2分别代表上管和下管的辅助电容,q

p1

和q

p2

分别代表上管和下管的辅助mosfet。桥臂上管q

h

作为主动管,在脉冲控制信号s1的控制下,开通、关断;桥臂下管q

l

作为被动管,其控制信号s2一直处于低电平,q

l

沟道关断,仅用其寄生体二极管续流。

[0049]

mosfet的米勒电容c

gdh

和c

gdl

随着漏源电压的增大而降低。为了方便揭示负反馈有源驱动电路原理,在接下来的实施例中引入分段线性化的近似曲线,拟合实际曲线。当漏源电压大于栅源电压时,c

gdh

和c

gdl

的值为c

gd1

;当漏源电压小于栅源电压时,c

gdh

和c

gdl

的值为c

gd2

。桥臂中点输出电流,在一个开关周期中,近似恒定,因此以恒流源表示为i

l

。同时,记桥臂上的直流电压为v

dc

。

[0050]

如图4a和图4b所示,分别展示了图3所示电路的q

h

开通和关断动态过程的理论波形,分别以s1从低电平变为高电平的时刻、s1从高电平变为低电平的时刻为初始时刻,两个动态过程分别有4个主要模态,详述如下:

[0051]

1、如图4a所示,q

h

开通过程

[0052]

开通模态1:开通延迟阶段t

d(on)

。0时刻,s1从低电平变为高电平,驱动芯片通过r1为辅助电容c1充电,驱动电压v

gs1

*增大,逐渐从v

ee1

上升到v

cc1

。由于所述负反馈机制,q

h

的栅源电压v

gs1

跟随v

gs1

*变化,也逐渐增大,然而由于图1所述栅极负反馈有源驱动是i型系统,

其对于斜坡信号v

gs1

*的跟踪存在一定误差,但由于开环放大倍数足够大,该跟踪误差不会影响驱动电路正常工作。该模态中,由于v

gs1

尚小于阈值电压v

gs,th

,q

h

的沟道处于关断状态,i

d1

=0。v

ds1

处于v

dc

不变,当v

gs1

上升到达v

gs,th

时,该模态结束。

[0053]

开通模态2:电流上升阶段t

ri

。v

gs1

从阈值电压v

gs,th

开始,升高到v

gs,il

,表示可以维持沟道电流为i

l

的v

gs1

值。v

ds1

处于v

dc

不变。q

h

的电流i

d1

从0开始上升至i

l

。该过程中,由于被动管电流i

d2

的降低,q

l

的栅源电压v

gs2

产生微小上升,但不足以触发q

p2

导通。在忽略q

l

寄生体二极管反向恢复的条件下,该模态在电流上升至i

l

的时刻结束。

[0054]

开通模态3:电压下降阶段t

fv1

。普通驱动电路情况下,将进入米勒平台,栅源电压维持在v

gs,il

不变。但采用栅极负反馈有源驱动的mosfet,由于图1实施例所述负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起升高,不会维持在v

gs,il

不变。在该模态中,v

ds1

从v

dc

开始下降,由于漏源电压仍然大于栅源电压,c

gdh

的值依旧相对较小(c

gd1

),该阶段v

ds1

下降速度相对较快。该模态中,q

l

的漏源电压v

ds2

迅速上升,因而q

l

的栅源电压v

gs2

产生较大幅度的上升;由于图1实施例所述负反馈机制的存在,当s

p2

的电位高于d

p2

的电位,且电位差超过阈值电压v

th

时,q

p2

沟道导通,驱动芯片通过q

p2

的沟道为q

l

的输入电容c

issl

放电,q

l

的栅源电压v

gs2

减小,干扰得到抑制,v

gs2

又回到v

ee2

。当v

ds1

下降到与v

gs1

在数值上相等时,该模态结束。

[0055]

开通模态4:电压下降阶段t

fv2

。由于图1实施例所述负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起升高,不会维持在v

gs,il

不变。v

ds1

继续下降,由于漏源电压小于栅源电压,c

gdh

的值相对较大(c

gd2

),该阶段v

ds1

下降速度相对较慢。当v

ds1

下降到v

ds(on)

时,该模态结束。

[0056]

开通模态4之后,由于上述负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起升高到高电平v

cc1

,最终完成开通过程。

[0057]

2、如图4b所示,q

h

关断过程

[0058]

关断模态1:关断延迟阶段t

d(off)

。0时刻,s1从高电平变为高电平,驱动芯片通过r1为辅助电容c1放电,驱动电压v

gs1

*减小,逐渐从v

cc1

下降到v

ee1

。由于图1实施例中负反馈机制,q

h

的栅源电压v

gs1

跟随v

gs1

*变化,也逐渐减小,然而由于图1所示栅极负反馈有源驱动是i型系统,其对于斜坡信号v

gs1

*的跟踪存在一定误差,但由于开环放大倍数足够大,该跟踪误差不会影响驱动电路正常工作。由于栅源电压尚大于阈值电压v

gs,th

,q

h

的沟道处于导通状态,因而仍然有i

d1

=i

l

,v

ds1

尚处于v

ds(on)

不变。当v

gs1

下降到达v

gs,il

时,该模态结束。

[0059]

关断模态2:电压上升阶段t

rv1

。普通驱动电路情况下,将进入米勒平台,栅源电压维持在v

gs,il

不变。但采用栅极负反馈有源驱动的mosfet,由于图1实施例所述负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起降低,不会维持在v

gs,il

不变,而是继续下降。该模态中,v

ds1

从v

ds(on)

开始上升。由于漏源电压仍然小于栅源电压,c

gdh

的值依旧相对较大(c

gd2

),该阶段v

ds1

上升速度相对较慢。当v

ds1

上升到与v

gs1

在数值上相等时,该模态结束。

[0060]

关断模态3:电压上升阶段t

rv2

。由于图1所示负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起降低。该模态中,v

ds1

继续上升。由于漏源电压大于栅源电压,c

gdh

的值相对较小(c

gd1

),该阶段v

ds1

上升速度相对较快。q

l

的漏源电压v

ds2

迅速下降,因而q

l

的栅源电压v

gs2

产生较大幅度的下降;由于图1所示负反馈机制的存在,当d

p2

的电位高于s

p2

的电位,且电位差超过阈值电压v

th

时,q

p2

寄生体二极管导通,驱动芯片通过q

p2

的寄生体二极管为q

l

的

输入电容c

issl

充电,q

l

的栅源电压v

gs2

增大,干扰得到抑制,v

gs2

又回到v

ee2

。当v

ds1

上升到v

dc

时,该模态结束。

[0061]

关断模态4:电流下降阶段t

fi

。由于图1所示负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起降低,直到达到阈值电压v

gs,th

。该过程中,由于被动管电流i

d2

的升高,q

l

的栅源电压v

gs2

产生微小下降,但不足以触发q

p2

的寄生体二极管导通。该模态中,v

ds1

处于v

dc

不变,q

h

的电流i

d1

从i

l

开始下降至0,该模态结束。

[0062]

关断模态4之后,由于图1实施例所示负反馈机制的存在,q

h

的栅源电压v

gs1

仍然跟随v

gs1

*一起降低,从阈值电压v

gs,th

一直到降低到低电平v

ee1

,最终完成关断过程。

[0063]

本实用新型所述栅极负反馈有源驱动电路参数设计原则叙述如下。

[0064]

(1)被控mosfet选型原则

[0065]

本实用新型所述栅极负反馈有源驱动时,需首先依据功率变换装置的工作环境,确定被控mosfet,作为主功率电能变换的开关器件。与传统驱动方式下的功率变换装置的功率开关器件选型原则一致,一般在功率变换装置额定工作状态下,计算获得的器件的最大工作电压、工作电流,确保mosfet处于安全工作区内,参考器件允许的最大漏源极电压和最大漏极电流,确定mosfet型号。在该实施实例中,选择商业化程度较高且大功率电能变换领域较为典型的一款器件,作为被控mosfet,以示范验证所提方法的技术可行性。该mosfet的最大漏源极电压1200v、最大漏极电流56a,型号是imz120r030m1h。

[0066]

(2)驱动芯片选型及其外围电路设计原则

[0067]

由于被控mosfet的阈值电压较低(约2

‑

4v),虽然栅极负反馈有源驱动电路具有稳定栅源电压,屏蔽脉冲电压和脉冲电流干扰影响的作用,但并非完全根除栅极的不稳定问题。因此,驱动的负压关断是十分必要的。推荐开通偏置电压v

cc

=18~22v,关断偏置电压v

ee

=

‑

2.5~

‑

5v。可采用金升阳驱动电源模块qa01c系列(或类似替代产品)实现开通和关断偏置电压。基于以上考虑,该实施实例的设计中,采用开通电压v

cc

=20v,关断电压v

ee

=

‑

5v。

[0068]

推荐共模瞬变抗扰度cmti≥100v/ns(全温度范围内)。在驱动能力上,芯片输出电流应不小于(v

cc

‑

v

ee

)/r

g

,其中r

g

为被控mosfet的栅极寄生电阻。例如,前述所选被控mosfet(imz120r030m1h)的栅极内电阻r

g

=3ω,故而芯片输出电流应不小于8.3a,该实施实例中采用驱动芯片1ed3124mu12h,输出电流可达14a。

[0069]

(3)辅助mosfet选型原则

[0070]

辅助mosfet需选取与被控mosfet沟道特性对偶的器件实现,一般情况下,被控mosfet为n沟道,因此,辅助mosfet应为p沟道mosfet。同时,为保证控制精度,辅助mosfet的跨导增益远大于1(s)。此外,由于被控mosfet的开通和关断过程中,辅助mosfet需承受一定的电压和电流,因此,为保证辅助mosfet安全工作,需根据驱动芯片设计的开通偏置电压v

cc

关断偏置电压v

ee

,以及被控mosfet栅极特性,选取辅助mosfet的电压、电流等级,推荐漏源击穿电压不小于v

cc

‑

v

ee

,且可承受的连续漏极电流不小于(v

cc

‑

v

ee

)/r

g

。基于以上分析,该实施实例采用fds9435a作为p沟道的辅助mosfet,其漏源击穿电压为30(v),可承受的连续漏极电流为25(a),跨导增益为10(s)。

[0071]

(4)辅助电容和驱动电阻设计原则

[0072]

驱动芯片输出端连接的辅助电容和驱动电阻(如图1中的c和r),一起影响v

gs

上升

下降速度。由于一般情况下,被控mosfet的输入电容约nf级,而辅助mosfet的跨导增益远大于1(s)。因此栅极负反馈有源驱动电路的开环放大倍数足够大。当v

gs

跟踪斜坡上升(下降)的v

gs

*时,二者之间的偏差很小,v

gs

*与v

gs

具有近似相等的上升下降速度。

[0073]

辅助电容c在功能上还有解耦作用,缩短驱动芯片输出端与辅助mosfet与被控mosfet栅源极构成回路的“电气周长”。推荐辅助电容c在桥臂电路的功率回路无阻尼自振荡频率处,具有不大于0.2ω的阻抗,即:

[0074]

该实施例中,被控mosfet(imz120r030m1h)的输出容c

oss

=116pf,功率回路的杂散电感l

o

估算为50nh,因而根据上述公式,辅助电容c应当不小于12nf;工程上选取辅助电容c=20nf以确保其在功率回路无阻尼自振荡频率处的阻抗足够小。

[0075]

辅助电容c选取之后,即可设计驱动电阻r。驱动电阻r与辅助电容c的乘积τ=rc,是该阻容电路的充放电时间常数。充放电时间常数τ与栅源电压上升下降斜率成反比,即较大的充放电时间常数τ将导致较缓慢的栅源电压上升下降时间,因此,被控mosfet的开关速度也将变缓。反之,若需加快被控mosfet的开关速度,如需要降低损耗、提高效率的场合,就可以采用较小的充放电时间常数τ,获得较快的开关速度。然而,驱动电阻r在功能上还需兼顾对驱动芯片的限流和保护作用,开关动作伊始,驱动芯片经过驱动电阻r对辅助电容c充放电电流达到峰值(v

cc

‑

v

ee

)/r。为最大限度利用该实施例所选驱动芯片的带负载能力,让mosfet获得相对较快的开关速度,本实施例依据驱动芯片输出电流峰值的70%设计充放电电流峰值(v

cc

‑

v

ee

)/r。开通电压v

cc

=20v,关断电压v

ee

=

‑

5v,1ed3124mu12h最大输出电流的70%约10a,因此,驱动电阻r=2.5ω,对应的充放电时间常数τ=50ns。需要注意的是,此处对驱动电阻r的设计仅做示范说明之用,工业应用中,驱动电阻可根据效率、损耗、电磁兼容等综合需求,结合辅助电容的取值灵活调试选取。

[0076]

(5)驱动电路的pcb设计

[0077]

为保证了硬件设计的可靠性,需在主功率部分减小功率线路中的寄生电感,降低功率管mosfet漏源电压振荡和尖峰。本实施例采用了上下两层均铺铜,中间过孔连接的方式。在驱动回路中,为了使回路寄生电感尽可能的小,通过尽可能地缩短驱动回路长度,将主要元器件在满足安全规定的情况下尽可能地贴近功率管mosfet,同时采用大面积铺铜的方式缩短驱动回路,以保证辅助mosfet可以有效工作,不受引线杂散参数影响。

[0078]

如图5a、5b以及5c所示,为本实施例在双脉冲电路中的实验电路,包括了一种mosfet栅极负反馈有源驱动电路对照的无任何抑制措施的实验电路、一种mosfet栅极负反馈有源驱动电路对照的采用被动抑制措施的实验电路以及一种mosfet栅极负反馈有源驱动电路对照的采用负反馈有源驱动的实验电路;均设置一驱动脉冲驱动主动mosfet q

h

,设置一负向电压偏置,用于关断被动mosfet q

l

,在该实施例中对比了三种案例下被动管q

l

栅源极电压v

gs2

受到干扰的情况,用于验证采用mosfet栅极负反馈有源驱动电路稳定栅源电压的有效性。

[0079]

如图6a至图6c所示,为本实用新型实施例的无干扰抑制的传统驱动电路实验波形,主动管q

h

以及被动管q

l

的驱动仅有驱动电阻,对应的驱动电阻均为10ω。如图6a所示,被动管q

l

栅源极电压v

gs2

受到干扰出现较大振荡,正向干扰幅度高达7.9v,负向干扰幅度高达7v。如图6b所示,被动管q

l

的漏源电压v

ds2

上升过程中,100v

‑

800v的上升斜率约43.7v/ns。

如图6c所示,被动管q

l

的漏源电压v

ds2

下降过程中,800v

‑

100v的下降斜率约51.25v/ns。可见,被动管q

l

的漏源电压v

ds2

上升下降速度较快,引起q

l

栅源极电压v

gs2

的明显不稳定现象。

[0080]

如图7a至7c所示,为本实施例中采用无源抑制方法的驱动电路实验波形,主动管q

h

以及被动管q

l

的驱动电路采用并联栅源极辅助电容的办法。驱动电阻r1、r2为10ω,栅源极并联辅助电容c

a1

、c

a2

为2nf。如图7a所示,被动管q

l

栅源极电压v

gs2

的干扰振荡有一定程度的缓解,正向干扰幅度约为4v,负向干扰幅度也约为4v。如图7b所示,被动管q

l

的漏源电压v

ds2

上升过程中,100v

‑

800v的上升斜率约42.5v/ns。如图7c所示,被动管q

l

的漏源电压v

ds2

下降过程中,800v

‑

100v的下降斜率约39.6v/ns。相比图6a至图6c实施例中的开关速度,有大幅度降低,可见,采用栅源极并联辅助电容的无源栅极振荡抑制方法,虽然有效抑制了栅源极的振荡,但是却以牺牲开关速度为代价。

[0081]

如图8a至图8c所示,为本实施例中采用mosfet栅极负反馈有源驱动电路实验波形。主动管q

h

以及被动管q

l

的驱动电路均采用有源负反馈驱动。如图8a所示,被动管q

l

栅源极电压v

gs2

的干扰振荡有更大程度的缓解,正向干扰幅度约为3v,负向干扰幅度也约为3v。如图8b所示,被动管q

l

的漏源电压v

ds2

上升过程中,100v

‑

800v的上升斜率约50v/ns。如图8c所示,被动管q

l

的漏源电压v

ds2

下降过程中,800v

‑

100v的下降斜率约50v/ns。相比图7a至图7c实施例中的无源抑制方案,本实用新型所提栅极负反馈有源抑制电路可以实现更大幅度的栅源电压振荡抑制,而且,不会以牺牲开关速度为代价。在该辅助电容(20nf)设置情况下,相比图6a至图6c中实施例的开关速度,尚有一定程度的提高。

[0082]

本实用新型另一种具体实施方式:

[0083]

如图1所示,一种mosfet栅极负反馈有源驱动电路,用于连接驱动信号,进行控制被控mosfet的开和关,包括:

[0084]

驱动推挽电路,用于产生控制mosfet等宽禁带半导体器件的驱动电压v

gs

*;即提供驱动电流以驱动被控mosfet,所述驱动信号连接至所述驱动推挽电路,所述驱动推挽电路与第三节点串联;

[0085]

驱动电阻r,所述驱动电阻r一端与驱动推挽电路串联,另一端与第一节点相连,用于限制驱动推挽电路对辅助电容c的充放电电流,起限流和保护的作用;第一节点与被控mosfet源极之间的电压差为驱动电压;

[0086]

辅助电容c,所述辅助电容c一端与第一节点相连接,另一端通过第三节点与被控mosfet源极s相连接,与驱动电阻r构成无源网络,用于调节被控mosfet的开关速度;

[0087]

辅助mosfet,所述辅助mosfet为p沟道mosfet,所述辅助mosfet源极与被控mosfet栅极相连接,用于构造负反馈调节机制,所述辅助mosfet漏极连接到驱动电压;所述驱动电压为驱动芯片经过无源网络滤波后的电压;所述p沟道mosfet漏极d

p

和栅极g

p

通过第二节点与所述驱动电阻r串联,源极s

p

与被控mosfet栅极g相连接,用于构造负反馈调节机制,实现栅极电压自稳定;

[0088]

所述驱动推挽电路包括一mosfet驱动芯片、开通偏置电压v

cc

以及关断偏置电压v

ee

;所述mosfet驱动芯片输出电源正端口连接至开通偏置电压v

cc

的正极,所述mosfet驱动芯片输出电源负端口连接至关断偏置电压v

ee

的负极,所述mosfet驱动芯片的驱动输出端口连接至所述驱动电阻r的一端,所述驱动芯片的驱动输入端口连接至驱动信号;所述开通偏置电压v

cc

的负极以及关断偏置电压v

ee

的正极均连接至所述第三节点;所述驱动推挽电路

仅采用普通mosfet的驱动芯片即可,v

cc

为开通偏置电压,推荐开通偏置电压值为18~22v,v

ee

为关断偏置电压,推荐关断偏置电压值为

‑

2.5~

‑

5v,驱动芯片推荐共模瞬变抗扰度(cmti)≥100v/ns(全温度范围内)。在驱动能力上,芯片输出电流应不小于(v

cc

‑

v

ee

)/r

g

,其中r

g

为被控mosfet的栅极寄生电阻。

[0089]

所述p沟道mosfet在被控mosfet的开通和关断过程中,需承受一定的电压和电流,因此,为保证其安全工作,需根据驱动芯片设计的开通偏置电压v

cc

关断偏置电压v

ee

,以及被控mosfet栅极特性,选取辅助mosfet的电压、电流等级,推荐漏源击穿电压不小于v

cc

‑

v

ee

,且可承受的连续漏极电流不小于(v

cc

‑

v

ee

)/r

g

。同时,为保证控制精度,所述p沟道mosfet的跨导增益应远大于1(s)。

[0090]

所述辅助电容c功能上除可调节被控mosfet开关速度外,同时也可缩小驱动芯片、辅助mosfet、被控mosfet栅源极三者构成的回路面积,实现驱动回路的高频解耦。

[0091]

虽然以上描述了本实用新型的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本实用新型的范围的限定,熟悉本领域的技术人员在依照本实用新型的精神所作的等效的修饰以及变化,都应当涵盖在本实用新型的权利要求所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1