一种读卡器通讯传输线路的浪涌抑制电路的制作方法

1.本实用新型涉及读卡器领域,具体涉及一种读卡器通讯传输线路的浪涌抑制电路。

背景技术:

2.读卡器已经广泛的应用在各种生活场景中。读卡器内部涉及到各种各样的模块,其中就包括通讯模块,而在通讯模块中,如何在信号传输过程中进行浪涌防护为一个重要的问题。

技术实现要素:

3.本实用新型旨在至少解决现有技术或相关技术中存在的技术问题之一。

4.有鉴于此,本实用新型的一个目的在于提供一种读卡器通讯传输线路的浪涌抑制电路。

5.本实用新型提供一种读卡器通讯传输线路的浪涌抑制电路,所述浪涌抑制电路位于第一信号输入端、第二信号输入端和收发器之间,所述浪涌抑制电路包括第一瞬态抑制二极管、第二瞬态抑制二极管、第三瞬态抑制二极管和第四瞬态抑制二极管,以及第一保险管和第二保险管;

6.所述第一瞬态抑制二极管和第二瞬态抑制二极管顺序连接在第一信号输入端和第二信号输入端之间,第三瞬态抑制二极管和第四瞬态抑制二极管顺序连接在第一信号输入端和第二信号输入端之间;第一瞬态抑制二极管和第二瞬态抑制二极管的连接点与第三瞬态抑制二极管和第四瞬态抑制二极管的连接点共同接地;

7.所述第一保险管连接在所述第一信号输入端和所述收发器的第一差分信号端之间;所述第二保险管连接在所述第二信号输入端和所述收发器的第二差分信号端之间。

8.进一步的,所述第一和第二瞬态抑制二极管为bep0080tb

‑

mc型号,所述第三和第四瞬态抑制二极管为smf13ca型号。

9.进一步的,所述第一保险管和第二保险管为jk

‑

nsmd010型号。

10.进一步的,所述浪涌抑制电路还包括第一电容、第二电容和第三电容,第一电感和第二电感;

11.所述第一电容的一端和第二电容的一端连接,其连接点接地;所述第三电容,与第一电容和第二电容的连接电路的两端连接;

12.所述第一电容的另一端和第一电感的一端连接,所述第二电容的另一端和第一电感的一端连接;

13.所述第一保险管经过所述第一电感后,所述第一电感的另一端与所述第一差分信号端连接;所述第二保险管经过所述第二电感后,所述第二电感的另一端与所述第二差分信号端连接。

14.进一步的,第一电容、第二电容和第三电容的数值为15pf。

15.进一步的,第一电感和第二电感的数值为220uh。

16.本实用新型的有益效果是:浪涌抑制电路起到防浪涌输入以及防感应雷输入,保护后级芯片的安全。

附图说明

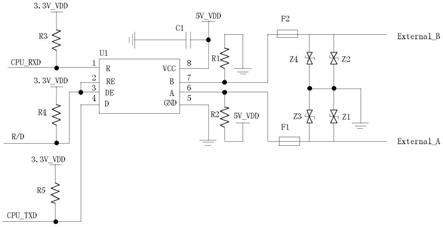

17.图1示出了根据本实用新型的一个实施例的浪涌抑制电路的电路原理图;

18.图2示出了根据本实用新型的又一个实施例的浪涌抑制电路的电路原理图。

具体实施方式

19.为了可以更清楚地理解本实用新型的上述目的、特征和优点,下面结合附图和具体实施方式对本实用新型进行进一步的详细描述。需要说明的是,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

20.在下面的描述中阐述了很多具体细节,以便于充分理解本实用新型,但是本实用新型还可以采用其他不同于在此描述的其他方式来实施,因此,本实用新型的保护范围并不受下面公开的具体实施例的限制。

21.下面参照图1描述本实用新型的一些实施例。

22.在读卡器的使用过程中,需要将门禁采集到的数据进行通信传输。相关技术中,采用rs485通讯方式进行数据传输,以获得稳定高效的传输效果。

23.如图1所示,处理器(图中未明示)通过收发器u1与浪涌抑制电路连接,浪涌抑制电路的另一端连接外围设备,比如接线端子排(图中未明示),来接收需要通讯传输的信号。

24.收发器u1采用sp485een

‑

l/tr收发器,其具有8个端口。第一端口r为接收器输出端,第四端口d为驱动器输入端,第二端口re为接收器使能端,第三端口de为驱动器使能端。

25.第一端口r通过第三电阻r3和电源3.3v_vdd连接。第四端口d通过第五电阻r5和电源3.3v_vdd连接。第二端口re和第三端口de连接后,通过第四电阻r4与第一电源3.3v_vdd连接。

26.第一端口r、第二端口re和第三端口de连接后的公共端、第四端口d均与处理器连接,如图1所示,分别与处理器cpu的cpu_rxd端、r/d端、cpu_txd端连接。

27.第五端口gnd为接地端,与地连接;第八端口vcc为电源端,与第二电源5v_vdd连接,同时,通过第一电容c1接地。第六端口a和第七端口b分别为第一差分信号端和第二差分信号端,第六端口a通过第二电阻r2与第二电源5v_vdd连接,第七端口b通过第一电阻r1接地。

28.信号经第一信号输入端和第二信号输入端,比如图1中的external_a和external_b端,进入浪涌抑制电路,然后输入至收发器u1。

29.浪涌抑制电路包括瞬态抑制二极管z1

‑

z4和保险管f1

‑

f2,第一瞬态抑制二极管z1和第二瞬态抑制二极管z2顺序连接在第一信号输入端和第二信号输入端之间,第三瞬态抑制二极管z3和第四瞬态抑制二极管z4顺序连接在第一信号输入端和第二信号输入端之间;z1和z2的连接点与z3和z4的连接点共同接地。

30.瞬态抑制二极管z1

‑

z4可选为双向瞬态二极管,比如,z1和z2选择bep0080tb

‑

mc型号,z3和z4选择smf13ca。

31.浪涌抑制电路还包括第一保险管f1和第二保险管f2。两路信号经瞬态抑制二极管z1

‑

z4后,分别经过第一保险管f1和第二保险管f2与收发器u1的第六端口a和第七端口b连接。f1和f2可选择型号jk

‑

nsmd010。

32.上述浪涌抑制电路起到防浪涌输入以及防感应雷输入,保护后级芯片的安全。

33.图1所述的浪涌抑制电路为一级电路,为了增强抑制效果,如图2所示增加多一级抑制电路,使得抑制效果更好,增强了信号传输过程中的抗干扰能力。图2所示的浪涌抑制电路除了包括与图1中相同的第一级浪涌抑制电路110外,还包括第二级浪涌抑制电路120。

34.第二级浪涌抑制电路120包括:电容c1、c2和c3,电感l1和l2。该部分电路连接在第一级浪涌抑制电路与收发器u1的第六端口a和第七端口b之间,起到加强抑制的效果,尤其对于信号传输过程中的干扰信号具有很好的抑制作用。因此图2所示的两级浪涌抑制电路具有很好的防雷和防干扰的作用。具体的,第二级浪涌抑制电路中,第一电容c1和第二电容c2连接,其连接点接地;第三电容c3与第一电容c1和第二电容c2的连接电路的两端连接,第一电感l1和第二电感l2分别与第三电容的两端连接后,第一电感l1的另一端和第二电感l2的另一端分别连接第六端口a和第七端口b。

35.第一电容c1、第二电容c2和第三电容c3的数值可选择为15pf,第一电感l1和第二电感l2的数值可选择为220uh。

36.上述浪涌抑制电路,通过两级电路配合,包括电路中各元件的参数和选型的配合,使得第一级浪涌抑制电路能够对感应雷等较大能量的浪涌输入有效抑制,同时使得第二级浪涌抑制电路能够对其它干扰信号等较小能量的干扰有效抑制,保护后级芯片的安全。其中的保险管具有退耦作用,有利于两级电路的配合;电感具有抑制干扰的作用。

37.在本实用新型中,术语“第一”、“第二”、“第三”仅用于描述的目的,而不能理解为指示或暗示相对重要性;术语“多个”则指两个或两个以上,除非另有明确的限定。术语“安装”、“相连”、“连接”、“固定”等术语均应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或一体地连接;“相连”可以是直接相连,也可以通过中间媒介间接相连。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型中的具体含义。

38.本实用新型的描述中,需要理解的是,术语“上”、“下”、“左”、“右”、“前”、“后”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或单元必须具有特定的方向、以特定的方位构造和操作,因此,不能理解为对本实用新型的限制。

39.在本说明书的描述中,术语“一个实施例”、“一些实施例”、“具体实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或特点包含于本实用新型的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或实例。而且,描述的具体特征、结构、材料或特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

40.以上仅为本实用新型的优选实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1