一种面向氮化镓晶体管的半桥负压驱动电路

1.本发明涉及电力电子技术领域,尤其涉及面向氮化镓晶体管的半桥负压驱动电路。

背景技术:

2.氮化镓高电子迁移率晶体管作为第三代宽禁带半导体器件,具有变换效率高,工作频率高等一系列优势,但由于其阈值电压小,开关速度快,易导致开关过程中的误导通,进而影响氮化镓晶体管的工作效果和器件寿命,因此,氮化镓晶体管在工作时对驱动电路的要求十分严格。而传统的驱动电路虽然在体积、成本方面有一定优势,但由于没有负压驱动,易使得氮化镓晶体管在开关过程中的反复导通而影响器件正常工作。

3.除此之外,对于使用氮化镓晶体管的半桥电路,其工作过程中的串扰电流及因此而引起的电压尖峰也是影响电路正常工作的一个重要原因,目前常见的如并联外部电容等方法在抑制串扰的同时,也降低了氮化镓晶体管的开关速度,实际应用价值不大,因此,为半桥电路的串扰电流提供了一条低阻抗回路,提高半桥电路的抗干扰性,是氮化镓晶体管大规模应用的一个亟待解决的问题。

技术实现要素:

4.根据以上技术问题,本发明提供一种解决传统的氮化镓半桥驱动电路存在的无负压驱动、串扰电流较严重等易引起氮化镓晶体管失效问题的面向氮化镓晶体管的半桥负压驱动电路。

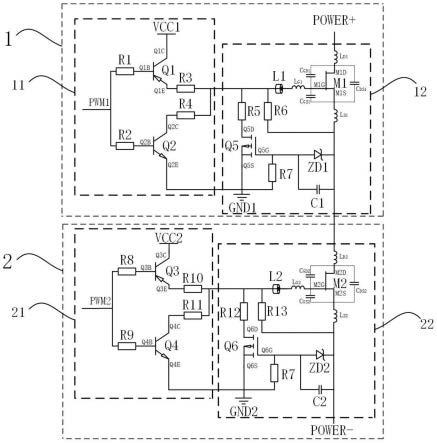

5.本发明提供一种面向氮化镓晶体管的半桥负压驱动电路,其特征在于包括第一驱动回路1、第二驱动回路2、氮化镓晶体管m1以及氮化镓晶体管m2,所述第一驱动回路1包括第一信号放大电路11和第一负压产生电路12,所述第二驱动回路2包括第二信号放大电路21 和第二负压产生电路22,所述第一驱动回路1用于驱动氮化镓晶体管m1,所述第二驱动回路2用于驱动氮化镓晶体管m2,所述氮化镓晶体管m1,作为半桥电路上桥臂,其中漏极m1d接功率回路的电源正极power+,用于为半桥电路提供功率;所述氮化镓晶体管m2,作为半桥电路下桥臂,其中漏极m2d接氮化镓晶体管m1的源极m1s,源极m2s接功率回路的电源负极power-,用于形成半桥电路的功率回路。

6.所述驱动信号放大电路11主要由功率开关管q1、q2、电阻r1 和r2组成,驱动信号pwm1经电阻r1、r2分别与功率开关管q1和 q2的基极q1b、q2b相连接,功率开关管q1的集电极q1c接第一驱动回路的信号电源正极vcc1,发射极q1e接电阻r3,功率开关管q2 的集电极q2c接电阻r4,发射极q2e接第一驱动回路的信号电源地 gnd1,r3和r4的另一端短接;所述第一负压产生电路12主要由电阻r5、r6、r7,磁珠l1,功率开关管q5,稳压管zd1及电容c1组成;所述电阻r3、r4另一端短接后,经电阻r5与功率开关管q5的漏极q5d连接,功率开关管q5的源极q5s与第一驱动回路的信号地 gnd1连接;所述电阻r3、r4另一端短接后,经磁珠l1与氮化镓功率管m1的栅极m1g连接,经电阻r6与氮化镓功率管m1的源极m1s 连接;所述稳压管

zd1和电容c1并联后,稳压管zd1负极与氮化镓晶体管m1的源极m1s连接,另外一端在接入功率开关管q5的栅极 q5g的同时,与电阻r7连接后接入第一驱动回路的信号地gnd1。

7.所述驱动信号放大电路21主要由功率开关管q3、q4,电阻r8、 r9组成,驱动信号pwm2经电阻r8和电阻r9分别与功率开关管q3、 q4的栅极q3b、q4b相连接,功率开关管q3的集电极q3c接第二驱动回路的信号电源正极vcc2,发射极q3e接电阻r10,功率开关管 q4的集电极q4c接电阻r11,发射极q3e接第二驱动回路的信号电源地gnd1,电阻r10、r11的另一端短接;所述第二负压产生电路22 主要由电阻r12、r13、r14,磁珠l2,功率开关管q6,稳压管zd2 及电容c2组成;所述电阻r10、r11另一端短接后,经电阻r12与功率开关管q5的漏极q6d连接,q5的源极q6s与第二驱动回路的信号地gnd2连接;所述电阻r10、r11另一端短接后,经磁珠l2与氮化镓功率管m2的栅极m2g连接,经电阻r13与氮化镓功率管m2的源极 m2s连接;所述稳压管zd2和电容c2并联后,zd2负极与氮化镓晶体管m2的源极m2s连接,另外一端在接入功率开关管q6的栅极q6s的同时,与电阻r14连接后接入第二驱动回路的信号地gnd2。

8.本发明的有益效果为:本发明为面向氮化镓晶体管的半桥负压驱动电路,相对于传统的氮化镓驱动电路,本发明能够在氮化镓关断时,以小于零的驱动电压使其快速关断,且为半桥电路的串扰电流提供了一条低阻抗回路,有效的抑制了电压尖峰,提高了半桥电路的抗干扰性,从而有效的保证了氮化镓晶体管开关过程的稳定性。

附图说明

9.图1为本发明专利的半桥负压驱动电路示意图;

10.图2为图1所示的负压驱动电路的上管工作时开通过程示意图;

11.图3为图1所示的负压驱动电路的上管工作时关断过程示意图;

12.图4为图1所示的负压驱动电路上管工作过程波形示意图;

13.图5为图1所示的负压驱动电路上管工作过程仿真波形示意图;

14.图6为图1所示的负压驱动电路上管实际工作时开通瞬间振荡波形示意图。

具体实施方式

15.下面将结合本发明的附图,对本发明的技术方案进行清楚完整地描述。

16.本发明提供一种面向氮化镓晶体管的半桥负压驱动电路,其特征在于包括第一驱动回路1、第二驱动回路2、氮化镓晶体管m1以及氮化镓晶体管m2,第一驱动回路1包括第一信号放大电路11和第一负压产生电路12,第二驱动回路2包括第二信号放大电路21和第二负压产生电路22,第一驱动回路1用于驱动氮化镓晶体管m1,第二驱动回路2用于驱动氮化镓晶体管m2,氮化镓晶体管m1,作为半桥电路上桥臂,其中漏极m1d接功率回路的电源正极power+,用于为半桥电路提供功率;所述氮化镓晶体管m2,作为半桥电路下桥臂,其中漏极m2d接氮化镓晶体管m1的源极m1s,源极m2s接功率回路的电源负极power-,用于形成半桥电路的功率回路。

17.驱动信号放大电路11主要由功率开关管q1、q2、电阻r1和r2 组成,驱动信号pwm1经电阻r1、r2分别与功率开关管q1和q2的基极q1b、q2b相连接,功率开关管q1的集电极q1c接第一驱动回路的信号电源正极vcc1,发射极q1e接电阻r3,功率开关管q2的集电极 q2c接

电阻r4,发射极q2e接第一驱动回路的信号电源地gnd1,r3 和r4的另一端短接;第一负压产生电路12主要由电阻r5、r6、r7,磁珠l1,功率开关管q5,稳压管zd1及电容c1组成;电阻r3、r4 另一端短接后,经电阻r5与功率开关管q5的漏极q5d连接,功率开关管q5的源极q5s与第一驱动回路的信号地gnd1连接;电阻r3、 r4另一端短接后,经磁珠l1与氮化镓功率管m1的栅极m1g连接,经电阻r6与氮化镓功率管m1的源极m1s连接;稳压管zd1和电容 c1并联后,稳压管zd1负极与氮化镓晶体管m1的源极m1s连接,另外一端在接入功率开关管q5的栅极q5g的同时,与电阻r7连接后接入第一驱动回路的信号地gnd1。

18.驱动信号放大电路21主要由功率开关管q3、q4,电阻r8、r9 组成,驱动信号pwm2经电阻r8和电阻r9分别与功率开关管q3、q4 的栅极q3b、q4b相连接,功率开关管q3的集电极q3c接第二驱动回路的信号电源正极vcc2,发射极q3e接电阻r10,功率开关管q4的集电极q4c接电阻r11,发射极q3e接第二驱动回路的信号电源地 gnd1,电阻r10、r11的另一端短接;第二负压产生电路22主要由电阻r12、r13、r14,磁珠l2,功率开关管q6,稳压管zd2及电容c2 组成;电阻r10、r11另一端短接后,经电阻r12与功率开关管q5的漏极q6d连接,q5的源极q6s与第二驱动回路的信号地gnd2连接;所述电阻r10、r11另一端短接后,经磁珠l2与氮化镓功率管m2的栅极m2g连接,经电阻r13与氮化镓功率管m2的源极m2s连接;稳压管zd2和电容c2并联后,zd2负极与氮化镓晶体管m2的源极m2s 连接,另外一端在接入功率开关管q6的栅极q6s的同时,与电阻r14 连接后接入第二驱动回路的信号地gnd2。

19.实施例

20.参考图1至图4,驱动整体工作过程分为以下四个阶段:

21.阶段一:如图4所示,t0到t1期间,第一驱动回路1的第一驱动信号放大电路11的输入pwma信号为高,npn型三极管q1导通, pnp型三极管q2关断,此时第一驱动信号放大电路经vcc1、q1、r3 输出一个正的驱动信号pwma1;在第一负压产生电路中,电流由磁环 l1、氮化镓晶体管m1、并联的稳压管zd1与电容c1、r7流向第一驱动回路的gnd1,此时电容c1两端电压为稳压管zd1两端的稳压值vzd1,功率开关管q5由于栅源极电压为r7两端电压,为正值而处于关断状态。氮化镓晶体管栅源极电压为vcc1-vzd1,处于开通状态,此时电流流向如图2所示。此时第二驱动回路与阶段二的第一驱动回路工作状态相似,氮化镓晶体管m1栅源极电压为-vzd1,处于关断状态。

22.阶段二:如图4所示,t1到t2期间,第一驱动回路1的第一驱动信号放大电路11的输入pwma信号为低,npn型三极管q1关断, pnp型三极管q2导通,第一驱动信号放大电路经gnd1、q2、r4输出的驱动信号pwma为0。此时由于功率开关管q5的栅极q5g与电容c1 的负压端-vzd1相连接,此时功率开关管q5导通,氮化镓晶体管的栅极电荷经磁环l1、电阻r5、功率开关管q5、gnd1、电阻r7、电容 c1进行泄放,此时氮化镓晶体管m1的栅源极电压为-vzd1,从而保证了氮化镓晶体管m1的安全关断,此时电荷泄放通道如图3所示。此时第二驱动回路与阶段二的第一驱动回路工作状态相似,氮化镓晶体管m2栅源极电压为-vzd2,处于关断状态。

23.阶段三:如图4所示,t2到t3期间,第一驱动回路与阶段二的第一驱动回路工作状态相似,氮化镓晶体管m1栅源极电压为-vzd1,处于关断状态。第二驱动回路与阶段一的第一驱动回路工作状态相似,氮化镓晶体管m2栅源极电压为vcc2-vzd2,处于开通状态。

24.阶段四:如图4所示,t3到t4期间,第一驱动回路与阶段二的第一驱动回路工作状

态相似,氮化镓晶体管m1栅源极电压为-vzd1,处于关断状态。第二驱动回路与阶段二的第一驱动回路工作状态相似,氮化镓晶体管m2栅源极电压为-vzd2,处于关断状态。

25.参阅图5,是以上四个阶段的ltspice仿真波形图。根据仿真波形图,可以看出波形是符合以上四个工作阶段的。

26.如图1及图6所示,以第一驱动回路为例,在器件导通时,驱动电阻为r3,驱动回路的栅极寄生电感为lg1,源极寄生电感为ls1,栅源极寄生电感为cgs1,由于开通过程中的振荡,此时r3、lg1、ls1、 cgs1应满足以下两个公式:

27.关断过程中的电阻r4计算公式与上式类似。

28.在其中一种实施方式中,氮化镓晶体管m1以及氮化镓晶体管m2 也可为sic mos或si mos或igbt。

29.在其中一种实施方式中,功率开关管q1、q2、q3、q4、q5、q6 可为三极管或者mosfet管。

30.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1