内埋式线路板及其制作方法与流程

1.本发明涉及内埋式线路板技术领域,尤其涉及内埋式线路板及其制作方法。

背景技术:

2.近年来,电子产品被广泛应用在日常工作和生活中,轻、薄、小的电子产品越来越受到欢迎。线路板作为电子产品的主要部件,其占据了电子产品的较大空间,因此线路板的体积在很大程度上影响了电子产品的体积,大体积的线路板势必难以符合电子产品轻、薄、短、小之趋势。其中,内埋式线路板主要是将电子组件嵌埋至线路板内部,从而使线路板模块实现小型化,缩短组件之间的连接路径,降低传输损失,内埋式线路板是可以实现便携式电子设备更小更轻便,多功能化和高性能化的一种技术途径。

3.其中,业内通常采用预先设置覆盖整个基材的电阻材料层,然后开设内埋凹槽,随后对电阻材料层进行蚀刻的方式制作内埋电阻。该方法中设置于基材表面的金属层往往为一整面,但最后形成电阻的电阻材料层只占其中一小部分,使得原材料损耗较大。且,该制程中,电阻材料层在预制过程中与制作走线的导电材料层堆叠设置,由于材料及工艺问题使得其会对走线的传输损耗造成负面影响;且,电阻的制作公差往往由蚀刻制程的精度决定。

4.如何解决上述问题,是本领域技术人员需要考虑的。

技术实现要素:

5.有鉴于此,本发明提供一种内埋式线路板的制作方法,包括如下步骤:

6.提供一第一基材,所述第一基材包括一第一表面,在所述第一表面形成一孔槽,所述孔槽暴露的表面为第二表面;

7.在所述第一基材形成有所述孔槽一侧形成一电阻材料层,保留位于所述第二表面的所述电阻材料层形成一内埋电阻,去除未设置于所述第二表面的电阻材料层;

8.在所述第一基材形成有所述孔槽一侧形成一掩膜,所述掩膜包括第一子掩膜,所述第一子掩膜设置于所述孔槽内并将所述孔槽分割为间隔的第一子槽及第二子槽;以及

9.在所述第一子槽及所述第二子槽内分别形成一个导电接脚。

10.于一实施例中,形成所述孔槽的步骤包括:

11.在所述第一基材表面设置一干膜;

12.对所述干膜进行曝光、显影、蚀刻使所述第一表面的至少部分裸露;以及

13.使用等离子体蚀刻工艺对所述第一表面裸露的部分进行蚀刻得到所述孔槽。

14.于一实施例中,使用物理镀膜或化学镀膜的方式在所述第一基材形成有所述孔槽一侧形成所述电阻材料层;

15.使所述电阻材料覆盖所述第二表面以及所述干膜远离所述第一表面一侧;以及

16.去除所述干膜以去除附着于所述干膜表面的所述电阻材料。

17.于一实施例中,所述掩膜还包括一第二子掩膜,所述第二子掩膜设置于所述第一

表面;

18.所述第二子掩膜上形成有一贯穿所述第二子掩膜的线路开口;

19.使用等离子体蚀刻工艺对由所述线路开口暴露的所述第一表面进行蚀刻得到一线路槽;以及

20.使用物理镀膜或化学镀膜的方式在所述孔槽及所述线路槽中设置导电单元。

21.于一实施例中,还包括如下步骤:

22.去除所述掩膜;

23.对所述导电单元进行图案化处理形成设置于所述线路槽中的导电线路及设置于所述孔槽中的所述导电接脚;以及

24.在所述第一基材设置有所述导电线路一侧形成一覆盖层。

25.于一实施例中,所述电阻材料完全覆盖所述第二表面,所述电阻材料包括元素镍、元素铬或元素钛中的至少一种。

26.本发明还提供一种内埋式线路板,包括:

27.第一基材,所述第一基材上开设有至少一个孔槽;

28.内埋电阻,所述内埋电阻设置于所述孔槽内;以及

29.导电接脚,两个所述导电接脚间隔设置于所述孔槽内,所述导电接脚设置于所述内埋电阻远离所述第一基材的表面。

30.于一实施例中,所述第一基材上开设有线路槽,所述线路槽中设置有导电线路,所述导电线路与所述导电接脚电性连接,两个所述导电接脚之间的间距范围为1μm至25μm。

31.于一实施例中,所述内埋电阻覆盖所述孔槽的表面,所述内埋电阻的材料包括元素镍、元素铬或元素钛中的至少一种,所述内埋电阻的厚度范围为0.03μm至1μm。

32.于一实施例中,还包括覆盖层,所述覆盖层覆盖所述内埋电阻未被所述导电接脚覆盖的表面。

33.相比于现有技术,本发明的内埋式线路板及其制作方法,相较于传统电阻材料均一放置于导体铜层下,本发明的内埋式线路板不仅能实现对大功率的承受,且不会影响同层射频讯号走线的损耗,易于实现元器件小型化的优点。

附图说明

34.图1为本发明一实施例的内埋式线路板的局部俯视示意图。

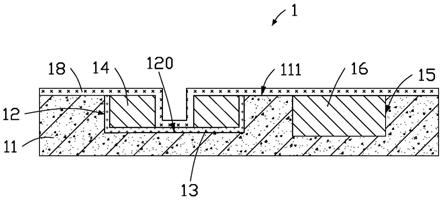

35.图2为本发明一实施例的内埋式线路板的局部截面示意图。

36.图3为本发明一实施例的内埋式线路板的制作流程示意图。

37.图4为本发明一实施例的内埋式线路板的制作流程示意图。

38.图5为本发明一实施例的内埋式线路板的制作流程示意图。

39.图6为本发明一实施例的内埋式线路板的制作流程示意图。

40.图7为本发明一实施例的内埋式线路板的制作流程示意图。

41.图8为本发明一实施例的内埋式线路板的制作流程示意图。

42.图9为本发明一实施例的内埋式线路板的制作流程示意图。

43.图10为本发明一实施例的内埋式线路板的制作流程示意图。

44.图11为本发明一实施例的内埋式线路板的制作流程示意图。

45.图12为本发明一实施例的内埋式线路板的制作流程示意图。

46.图13为本发明一实施例的内埋式线路板的制作流程示意图。

47.主要元件符号说明

48.内埋式线路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ149.第一基材

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11

50.第一表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

111

51.孔槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

52.第一子槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

121

53.第二子槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122

54.第二表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

120

55.内埋电阻

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13

56.导电接脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

57.线路槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15

58.导电线路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

16

59.干膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21

60.电阻材料

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22

61.掩膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23

62.第一子掩膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

231

63.第二子掩膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

232

64.线路开口

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24

65.导电单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

25

66.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

67.以下描述将参考附图以更全面地描述本发明内容。附图中所示为本发明的示例性实施例。然而,本发明可以以许多不同的形式来实施,并且不应该被解释为限于在此阐述的示例性实施例。提供这些示例性实施例是为了使本发明透彻和完整,并且将本发明的范围充分地传达给本领域技术人员。类似的附图标记表示相同或类似的组件。

68.本文使用的术语仅用于描述特定示例性实施例的目的,而不意图限制本发明。如本文所使用的,除非上下文另外清楚地指出,否则单数形式“一”,“一个”和“该”旨在也包括复数形式。此外,当在本文中使用时,“包括”和/或“包含”或“包括”和/或“包括”或“具有”和/或“具有”,整数,步骤,操作,组件和/或组件,但不排除存在或添加一个或多个其它特征,区域,整数,步骤,操作,组件,组件和/或其群组。

69.除非另外定义,否则本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。此外,除非文中明确定义,诸如在通用字典中定义的那些术语应该被解释为具有与其在相关技术和本发明内容中的含义一致的含义,并且将不被解释为理想化或过于正式的含义。

70.以下内容将结合附图对示例性实施例进行描述。须注意的是,参考附图中所描绘的组件不一定按比例显示;而相同或类似的组件将被赋予相同或相似的附图标记表示或类

似的技术用语。

71.下面参照附图,对本发明的具体实施方式作进一步的详细描述。

72.如图1及图2所示,本发明实施例提供一种内埋式线路板1,内埋式线路板1包括第一基材11、内埋电阻13、导电接脚14以及导电线路16,第一基材11上形成有至少一个孔槽12以及至少一个线路槽15,内埋电阻13及导电接脚14设置于孔槽12内,内埋电阻13设置于第一基材11与导电接脚14之间,导电线路16设置于线路槽15中,导电线路16与导电接脚14电性连接。

73.第一基材11包括第一表面111,孔槽12及线路槽15开设于第一表面111,孔槽12及线路槽15由第一表面111向内凹陷形成。于一实施例中,孔槽12及线路槽15的深度范围可以为5μm至25μm,具体可以为20μm。

74.于一实施例中,第一基材11可以为绝缘材料,例如聚酰亚胺或聚丙烯等。于一实施例中,第一基材11可以为透明材料或不透明材料。于一实施例中,第一基材11可以为柔性材料或非柔性材料。

75.孔槽12包括第二表面120,第二表面120为孔槽12的内壁,例如可以包括孔槽12的底壁和侧壁。于一实施例中,内埋电阻13设置于孔槽12内,具体的,内埋电阻13可以完全覆盖第二表面120。

76.于一实施例中,内埋电阻13的材料可以包括元素镍、元素铬或元素钛中的至少一种,例如可以为金属镍、金属铬或金属钛的单质、合金或者盐类。于一实施例中,内埋电阻的厚度范围可以为0.03μm至1μm。

77.于一实施例中,两个导电接脚14间隔设置于孔槽12内,导电接脚14设置于内埋电阻13远离第一基材11的表面,两个导电接脚之间的间距范围为1μm至25μm。

78.于一实施例中,每个导电接脚14均可分别与导电线路16电性连接,导电线路16及导电接脚14内埋于第一基材11内,通过内埋设置可以降低同层导电线路16或导电线路16与其他同层电子元件之间的讯号干扰。

79.于一实施例中,导电接脚14设置于整面的内埋电阻13远离第一基材11一侧,即,内埋电阻13设置于导电接脚14与第一基材11之间,使得导电接脚14与第一基材11间隔设置。

80.内埋电阻13不仅可以实现对大功率的承受,且不会影响同层射频讯号走线的损耗,易于实现元器件小型化的优点。

81.内埋式线路板1还包括覆盖层18,覆盖层18覆盖内埋电阻13未被导电接脚14覆盖的第二表面120,以及导电接脚14裸露的表面,以及第一表面111,以及导电线路16裸露的表面。于一实施例中,覆盖层18可以为阻焊层或防焊层,覆盖层18的材质可以为油墨。

82.覆盖层18可以通过印刷、喷涂、镀膜等多种形式制作,覆盖层18一方面可保护内埋式线路板1不因物理接触而破坏,另一方面还能为内埋式线路板1提供电磁屏蔽或绝缘屏蔽等电磁防护。

83.于一实施例中,覆盖层18覆盖上述表面前,还可在第一基材11上设置其他电子元件,例如电容单元或电感单元,或可以在第一基材11上增层。在其他实施例中,可以在覆盖层18远离第一基材11的表面进行增层或设置电性元件或进行蚀刻开设其他结构。

84.如图3至图13所示,本发明实施例还提供一种内埋式线路板1的制作方法,包括如下步骤:

85.步骤s1:提供一第一基材11,第一基材11包括一第一表面111,在第一表面111形成一孔槽12,孔槽12暴露的表面为第二表面120。

86.具体可包括如下步骤:

87.步骤s11:如图4所示,在第一基材11表面设置一干膜21。

88.在其他实施例中,干膜21可替换为可重复使用的掩膜。

89.步骤s12:如图5所示,对干膜21进行曝光、显影、蚀刻使第一表面111的至少部分裸露。

90.于一实施例中,可使用黄光显影支撑对干膜21进行蚀刻,可有效控制蚀刻精度。

91.步骤s13:如图6所示,使用等离子体蚀刻工艺对第一表面111裸露的部分进行蚀刻得到孔槽12。

92.于一实施例中,孔槽12的深度范围可以为5μm至25μm,具体可以为20μm,使用等离子体蚀刻可有效控制蚀刻精度,孔槽12的可控深度小于1μm。

93.步骤s2:在第一基材11形成有孔槽12一侧形成一电阻材料层22,保留位于第二表面120的电阻材料层22形成一内埋电阻13,去除未设置于第二表面120的电阻材料22。

94.步骤s21:如图7所示,使用物理镀膜或化学镀膜的方式在第一基材11形成有孔槽12一侧形成电阻材料22。

95.于一实施例中,电阻材料22覆盖第二表面120以及干膜21远离第一基材11一侧。

96.于一实施例中,电阻材料22完全覆盖第二表面120,电阻材料22包括元素镍、元素铬或元素钛中的至少一种。

97.步骤s22:如图7及图8所示,去除干膜21以去除附着于干膜21表面的电阻材料22,设置于孔槽12内部的电阻材料22被保留形成内埋电阻13。

98.步骤s3:在第一基材11形成有孔槽12一侧形成一掩膜23,掩膜23包括第一子掩膜231,第一子掩膜231设置于孔槽12内并将孔槽12分割为间隔的第一子槽121及第二子槽122。

99.步骤s31:如图9所示,掩膜23包括第一子掩膜231及第二子掩膜232,第二子掩膜232设置于第一表面111,第二子掩膜232上形成有一贯穿第二子掩膜232的线路开口24。

100.于一实施例中,掩膜23可以为可重复使用的掩膜。

101.于一实施例中,第一子掩膜231可设置于孔槽12中间区域,第一子掩膜231的宽度可大于20μm。

102.步骤s32:如图10所示,使用等离子体蚀刻工艺对由线路开口24暴露的第一表面111进行蚀刻得到一线路槽15。

103.步骤s33:如图11所示,使用物理镀膜或化学镀膜的方式在孔槽12及线路槽15中设置导电单元25。

104.于一实施例中,导电单元25的材料可以为铜,在其他实施例中,导电单元25的材料还可以为金属银或金,或具备导电能力的合金或金属复合物。

105.于一实施例中,在第一子槽121及第二子槽122内分别设置导电单元25。

106.步骤s4:如图12所示,去除掩膜23,并对导电单元25进行图案化处理形成设置于线路槽15中的导电线路16及设置于孔槽12中的导电接脚14。

107.步骤s5:如图13所示,在第一基材11设置有导电线路16一侧形成一覆盖层18。

108.于一实施例中,覆盖层18覆盖内埋电阻13未被导电接脚14覆盖的表面,以及导电接脚14裸露的表面,以及第一表面111,以及导电线路16裸露的表面。于一实施例中,覆盖层18可以为阻焊层或防焊层,覆盖层18的材质可以为油墨,可通过印刷的方式形成覆盖层18。

109.于一实施例中,可在第一基材11表面形成一种子层,该种子层可用于作为物理镀膜或化学镀膜等制成中薄膜的生长基础,该种子层在蚀刻或物理镀膜或化学镀膜的过程中可被去除。

110.上文中,参照附图描述了本发明的具体实施方式。但是,本领域中的普通技术人员能够理解,在不偏离本发明的精神和范围的情况下,还可以对本发明的具体实施方式作各种变更和替换。这些变更和替换都落在本发明所限定的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1