基于嵌入型电极的超高频谐振器的制作方法

[0001]

本发明涉及谐振器技术领域,尤其涉及一种基于嵌入型电极的超高频谐振器。

背景技术:

[0002]

5g/6g时代已经到来,无线与移动通信系统的发展又一次被推上了时代前沿,这对多频段高频滤波器的祈求急剧增加,滤波器的性能取决于其谐振器的性能,从而对压电谐振器的性能提出了更高的要求。就谐振器本身而言,其最关键的性能为机电耦合系数和品质因子(q值)。谐振器的机电耦合系数决定了滤波器的带宽,其品质因子直接影响其带内插损和滤波器裙边的陡峭性。因此,实现高品质因子的谐振器组件对低插入损耗、陡峭的滤波器裙边,高的带外抑制的滤波器起着至关重要的作用。

[0003]

声表面波谐振器(surface acoustic wave resonator)和体声波谐振器(bulk acoustic wave resonator)凭借其特有的优势,在主流市场中占据主导地位。但是,声表面波(saw)谐振器由于其相速度低、光刻存在限制等原因,在高频段很难保持优良的性能。体波谐振器(baw)由于其插入损耗低、功率处理能力好而被广泛应用于高频市场,特别是其中的薄膜体声波谐振器(fbar),具有高品质因数(q)和高机电耦合系数(k

2eff

)。然而,fbar的谐振频率是由压电薄膜的厚度决定的,因此很难在单片晶圆上实现多频段集成。兰姆波谐振器(lwr)的提出,可以突破saw所面对的频率限制,同时通过调节叉指的间距可以获得不同频率的兰姆波谐振器,从而实现同一晶圆的调频,但是兰姆波谐振器的低品质因数一直是限制其大规模普及的关键因素。

技术实现要素:

[0004]

本发明提供一种基于嵌入型电极的超高频谐振器,将电极的部分或全部沉积在压电层中,使得在压电层中的电场得到增强并分布更加均匀,使得压电层厚度方向与横向方向的电场产生更强的耦合效应,从而使得谐振器的品质因数与机电耦合系数增加。

[0005]

根据本发明实施例的一方面,一种超高频谐振器电极的部分或全部嵌在压电层中,以增加所述谐振器的品质因数与机电耦合系数。

[0006]

在一些示例中,所述电极嵌入所述压电层的深度占所述压电层厚度的1%到100%之间。

[0007]

在一些示例中,所述电极截面形状为圆形、椭圆形、规则多边形或不规则多边形。

[0008]

在一些示例中,所述压电层截面形状为圆形、规则多边形或不规则多边形。

[0009]

在一些示例中,所述电极相邻的两个的间距大于二倍声波波长。

[0010]

在一些示例中,所述电极的材料为铂、钼、铜、铝或金。

[0011]

在一些示例中,所述压电层材料为铌酸锂、钽酸锂或氮化铝。

[0012]

在一些示例中,所述电极的排列方式为规则图形或不规则图形。

附图说明

[0013]

为了更清楚地说明本发明实施例的技术方案,下面将对实施例的附图作简单地介绍。

[0014]

图1为现有技术的兰姆波谐振器的截面结构示意图。

[0015]

图2为本发明第一实施例提供的基于嵌入型电极的超高频谐振器的截面结构示意图。

[0016]

图3为本发明第二实施例提供的基于嵌入型电极的超高频谐振器的截面结构示意图。

[0017]

图4为本发明第三实施例提供的基于嵌入型电极的超高频谐振器的俯视图。

[0018]

图5为本发明第四实施例提供的基于嵌入型电极的超高频谐振器的俯视图。

[0019]

图6为本发明第五实施例提供的基于嵌入型电极的超高频谐振器的俯视图。

[0020]

图7为本发明一实施例提供的截面形状为长方形的电极全部嵌入截面形状为正方形的压电层的谐振器的阻抗曲线示意图。

[0021]

图8为本发明另一实施例提供的现有技术谐振器的阻抗曲线,以及截面形状为圆形的电极2/3嵌入截面形状为正方形的压电层的谐振器的阻抗曲线示意图。

具体实施方式

[0022]

图1为现有技术的二维兰姆波谐振器的截面结构示意图。如图1所示,压电层103设置在衬底104上,在压电层103的上表面布置排布均匀的电极101,102,电极101,102分为两组:一组施加正电压,称作正电极102;另一组施加负电压,称为负电极101,他们都分布在压电层103的表面。

[0023]

本发明提供一种基于嵌入型电极的超高频谐振器,将电极101,102的部分或全部沉积在压电层103中。图2展示了电极101,102完全嵌入到压电层103内的超高频谐振器的截面结构示意图。图3展示了电极101,102的部分嵌入到压电层103内的超高频谐振器的截面结构示意图。本发明并不限定电极101,102嵌入到压电层103内的深度,例如可以是电极101,102的2/3嵌入到压电层103内。

[0024]

本发明并不对压电层103的形状和电极101,102的形状进行限定。压电层103截面形状可为圆形,或者正方形(参见图4)、矩形(参见图5、图6)等规则多边形,当然也可以是不规则多边形。电极101,102截面要求的形状可为圆形(参见图4),或者正方形(参见图5)、矩形(参见图6)等规则多边形,当然也可以是不规则多边形。

[0025]

电极101,102整体排列方式为规则图形(如圆环状、正方形、矩形、菱形)或不规则图形。

[0026]

此外,衬底104上带有刻蚀的空腔,所述空腔通过牺牲层填充刻蚀或为背向刻蚀。本发明并不对材料进行限定,衬底104可为为硅、蓝宝石衬底或者soi衬底,压电层103可为铌酸锂、钽酸锂或氮化铝等压电材料,电极101,102材料可为铂、钼、铜、铝或金等金属。

[0027]

此外,相邻电极电极101,102的间距可大于二倍声波波长。

[0028]

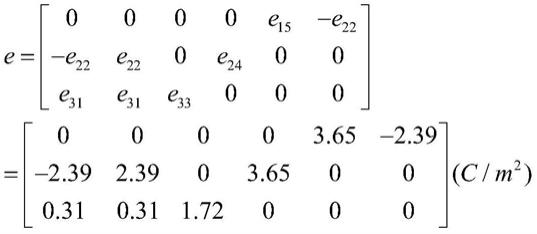

压电层103中的电极101,102被交替施加上正负电压后,压电层压电层103内部会产生多方向的电场耦合,电极101,102嵌入到压电层103的排布方式产生的电场使得压电层103内部的e

15

与e

24

产生耦合,由经典压电方程:

[0029]

t=cs-ee

[0030]

d=εe+es

[0031]

其中:

[0032][0033]

t是压电层中的应力;c是压电材料的弹性系数;s是压电材料的应变;e是压电材料的压电应力常数;e是电场强度;d是电位移。电场的增加能使e

15

与e

24

的耦合变强,从而提升谐振器的机电耦合系数;本发明电极101,102嵌入到压电层103的布置使得在压电层103中的电场得到增强并分布更加均匀,使得压电层103厚度方向与横向方向产生更强的耦合效应,从而使得谐振器的品质因数与机电耦合系数增加。

[0034]

图7展示了截面形状为长方形的电极全部嵌入截面形状为正方形的压电层的谐振器的阻抗曲线;图8展示了现有技术谐振器的阻抗曲线,以及截面形状为圆形的电极2/3嵌入截面形状为正方形的压电层的谐振器的阻抗曲线。串联谐振频率f

s

和并联谐振频率f

p

之间的频率间隔δf决定了谐振器的机电耦合系数k

2eff

的大小,可用下列公式计算:

[0035][0036]

现有技术谐振器模拟出来是31.277%,q值是71。本发明中电极101,102未完全嵌入到压电层103内的谐振器的机电耦合系数k

2eff

是34.655%,q值是241,k

2eff

增加了3.378%,q值增加了170。电极101,102完全嵌入到压电层103内的谐振器的机电耦合系数k

2eff

是38.986%,q值是600,k

2eff

增加了4.331%,q值增加了529。

[0037]

本发明的超高频谐振器将电极101,102的部分或全部沉积在压电层103中,使得在压电层103中的电场得到增强并分布更加均匀,使得压电层103厚度方向与横向方向的电场产生更强的耦合效应,从而使得谐振器的品质因数与机电耦合系数增加。相对于现有技术的谐振器,本发明的谐振器可以达到很高的谐振频率,且在很高的谐振频率下实现高机电耦合系数,提高品质因数,超高频且高机电耦合系数对后续搭建滤波器的性能起了决定的性能,意味着可以突破5ghz,实现更高频更高性能的芯片。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1