输出驱动电路的制作方法

输出驱动电路

1.相关申请的交叉引用

2.本技术要求于2020年5月19日向韩国知识产权局提交的、申请号为10

‑

2020

‑

0060001的韩国专利申请的优先权,其全部公开通过引用并入本文。

技术领域

3.本公开涉及一种电子装置,并且更特别地,涉及一种输出驱动电路以及包括该输出驱动电路的半导体装置。

背景技术:

4.在近来的芯片中通常使用需要较低电源电压和高速操作的高速接口ip。因此,作为配置芯片中的操作电路的元件,例如,具有中等栅极氧化物(例如,用于1.8v操作的栅极氧化物)的cmosfet或具有薄膜栅极氧化物(例如,用于0.9v操作的栅极氧化物)的cmosfet,与具有厚栅极氧化物(例如,用于3.3v操作的栅极氧化物)的 cmosfet相比,被更广泛地使用。

5.然而,输入/输出(io)电路仍然需要支持要求相对较高的接口电压(例如,3.3v接口电压)的应用电路。因此,由具有用于1.8v操作的中等栅极氧化物或用于0.9v操作的薄膜栅极氧化物的cmosfet 制成的输入/输出电路在被施加3.3v的电压时,由于诸如装置破坏的问题而难以操作。

技术实现要素:

6.本公开的实施例提供了一种具有提高的可靠性的输出驱动电路。

7.根据本公开的实施例的输出驱动电路包括下拉驱动器和稳压器。下拉驱动器包括在焊盘和接地节点之间的串联连接的第一、第二和第三晶体管。稳压器基于焊盘的电压和电源电压生成稳定电压,并且将稳定电压输出到第二晶体管的控制端子。

8.在实施例中,当焊盘的电压具有第一值并且电源电压具有小于第一值的第二值时,稳压器可以对焊盘的电压进行分压并且基于分压后的焊盘的电压而生成稳定电压。

9.在实施例中,稳定电压的值可以足以使第二晶体管的末端端子处的电压与第二晶体管的控制端子处的电压之间的差值等于或小于给定值。

10.在实施例中,第二值可以对应于接地电压,并且稳定电压的值可以小于第一值且大于第二值。

11.在实施例中,第一值可以大于1.8v。

12.在实施例中,第一值可以大于1.8v并且小于3.3v。

13.在实施例中,稳压器可以包括分压器和稳定电压生成器。分压器可以连接在焊盘和地之间。分压器可以被配置为对焊盘的电压进行分压并且将分压后的电压输出到第一内部节点。稳定电压生成器可以连接在电源电压和第一内部节点之间。稳定电压生成器可以被配置为基于电源电压输出稳定电压。

14.在实施例中,分压器可以包括连接在焊盘和第一内部节点之间的至少一个第一二极管,以及连接在第一内部节点和地之间的至少一个第二二极管。

15.在实施例中,第一二极管的数量和第二二极管的数量可以相同。

16.在实施例中,分压器可以进一步包括连接在第一内部节点和地之间的电容器。

17.在实施例中,稳定电压生成器可以包括在电源电压和第一内部节点之间串联连接的第四晶体管和第五晶体管。第四晶体管和第五晶体管可以在第二内部节点处连接。稳定电压生成器可以输出第二内部节点的电压作为稳定电压。

18.在实施例中,第四晶体管可以与电源电压相邻,并且第五晶体管可以与第一内部节点相邻。同时,第五晶体管可以是pmos晶体管,并且第五晶体管的栅极端子可以连接到电源电压。

19.在实施例中,第四晶体管可以是pmos晶体管,并且第四晶体管的栅极端子可以连接到第一内部节点。

20.在实施例中,稳定电压生成器可以进一步包括在电源电压和第二内部节点之间连接的第六晶体管。

21.在实施例中,第六晶体管可以是nmos晶体管,并且第六晶体管的栅极端子可以连接到电源电压。

22.在实施例中,第四晶体管可以是nmos晶体管,并且第四晶体管的栅极端子可以连接到电源电压。

23.在实施例中,当电源电压可以具有大于第二值且小于第一值的第三值时,稳压器可以输出电源电压作为稳定电压。

24.在实施例中,电源电压的第三值可以是大约1.8v。

25.在实施例中,输出驱动电路可以进一步包括输入/输出控制逻辑和栅极控制逻辑。输入/输出控制逻辑可以接收时钟信号和使能信号,并且将第一控制信号输出到第三晶体管。栅极控制逻辑可以接收焊盘的电压并且向第一晶体管的栅极端子输出反馈电压。

26.在实施例中,输出驱动电路可以进一步包括反相器和内部电阻器。反相器可以反转使能信号并将反转后的使能信号输出到栅极控制逻辑。内部电阻器可以具有连接到焊盘的第一末端和连接到栅极控制逻辑的第二末端。

27.在实施例中,下拉驱动器中包括的第一、第二和第三晶体管可以是nmos晶体管。

28.在实施例中,栅极控制逻辑可以包括在内部电阻器的第二末端的焊盘电压和电源电压之间串联连接的第一、第二和第三pmos晶体管。可以将电源电压施加到第一pmos晶体管的栅极端子,可以将焊盘电压施加到第二pmos晶体管的栅极端子。可以将反转后的使能信号施加到第三pmos晶体管的栅极端子,并且可以将第一、第二和第三pmos晶体管的体区域电压作为反馈电压输出。

29.在实施例中,第一pmos晶体管的漏极端子可以电连接到第一 pmos晶体管的体区域。

30.在实施例中,栅极控制逻辑可以进一步包括在电源电压和第一 pmos晶体管的体区域之间连接的第四pmos晶体管。可以将焊盘电压施加到第四pmos晶体管的栅极端子。

31.在实施例中,第四pmos晶体管的源极端子可以电连接到第四 pmos晶体管的体区域。

32.在实施例中,栅极控制逻辑可以进一步包括在体区域和电源电压之间串联连接的第四nmos晶体管和第五pmos晶体管。可以将电源电压施加到第四nmos晶体管的栅极端子。可以将第二控制信号施加到第五pmos晶体管的栅极端子。

33.根据本公开的实施例,可以提供一种具有提高的可靠性的输出驱动电路。

附图说明

34.图1是用于描述根据实施例的中等栅极氧化物装置的操作条件的示图。

35.图2是示出常规的输出驱动电路的示例的电路图。

36.图3是示出常规的输出驱动电路的另一示例的电路图。

37.图4a是图2的输出驱动电路的操作波形图。

38.图4b是示出图4a的放大的t1时段的波形图。

39.图5a是图3的输出驱动电路的操作波形图。

40.图5b是示出图5a的放大的t2时段的波形图。

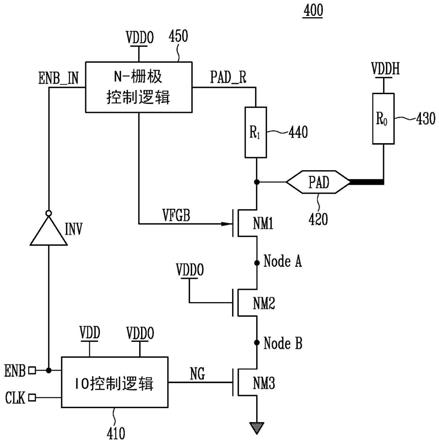

41.图6是示出根据本公开的实施例的输出驱动电路的电路图。

42.图7是示出根据实施例的适于用作图6的栅极控制逻辑的栅极控制逻辑的电路图。

43.图8是示出根据实施例的图7的第一pmos晶体管的具体配置的示图。

44.图9是示出根据实施例的图7的第二pmos晶体管的具体配置的示图。

45.图10是示出根据实施例的图7的第三pmos晶体管的具体配置的示图。

46.图11是示出根据另一实施例的适于用作图6的栅极控制逻辑的栅极控制逻辑的电路图。

47.图12a是根据实施例的图6的输出驱动电路的操作波形图。

48.图12b是示出图12a的放大的t3时段的波形图。

49.图13是用于描述添加图11的第四pmos晶体管的效果的波形图。

50.图14是示出根据本公开的另一实施例的输出驱动电路的电路图。

51.图15是示出根据实施例的适于用作图14的栅极控制逻辑的栅极控制逻辑的电路图。

52.图16是示出根据另一实施例的适于用作图14的栅极控制逻辑的栅极控制逻辑的电路图。

53.图17是示出当外部高电压vddh为1.8v时图14的输出驱动电路的操作的波形图。

54.图18是示出根据本公开的又一实施例的输出驱动电路的电路图。

55.图19a是示出根据实施例的适于用作图18的稳压器的稳压器的电路图。

56.图19b、图19c、图19d、图19e、图19f、图19g、图19h和图19i 是各自示出根据实施例的适于用作图18的稳压器的稳压器的电路图。

57.图20是示出根据本公开的另一实施例的输出驱动电路的电路图。

58.图21和图22是当内部电源电压vddo为0v时图18的输出驱动电路的操作波形图。

59.图23和图24是当内部电源电压vddo为第十电平v10时图18的输出驱动电路的操作波形图。

具体实施方式

60.示出根据在本说明书或申请中所公开的概念的实施例的具体结构或功能描述仅为了描述根据本公开的概念的实施例。根据本公开的概念的实施例可以以各种形式来实施,并且该描述不限于本说明书或申请中所描述的实施例。

61.图1是用于描述根据实施例的开关装置(例如,中等栅极氧化物装置)100的操作条件的示图。

62.为了使中等栅极氧化物装置100稳定运行,需要中等栅极氧化物装置100的栅极

‑

源极电压v

gs

、栅极

‑

漏极电压v

gd

和漏极

‑

源极电压 v

ds

满足可靠性条件。例如,当中等栅极氧化物装置100是用于1.8v操作的装置时,在栅极

‑

源极电压v

gs

、栅极

‑

漏极电压v

gd

和漏极

‑

源极电压v

ds

等于或小于1.8v的110%时确保了装置的可靠性。因此,可以推导出[表1]中所示的可靠性条件。

[0063]

[表1]

[0064]

电压差可靠性条件v

gd

v

gd

≤1.98vv

gs

v

gs

≤1.98vv

ds

v

ds

≤1.98v

[0065]

为了满足这种条件,常规的输出驱动电路由图2或图3所示的电路配置,稍后将对其进行描述。

[0066]

图2是示出常规的输出驱动电路200的示例的电路图。

[0067]

参照图2,输出驱动电路200由输入/输出控制逻辑(io控制逻辑) 210以及串联连接的第一晶体管nma和第二晶体管nmb配置。第一晶体管nma连接在焊盘(pad)220和节点node0之间,并且第二晶体管 nmb连接在节点node0和地之间。第一电源电压vddo被施加到第一晶体管nma的栅极端子,并且从输入/输出控制逻辑210输出的栅极控制信号ng被施加到第二晶体管nmb的栅极端子。同时,输入/输出控制逻辑210基于第一电源电压vddo和第二电源电压vdd进行操作,接收使能信号enb和时钟信号clk,并且输出栅极控制信号ng。同时,焊盘220通过外部电阻器r

0 230连接到外部高电压vddh。

[0068]

在图4a和4b中示出图2的输出驱动电路200的操作波形图。稍后将参照图4a和4b描述图2所示的输出驱动电路200的操作。

[0069]

图3是示出常规的输出驱动电路300的另一示例的电路图。

[0070]

参照图3,输出驱动电路300由输入/输出控制逻辑310以及串联连接的第一晶体管nm1、第二晶体管nm2和第三晶体管nm3配置。第一晶体管nm1连接在焊盘320和节点a node a之间,第二晶体管nm2 连接在节点a node a和节点b node b之间,并且第三晶体管nm3连接在节点b node b和地之间。第一电源电压vddo被施加到第一晶体管 nm1和第二晶体管nm2的栅极端子,并且从输入/输出控制逻辑310 输出的栅极控制信号ng被施加到第三晶体管nm3的栅极端子。同时,输入/输出控制逻辑310基于第一电源电压vddo和第二电源电压 vdd进行操作,接收使能信号enb和时钟信号clk,并且输出栅极控制信号ng。同时,焊盘320通过外部电阻器r0连接到外部高电压 vddh。

[0071]

在图5a和图5b中示出了图3的输出驱动电路300的操作波形图。稍后将参照图5a和图5b描述图3所示的输出驱动电路300的操作。

[0072]

图2和图3所示的常规的输出驱动电路200和300使用厚栅极氧化物元件(2.5v或3.3v元件)。因此,在接口连接3.3v或5v信号时,氧化物厚度较厚。因此,即使栅极

‑

漏极电压v

gd

和漏极

‑

源极电压v

ds

处于稍微超出可靠性的区间,也可以确保元件的可靠性。然而,当在当前的32纳米或更小的制程中使用中等栅极氧化物元件(1.8v元件)来驱动3.3v的接口连接时,元件的氧化物厚度变薄,满足可靠性条件变得困难。

[0073]

图4a是图2的输出驱动电路200的操作波形图。另外,图4b是示出图4a的放大的t1时段的波形图。

[0074]

参照图4a,示出了焊盘220的电压和节点node0的电压。焊盘220 的电压可以增加到第一电平v1,节点node0的电压可以增加到第二电平v2。第一电平v1可以是大约3.5v,第二电平v2可以是大约1.6v。因此,焊盘220的电压和节点node0的电压之间的差被保持为大约2v 或更小。因此,满足第一晶体管nma的漏极

‑

源极电压v

ds

的条件。然而,随着焊盘220的电压迅速降低,节点node0的电压也降低,在这种情况下,如下面将参照图4b所描述的,发生不满足漏极

‑

源极电压v

ds

的可靠性条件的情况。

[0075]

参照图4b,放大了图4a中的虚线所示的t1时段的波形图。如图 4b所示,在t1时段期间焊盘210的电压和节点node0的电压降低的d1 时段中,焊盘210的电压与节点node0的电压之间的差暂时可以是大于第一电平v1与第二电平v2之间的差(例如,约2v)的值δva。例如,在时间ta的值δva可以是2.9v。在这种情况下,焊盘210的电压与节点node0的电压之间的差暂时为2.9v,这是不满足1.8v元件的漏极

‑ꢀ

源极电压v

ds

的可靠性条件的情况。

[0076]

图5a是图3的输出驱动电路300的操作波形图。同时,图5b是示出图5a的放大的t2时段的波形图。

[0077]

参照图5a,示出了焊盘320的电压、节点a node a的电压和节点 b node b的电压。焊盘320的电压可以增加到第一电平v1,并且节点 a node a的电压和节点b node b的电压可以增加到第二电平v2。第一电平v1可以是大约3.5v,第二电平v2可以是大约1.6v。因此,总体而言,焊盘320的电压与节点a node a的电压之间的差或焊盘320 的电压与节点b node b的电压之间的差被保持为约2v或更小。因此,满足第一晶体管nm1和第二晶体管nm2的漏极

‑

源极电压v

ds

的条件。然而,随着焊盘320的电压迅速降低,如下面将参照图5b所描述的,发生不满足第一晶体管nm1和第二晶体管nm2的漏极

‑

源极电压v

ds

的可靠性条件的情况。

[0078]

参照图5b,放大了图5a中的虚线所示的t2时段的波形图。如图 5b所示,在t2时段期间,在焊盘320的电压和节点a node a的电压降低的d2时段中,焊盘320的电压与节点a node a的电压之间的差暂时可以是大于第一电平v1与第二电平v2之间的差(例如,约2v)的值。例如,焊盘320的电压与节点a node a的电压之间的差暂时为2.8v,这是不满足1.8v元件的漏极

‑

源极电压v

ds

的可靠性条件的情况。

[0079]

因此,可能需要具有提高的可靠性的新的输出驱动电路的结构。

[0080]

图6是示出根据本公开的实施例的输出驱动电路400的电路图。

[0081]

参照图6,根据本公开实施例的输出驱动电路400包括在焊盘420 和接地节点之间顺序地串联连接的第一、第二和第三晶体管nm1、 nm2和nm3、输入/输出控制逻辑410、栅极控制逻辑450以及反相器 inv。第一、第二和第三晶体管nm1、nm2和nm3可以配置下拉驱动器。输入/输出控制逻辑410接收时钟信号clk和使能信号enb,并且将第一控制信号ng传送到第三晶体管nm3。栅极控制逻辑450接收焊盘420的电压pad_r。另外,栅极控制逻辑450将

反馈电压vfgb输出到第一晶体管nm1的栅极端子。反相器inv反转使能信号enb并且将反转后的使能信号enb_in输出到栅极控制逻辑450。同时,焊盘420 通过外部电阻器r0连接到外部高电压vddh。另外,输出驱动电路400 可以进一步包括内部电阻器r1,内部电阻器r1连接在焊盘420和栅极控制逻辑450之间。在实施例中,内部电阻器r1可以用作esd保护电阻器。

[0082]

输出驱动电路400的第一、第二和第三晶体管nm1、nm2和nm3 可以是1.8v操作元件的中等栅极氧化物元件。为了提高可靠性,如图所示配置了三级串联连接结构。同时,输出驱动电路400的第一、第二和第三晶体管nm1、nm2和nm3具有开放漏极(open

‑

drain)输出结构。第一晶体管nm1的栅极端子接收反馈电压vfgb,并且反馈电压vfgb的电压电平根据开放漏极输出的电平而改变。同时,第一电源电压vddo可以是1.8v,并且外部高电压vddh可以是3.3v。当输出被激活时,使能信号enb变为高状态,并且当时钟信号clk为高状态时,焊盘420通过由外部电阻器r

0 430连接的外部高电压vddh而变为高状态。当时钟信号clk为低状态时,开放漏极输出结构的nmos 驱动器接通,因而焊盘420操作为低状态。在此,稍后将参照图7和图 8描述栅极控制逻辑450的详细配置。

[0083]

图7是示出根据实施例的适于用作图6的栅极控制逻辑450的栅极控制逻辑450a的电路图。

[0084]

参照图7,栅极控制逻辑450a包括在焊盘电压pad_r和第一电源电压vddo之间顺序地串联连接的第一、第二和第三pmos晶体管 pm1、pm2和pm3。第一、第二和第三pmos晶体管pm1、pm2和pm3 的串联连接结构可以配置反馈晶体管组件451a。第一pmos晶体管 pm1的漏电极和第二pmos晶体管pm2的源电极连接到节点nd2。另外,第二pmos晶体管pm2的漏电极和第三pmos晶体管pm3的源电极连接到节点nd1。同时,第一电源电压vddo被施加到第一pmos 晶体管pm1的栅极端子,焊盘电压pad_r被施加到第二pmos晶体管 pm2的栅极端子,并且反转后的使能信号enb_in被施加到第三 pmos晶体管pm3的栅极端子。另外,第一、第二和第三pmos晶体管pm1、pm2和pm3的体区域连接到反馈电压vfgb。

[0085]

当时钟信号clk为低状态时,焊盘电压pad_r变为低状态。因此,第二pmos晶体管pm2导通,从而第一电源电压vddo(即1.8v)作为反馈信号vfgb输出。因此,图6的第一晶体管nm1保持导通状态。此时,第一pmos晶体管pm1的栅极电压是第一电源电压vddo。由于焊盘420为低状态,所以第一pmos晶体管pm1关断。因此,从连接到第三pmos晶体管pm3的第一电源电压vddo到焊盘电压pad_r的电流路径被切断。

[0086]

此后,当在时钟信号clk改变为高状态的时间点焊盘420的电压从0v改变为外部高电压vddh(即,3.3v)时,在焊盘电压pad_r 大于第一电源电压vddo与第一pmos晶体管的阈值电压vth_pm1之和的时间点,第一pmos晶体管pm1导通,因此反馈电压vfgb遵循焊盘420的电压电平。此时,反馈电压vfgb处于反馈电压vfgb从第一电源电压vddo增加到外部高电压vddh的状态。另外,随着作为第二pmos晶体管pm2的栅极电压的焊盘电压pad_r变得等于反馈电压vfgb,第二pmos晶体管pm2关断。因此,从反馈电压vfgb的输出端子到连接到第三pmos晶体管pm3的第一电源电压vddo的电流路径被切断。因此,降低了功耗,并且基本上防止了反馈电压vfgb 的降低。另外,在第二pmos晶体管pm2的情况下,即使当节点nd1 的电压为1.8v时反馈电压vfgb增加到3.3v,栅极

‑

源极电压v

gs

、栅极

‑

漏极电压v

gd

和漏极

‑

源极电压v

ds

之间的电压差也保持在1.98v以内,因此第二pmos晶体管pm2的可靠性条件也得到满足。

[0087]

也就是说,在开放漏极输出结构的特性之中,即使当时钟信号 clk从低状态转换到高状态时,即,当焊盘420的电压从外部高电压 vddh转换到0v时,根据本公开的实施例的输出驱动电路400也将焊盘420与节点a node a之间的电压差保持在1.98v或更小,因此提高了装置的可靠性。在图12a和图12b中示出根据图6和图7的实施例的输出驱动电路400的操作波形图,并且稍后将参照图12a和图12b描述操作特性。

[0088]

图8是示出根据实施例的图7的第一pmos晶体管pm1的具体配置的示图。

[0089]

在图7中,第一pmos晶体管pm1的体区域电压连接到反馈电压 vfgb。在图8中,具体示出了第一pmos晶体管pm1的这种结构。

[0090]

参照图8,在p型衬底460上形成n阱461。n阱461可以用作第一 pmos晶体管pm1的体区域。同时,在n阱461上形成源极区域465和漏极区域463。源极区域465和漏极区域463可以形成为高浓度p+区域。分别在源极区域465和漏极区域463上形成源电极473和漏电极471。另外,在n阱461上形成绝缘层481和栅电极483。因此,配置了第一pmos 晶体管pm1。另外,在n阱461上进一步形成高浓度n+区域467,以提供与作为体区域的n阱461的电连接。在n+区域467上形成体电极475。

[0091]

同时,参考第一pmos晶体管pm1的电极连接,源电极473连接到焊盘电压pad_r,漏电极471连接到反馈电压vfgb,并且栅电极 483连接到第一电源电压vddo。另外,体电极475可以连接到反馈电压vfgb,以配置图7所示的第一pmos晶体管pm1的电连接关系。

[0092]

图9是示出根据实施例的图7的第二pmos晶体管pm2的具体配置的示图。

[0093]

在图7中,第二pmos晶体管pm2的体区域电压连接到反馈电压 vfgb。在图9中,具体示出了第二pmos晶体管pm2的结构。

[0094]

参照图9,在p型衬底460上形成n阱462。n阱462可以用作第二 pmos晶体管pm2的体区域。同时,在n阱462上形成源极区域466和漏极区域464。源极区域466和漏极区域464可以形成为高浓度p+区域。分别在源极区域466和漏极区域464上形成源电极474和漏电极472。另外,在n阱462上形成绝缘层482和栅电极484。因此,配置了第二pmos 晶体管pm2。另外,在n阱462上进一步形成高浓度n+区域468,以提供与作为体区域的n阱462的电连接。在n+区域468上形成体电极476。

[0095]

同时,参考第二pmos晶体管pm2的电极连接,源电极474连接到反馈电压vfgb,漏电极472连接到节点nd1,并且栅电极484连接到焊盘电压pad_r。另外,体电极476可以连接到反馈电压vfgb,以配置图7所示的第二pmos晶体管pm2的电连接关系。

[0096]

图10是示出根据实施例的图7的第三pmos晶体管pm3的具体配置的示图。

[0097]

在图7中,第三pmos晶体管pm3的体区域电压连接到反馈电压 vfgb。在图10中,具体示出了第三pmos晶体管pm3的结构。

[0098]

参照图10,在p型衬底460上形成n阱469。n阱469可以用作第三 pmos晶体管pm3的体区域。同时,在n阱469上形成源极区域477和漏极区域470。源极区域477和漏极区域470可以形成为高浓度p+区域。分别在源极区域477和漏极区域470上形成源电极485和漏电极480。另外,在n阱469上形成绝缘层487和栅电极489。因此,配置了第三pmos 晶体管pm3。另外,在n阱469上进一步形成高浓度n+区域478,以提供与作为体区域的n阱469的电连接。在n+区域478上形成体电极486。

[0099]

同时,参考第三pmos晶体管pm3的电极连接,源电极485连接到节点nd1,漏电极480

连接到第一电源电压vddo,并且栅电极489 连接到反转后的使能信号enb_in。另外,体电极486连接到反馈电压 vfgb,以形成图7所示的第三pmos晶体管pm3的电连接关系。

[0100]

图11是示出根据另一实施例的适于用作图6的栅极控制逻辑450 的栅极控制逻辑450b的电路图。

[0101]

根据图11的栅极控制逻辑450b的结构类似于图7的栅极控制逻辑 450a的结构,并且不同之处在于,栅极控制逻辑450b进一步包括第四 pmos晶体管pm4。第四pmos晶体管pm4可以配置稳压器452b。也就是说,栅极控制逻辑450b包括反馈晶体管组件451b和稳压器452b。稍后将参照图13描述通过进一步包括第四pmos晶体管pm4而获得的效果。

[0102]

图12a是根据实施例的图6的输出驱动电路400的操作波形图。同时,图12b是示出图12a的放大的t3时段的波形图。

[0103]

参照图12a,当时钟信号clk从低状态转换为高状态时,焊盘420 的电压从外部高电压vddh改变为0v。外部高电压vddh的电压电平可以是第一电平v1。第一电平v1可以是3.5v。节点a node a的电压可以从略小于焊盘420的电压的电平改变为0v。同时,节点b node b 的电压可以从第二电平v2改变为0v。第二电平v2可以是大约1.6v。

[0104]

随着焊盘420的电压改变为0v,反馈电压vfgb的电压电平可以从第一电平v1改变为第三电平v3。第三电平v3可以是大约1.8v。因此,反馈电压vfgb的电压电平从3.5v改变为1.8v。

[0105]

参照图12b,放大了图12a中的虚线所示的t3时段的波形图。如图12b所示,在t3时段期间,在焊盘420的电压、节点a node a的电压和节点b node b的电压降低的d3时段中,焊盘420的电压与节点anode a的电压之间的差可以保持为小于第一电平v1和第二电平v2之间的差(例如,大约2v)的值。此外,在d3时段中,节点a node a 的电压与节点b node b的电压之间的差可以保持为小于第一电平v1 和第二电平v2之间的差(例如,约2v)的值。

[0106]

也就是说,在将焊盘420的偏压施加到第一晶体管nm1的栅极之后,栅极偏压切换到1.8v。因此,在节点a node a的电压增加了 vddh

‑

vth_nm1的状态下逐渐降低电压电平,以使焊盘420的电压与节点a node a的电压之间的差以及节点a node a的电压与节点bnode b的电压之间的差最小化。因此,满足了第一和第二晶体管nm1 和nm2的可靠性条件。

[0107]

图13是用于描述添加图11所示的第四pmos晶体管pm4即稳压器 452b的效果的波形图。在图13中,顺序地示出了焊盘电压、当不存在第四pmos晶体管pm4时的反馈电压vfgb以及当添加了第四pmos 晶体管pm4时的反馈电压vfgb。

[0108]

当不存在第四pmos晶体管pm4时,反馈电压vfgb在区域a和区域b中不稳定。然而,当添加了第四pmos晶体管pm4时,反馈电压 vfgb在区域c和区域d中可以是稳定的。

[0109]

图14是示出根据本公开的另一实施例的输出驱动电路400的电路图。

[0110]

参照图14,根据本公开实施例的输出驱动电路500包括在焊盘520 和接地节点之间顺序地串联连接的第一、第二和第三晶体管nm1、 nm2和nm3、输入/输出控制逻辑510、栅极控制逻辑550和反相器 inv。输入/输出控制逻辑510接收时钟信号clk和使能信号enb,并且将第一控制信号ng传送到第三晶体管nm3。栅极控制逻辑550接收焊盘520的电压pad_r。另外,栅极控制逻辑550将反馈电压vfgb输出到第一晶体管nm1的栅极端子。反相器inv反转使能信号enb并且将反转后的使能信号enb_in传送到栅极控制逻辑550。另外,栅极控制逻辑550接收第二控制信号vsel。同时,焊盘520通过外部电阻器 r0连接到外部高电压vddh。

另外,输出驱动电路500可以进一步包括内部电阻器r1,内部电阻器r1连接在焊盘520和栅极控制逻辑550 之间。如上所述,内部电阻器r1可以用作esd保护电阻器。图14的输出驱动电路500与图6的输出驱动电路400之间的差异在于栅极控制逻辑550进一步接收第二控制信号vsel。稍后将参照图15描述栅极控制逻辑550的具体配置和操作。

[0111]

图15是示出根据实施例的适于用作图14的栅极控制逻辑550的栅极控制逻辑550a的电路图。

[0112]

参照图15,栅极控制逻辑550a包括在焊盘电压pad_r和第一电源电压vddo之间顺序地串联连接的第一、第二和第三pmos晶体管 pm1、pm2和pm3。第一、第二和第三pmos晶体管pm1、pm2和pm3 的串联连接结构可以配置反馈晶体管组件551a。第一pmos晶体管 pm1的漏电极和第二pmos晶体管pm2的源电极连接到节点nd2。另外,第二pmos晶体管pm2的漏电极和第三pmos晶体管pm3的源电极连接到节点nd1。同时,第一电源电压vddo被施加到第一pmos 晶体管pm1的栅极端子,焊盘电压pad_r被施加到第二pmos晶体管 pm2的栅极端子,并且反转后的使能信号enb_in被施加到第三 pmos晶体管pm3的栅极端子。另外,第一、第二和第三pmos晶体管pm1、pm2和pm3的体区域电压作为反馈电压vfgb输出。

[0113]

同时,图15的栅极控制逻辑550a和图7的栅极控制逻辑450a之间的差异在于栅极控制逻辑550a进一步包括在反馈电压vfgb的输出端子和第一电源电压vddo之间顺序地串联连接的第四nmos晶体管 nm4和第五pmos晶体管pm5。第四nmos晶体管nm4和第五pmos 晶体管pm5可以配置外部电压选择器553a。第一电源电压vddo被施加到第四nmos晶体管nm4的栅极端子,并且第二控制信号vsel被施加到第五pmos晶体管pm5的栅极端子。通过附加的第五pmos晶体管pm5,即使在外部高电压vddh为1.8v的情况下,所公开的开放漏极输出结构也可以进行操作。同时,当外部高电压vddh为3.3v时,第四nmos晶体管nm4使第五pmos晶体管pm5的漏极电压为 vddo

‑

vth_nm4(在这种情况下,第五pmos晶体管pm5的漏极电压变为大约1.4v),以满足第五pmos晶体管pm5的可靠性条件。

[0114]

当外部高电压vddh为3.3v时,图15所示的栅极控制逻辑550a与图7所示的栅极控制逻辑450a相同地操作。当外部电压vddh为1.8v 时,反馈电压vfgb保持在vddo

‑

vth_nm4和1.8v之间(即,1.4v≤ vfgb≤1.8v)。也就是说,可以使用比外部电压选择器553a更灵活的开放漏极输出结构。

[0115]

图16是示出根据另一实施例的适于用作图14的栅极控制逻辑550 的栅极控制逻辑550b的电路图。

[0116]

图16所示的栅极控制逻辑550b的配置与图15所示的栅极控制逻辑550a的配置相似,并且包括反馈晶体管组件551b和外部电压选择器 553b。不同之处在于,图16的栅极控制逻辑550b进一步包括如图11 所示的第四pmos晶体管pm4,即,稳压器552b。如以上参照图13所述,可以通过添加第四pmos晶体管pm4来形成更稳定的反馈电压 vfgb。

[0117]

图17是示出当外部高电压vddh为1.8v时图14的输出驱动电路500的操作的波形图。参照图17,焊盘pad的电压可以增加到第四电平v4。在实施例中,第四电平v4可以是1.8v。如图17所示,当输出驱动电路500如图14和图15所示配置时,即使外部高电压vddh为第四电平v4即1.8v,也可以适当地满足元件的可靠性条件。

[0118]

然而,在第一电源电压vddo的值为0v的情况下,当通过焊盘施加外部高电压vddh时,可能发生元件的可靠性问题。例如,当第一电源电压vddo为0v并且将超过1.98v的外部

高电压vddh施加到焊盘时,节点a node a的电压也为1.98v。此时,第二晶体管nm2的栅极

‑

漏极电压v

gd

可能超过1.98v。因此,可以满足第一晶体管nm1的可靠性条件,但是可能不满足第二晶体管nm2的可靠性条件。因此,可能需要即使当第一电源电压vddo处于关断状态即0v时也能够满足元件的可靠性条件的输出驱动电路。

[0119]

图18是示出根据本公开的又一实施例的输出驱动电路600的电路图。

[0120]

参照图18,根据本公开的又一实施例的输出驱动电路600包括在焊盘620和接地节点之间顺序地串联连接的第一、第二和第三晶体管 nm1、nm2和nm3、输入/输出控制逻辑610、栅极控制逻辑650、反相器inv和稳压器670。输入/输出控制逻辑610接收时钟信号clk和使能信号enb,并且将第一控制信号ng输出到第三晶体管nm3。栅极控制逻辑650接收焊盘620的电压pad_r。另外,栅极控制逻辑650将反馈电压vfgb输出到第一晶体管nm1的栅极端子。反相器inv反转使能信号enb并且将反转后的使能信号enb_in输出到栅极控制逻辑 650。同时,焊盘620通过外部电阻器r0连接到外部高电压vddh。另外,输出驱动电路600可以进一步包括内部电阻器r1,内部电阻器r1连接在焊盘620和栅极控制逻辑650之间。在实施例中,内部电阻器r1可以用作esd保护电阻器。

[0121]

图18的输出驱动电路600可以与图6的输出驱动电路400基本上相同,除了输出驱动电路600进一步包括稳压器670并且第二晶体管nm2 从稳压器670接收稳定电压vstb。因此,图18的栅极控制逻辑650可以被实施为图7的栅极控制逻辑450a和图11的栅极控制逻辑450b中的一个。稳压器670连接到焊盘620以接收施加到焊盘620的电压,并且将稳定电压vstb输出到第二晶体管nm2的栅极端子。

[0122]

稳定电压vstb可以是在满足第二晶体管nm2的可靠性条件的范围内的电压。具体地,稳定电压vstb可以具有足以使第二晶体管 nm2的两个端子之间的电压差等于或小于给定值的值,从而确保第二晶体管nm2的可靠性。在实施例中,稳定电压vstb可以是使第二晶体管nm2的栅极

‑

漏极电压v

gd

具有1.98v或更小的值的电压,如表1 所示。例如,当通过焊盘620施加并通过第一晶体管nm1施加到第二晶体管nm2的漏极的电压是3.3v时,稳定电压vstb可以是大于1.32v 且小于3.3v的电压。

[0123]

也就是说,即使第一电源电压vddo是0v,根据本公开的实施例的稳压器670也可以将具有1.32v或更大的值的稳定电压vstb施加到第二晶体管nm2的栅极端子。因此,即使当施加外部高电压vddh的相对较高的电平(例如,3.3v)并且第一电源电压vddo具有相对较低的电平(例如,0v)时,也可以满足第二晶体管nm2的可靠性条件。

[0124]

图19a是示出根据实施例的适于用作图18的稳压器670的稳压器 670a的电路图。参照图19a,根据本公开的实施例的稳压器670a包括分压器671a和稳定电压生成器673a。

[0125]

分压器671a连接到焊盘(例如,图18中的焊盘620),并且通过第一内部节点ni1输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压v_div。在图19a的实施例中,分压器671a包括在焊盘和接地节点之间串联连接的第一二极管d1和第二二极管d2。然而,本公开的实施例不限于此,并且可以被实施为能够对通过焊盘施加的电压v_pad进行分压并输出分压电压的任何类型的分压电路。例如,分压器可以包括在焊盘和接地节点之间串联连接的多个电阻器。

[0126]

在实施例中,第一二极管d1和第二二极管d2的特性可以基本上相同。例如,第一二极管d1和第二二极管d2中的每一个的正向电压可以基本上等于从焊盘施加的电压v_pad的

一半。在这种情况下,分压电压v_div可以具有对应于从焊盘施加的电压v_pad的大约一半的值。然而,本公开的实施例不限于此,并且分压器671a可以被配置为使得分压电压v_div具有在从焊盘施加的电压v_pad和接地电压之间的任意值。

[0127]

稳定电压生成器673a通过第一内部节点ni1接收分压电压 v_div。另外,稳定电压生成器673a接收第一电源电压vddo。在图 19a的实施例中,稳定电压生成器673a可以包括在第一电源电压 vdd0和第一内部节点ni1之间串联连接的第六pmos晶体管pm6和第七pmos晶体管pm7。第六pmos晶体管pm6连接在第一电源电压 vddo和第二内部节点ni2之间。第六pmos晶体管pm6的栅极端子连接到第一内部节点ni1。第七pmos晶体管pm7连接在第二内部节点 ni2和第一内部节点ni1之间。第七pmos晶体管pm7的栅极端子连接到第一电源电压vddo。同时,稳定电压生成器673a通过第二内部节点ni2输出稳定电压vstb。

[0128]

当第一电源电压vddo为0v的电压时,第七pmos晶体管pm7导通。同时,当在第一电源电压vddo为0v的状态下,施加到焊盘的电压v_pad是相对较高的电压(例如3.3v)时,分压电压v_div约为 1.65v。在这种情况下,分压电压v_div可以是使第六pmos晶体管 pm6弱导通的电压。由于第六pmos晶体管pm6弱导通并且第七 pmos晶体管pm7相对强导通,因此稳定电压生成器673a输出基本上等于分压电压v_div的稳定电压vstb。

[0129]

在实施例中,稳定电压vstb的大小可以足以使第二晶体管nm2 的末端端子(例如,漏极)和第二晶体管nm2的控制端子(例如,栅极)处的电压之间的差等于或小于用于满足第二晶体管nm2的可靠性条件的给定值(例如,1.98v)。例如,如上所述,当施加到焊盘的电压v_pad为3.3v时,用于满足第二晶体管nm2的可靠性条件的稳定电压vstb为大于1.32v的电压(例如,大约1.65v)。因此,分压器671a 可以对3.3v的焊盘电压进行分压,并且输出大于1.32v的电压作为分压电压v_div。在这种情况下,即使在第一电源电压vddo为0v的状态下通过焊盘施加3.3v的外部高电压vddh,也可以满足第二晶体管 nm2的可靠性条件。

[0130]

当第一电源电压vddo是除0v以外的正常状态的电压(例如, 1.8v)时,第七pmos晶体管pm7关断。例如,当第一电源电压vddo 为大约1.8v时,第一电源电压vddo可以在1.7v至1.9v、1.75v至 1.85v、1.77v至1.83v或1.79v至1.81v的范围内。同时,当施加到焊盘的电压v_pad是高电压(例如3.3v)时,分压电压v_div变为大约 1.65v。在这种情况下,分压电压v_div可以是使第六pmos晶体管 pm6弱导通的电压。由于第六pmos晶体管pm6弱导通并且第七 pmos晶体管pm7关断,所以通过第二内部节点ni2输出的稳定电压 vstb可以基本上等于正常状态的第一电源电压vddo。然而,在这种情况下,由于第六pmos晶体管pm6弱导通,所以稳定电压vstb 可以有些缓慢地增加以达到第一电源电压vddo。

[0131]

图19b是示出根据另一实施例的适于用作图18的稳压器670的稳压器670b的电路图。参照图19b,根据本公开的另一实施例的稳压器 670b包括分压器671b和稳定电压生成器673b。图19b的分压器671b可以与图19a的分压器671a基本上相同。因此,省略了对分压器671b的重复描述。

[0132]

稳定电压生成器673b通过第一内部节点ni1接收分压电压 v_div。另外,稳定电压生成器673b接收第一电源电压vddo。在图19b的实施例中,稳定电压生成器673b可以包括在第一电源电压 vddo和第一内部节点ni1之间串联连接的第五nmos晶体管nm5和第八pmos晶体管pm8。第五nmos晶体管nm5连接在第一电源电压 vddo和第二内部节点ni2之间。第五nmos晶体管nm5的栅极端子连接到第一电源电压vddo。第八pmos晶体管pm8连接在第二内部

节点ni2和第一内部节点ni1之间。第八pmos晶体管pm8的栅极端子连接到第一电源电压vddo。同时,稳定电压生成器673b通过第二内部节点ni2输出稳定电压vstb。

[0133]

当第一电源电压vddo是0v的电压时,第五nmos晶体管nm5 关断,并且第八pmos晶体管pm8导通。因此,在这种情况下,稳定电压生成器673b将分压电压v_div作为稳定电压vstb输出到第二晶体管nm2的栅极端子。

[0134]

当第一电源电压vddo是除0v之外的正常状态的电压(例如, 1.8v)时,第五nmos晶体管nm5导通并且第八pmos晶体管pm8关断。因此,在这种情况下,稳定电压生成器673b将第一电源电压vddo 作为稳定电压vstb输出到图18的第二晶体管nm2的栅极端子。

[0135]

在图19a的稳定电压生成器673a的情况下,由于当第一电源电压 vddo是除了0v以外的正常状态的电压时第六pmos晶体管pm6被弱导通,因此稳定电压vstb可以有些缓慢地增加到第一电源电压 vddo的电压电平。与此相比,在图19b的稳定电压生成器673b的情况下,通过第一电源电压vddo导通的第五nmos晶体管nm5可以将稳定电压vstb迅速增加到第一电源电压vddo的电压电平。

[0136]

图19c是示出根据另一实施例的适于用作图18的稳压器670的稳压器670c的电路图。参照图19c,根据本公开的另一实施例的稳压器 670c包括分压器671c和稳定电压生成器673c。图19c的稳定电压生成器673c可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673c的重复描述。

[0137]

参照图19c,分压器671c连接到焊盘,并且通过第一内部节点ni1 输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压 v_div。与图19a的包括两个二极管d1和d2的分压器671a不同,在图 19c的实施例中,分压器671c包括在焊盘和接地节点之间串联连接的第三至第六二极管d3至d6。根据二极管的尺寸和施加电压,可以不同地确定分压器671c中包括的二极管的数量。例如,假设可以将相同电平(例如,3.3v)的电压施加到焊盘,图19c中的第三至第六二极管d3至d6中的每一个的尺寸可以使得其正向电压为图19a中的第一和第二二极管d1和d2中的每一个的大约一半,从而使图19c的第三和第四二极管d3和d4两端的电压降基本上等于图19a的第一二极管d1 两端的电压降,并且使图19c的第五和第六二极管d5和d6两端的电压降基本上等于图19a的第二二极管d2两端的电压降。同时,在图19c 中,在焊盘和第一内部节点ni1之间连接的二极管d3和d4的数量与在第一内部节点ni1和地之间连接的二极管d5和d6的数量相同。然而,本公开的实施例不限于此,并且可以在焊盘和第一内部节点ni1之间以及在第一内部节点ni1和地之间连接不同数量的二极管。

[0138]

同时,图19c所示的分压器671c可以进一步包括连接在第一内部节点ni1与地之间的电容器c1。也就是说,电容器c1并联连接到第五和第六二极管d5和d6。通过连接在第一内部节点ni1与地之间的电容器c1可以稳定地保持通过第一内部节点ni1输出的分压电压v_div。

[0139]

图19d是示出根据另一实施例的适于用作图18的稳压器670的稳压器670d的电路图。参照图19d,根据本公开的另一实施例的稳压器 670d包括分压器671d和稳定电压生成器673d。图19d的分压器671d可以与图19c的分压器671c基本上相同。因此,省略了对分压器671d的重复描述。

[0140]

稳定电压生成器673d通过第一内部节点ni1接收分压电压 v_div。另外,稳定电压生成器673d接收第一电源电压vddo。在图19d的实施例中,稳定电压生成器673d可以包括串

联连接在第一电源电压vddo和第一内部节点ni1之间的第六pmos晶体管pm6和第七 pmos晶体管pm7,以及连接在第一电源电压vddo和第二内部节点 ni2之间的第六nmos晶体管nm6。第六pmos晶体管pm6连接在第一电源电压vddo和第二内部节点ni2之间。第六pmos晶体管pm6的栅极端子连接到第一内部节点ni1。第七pmos晶体管pm7连接在第二内部节点ni2和第一内部节点ni1之间。第七pmos晶体管pm7的栅极端子连接到第一电源电压vddo。第六nmos晶体管nm6的栅极端子连接到第一电源电压vddo。同时,稳定电压生成器673d通过第二内部节点ni2输出稳定电压vstb。

[0141]

比较图19c和图19d,图19d的稳定电压生成器673d与图19c的稳定电压生成器673c基本上相同,除了稳定电压生成器673d进一步包括连接在第一电源电压vddo和第二内部节点ni2之间的第六nmos晶体管nm6。

[0142]

当第一电源电压vddo为0v的电压时,第七pmos晶体管pm7导通并且第六nmos晶体管nm6关断。同时,当在第一电源电压vddo 为0v的状态下施加到焊盘的电压v_pad是高电压(例如3.3v)时,分压电压v_div约为1.65v。在这种情况下,分压电压v_div可以是使第六pmos晶体管pm6弱导通的电压。由于第六晶体管pm6弱导通并且第七pmos晶体管pm7相对强导通,因此稳定电压生成器673d输出基本上等于分压电压v_div的稳定电压vstb。

[0143]

如上所述,当施加到焊盘的电压v_pad为3.3v时,用于满足图18 的第二晶体管nm2的可靠性条件的稳定电压vstb为大于1.32v的电压。因此,分压器671d可以对3.3v的焊盘电压进行分压,并且输出大于1.32v的电压作为分压电压v_div。在这种情况下,即使在第一电源电压vddo为0v的状态下通过焊盘施加3.3v的外部高电压vddh,也可以满足第二晶体管nm2的可靠性条件。

[0144]

当第一电源电压vddo是除0v以外的正常状态的电压(例如, 1.8v)时,第七pmos晶体管pm7关断并且第六nmos晶体管nm6导通。同时,当施加到焊盘的电压v_pad是相对较高的电压(例如3.3v) 时,分压电压v_div为大约1.65v。在这种情况下,分压电压v_div 可以是使第六pmos晶体管pm6弱导通的电压。由于在第七pmos晶体管关断的状态下第六pmos晶体管pm6弱导通并且第六nmos晶体管nm6相对强导通,因此通过第二内部节点ni2输出的稳定电压vstb 可以基本上等于正常状态的第一电源电压vddo。

[0145]

在图19a的稳定电压生成器673a和图19c的稳定电压生成器673c 中的每一个的情况下,由于当第一电源电压vddo是除了0v以外的正常状态的电压时第六pmos晶体管pm6被弱导通,因此稳定电压vstb可以有些缓慢地增加到第一电源电压vddo的电平。与此相比,在图19d的稳定电压生成器673d的情况下,通过第一电源电压vddo 导通的第六nmos晶体管nm6可以将稳定电压vstb迅速增加到第一电源电压vddo的电压电平。

[0146]

图19e是示出根据另一实施例的适于用作图18的稳压器670的稳压器670e的电路图。参照图19e,根据本公开的另一实施例的稳压器 670e包括分压器671e和稳定电压生成器673e。图19e的稳定电压生成器673e可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673e的重复描述。

[0147]

分压器671e连接到焊盘,并且通过第一内部节点ni1输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压v_div。在图 19e的实施例中,分压器671e可以包括在焊盘和第一内部节点ni1之间并联连接的n个第一二极管da1、da2、

……

、和dan,以及在第一内部节点ni1和接地节点之间并联连接的m个第二二极管db1、 db2、

……

、和dbm。第一二

极管da1至dan的数量n和第二二极管db1 至dbm的数量m是自然数,并且可以是相同的数或不同的数。当n和m 的值为1时,图19e的分压器671e可以与图19a的分压器671a基本上相同。根据本公开的实施例,n和m可以是任意自然数。

[0148]

在图19e的实施例中,稳定电压生成器673e与图19a的稳定电压生成器673a基本上相同。然而,本公开的实施例不限于此,图19e的稳压器670e可以包括图19b的稳定电压生成器673b或图19d的稳定电压生成器673d,而不是稳定电压生成器673e。

[0149]

图19f是示出根据另一实施例的适于用作图18的稳压器670的稳压器670f的电路图。参照图19f,根据本公开的另一实施例的稳压器 670f包括分压器671f和稳定电压生成器673f。图19f的稳定电压生成器 673f可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673f的重复描述。

[0150]

分压器671e连接到焊盘,并且通过第一内部节点ni1输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压v_div。在图 19f的实施例中,分压器671f可以包括在焊盘和第一内部节点ni1之间串联连接的p个第一二极管dc1、dc2、

……

、和dcp,以及在第一内部节点ni1和接地节点之间串联连接的q个第二二极管dd1、 dd2、

……

、和ddq。第一二极管dc1至dcp的数量p和第二二极管dd1 至ddq的数量q是自然数,并且可以是相同的数或不同的数。当p和q 的值为1时,图19f的分压器671f可以与图19a的分压器671a基本上相同。根据本公开的实施例,p和q可以是任意自然数。

[0151]

在图19f的实施例中,稳定电压生成器673f与图19a的稳定电压生成器673a基本上相同。然而,本公开的实施例不限于此,图19f的稳压器670f可以包括图19b的稳定电压生成器673b或图19d的稳定电压生成器673d,而不是稳定电压生成器673f。

[0152]

图19g是示出根据本公开的另一实施例的适于用作图18的稳压器670的稳定电压生成器670g的电路图。参照图19g,稳压器670g包括分压器671g和稳定电压生成器673g。图19g的稳定电压生成器673g 可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673g的重复描述。

[0153]

分压器671g连接到焊盘,并且通过第一内部节点ni1输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压v_div。在图 19g的实施例中,分压器671g可以包括在焊盘和第一内部节点ni1之间并联连接的r个第一二极管de1、de2、

……

、和der,以及在第一内部节点ni1与接地节点之间串联连接的s个第二二极管df1、df2、

……

、和dfs。第一二极管de1至der的数量r和第二二极管df1至dfs的数量s 是自然数,并且可以是相同的数或不同的数。当r和s的值为1时,图 19g的分压器671g可以与图19a的分压器671a基本上相同。根据本公开的实施例,r和s可以是任意自然数。

[0154]

在图19g的实施例中,稳定电压生成器673g与图19a的稳定电压生成器673a基本上相同。然而,本公开的实施例不限于此,图19g的稳压器670g可以包括图19b的稳定电压生成器673b或图19d的稳定电压生成器673d,而不是稳定电压生成器673g。

[0155]

图19h是示出根据另一实施例的适于用作图18的稳压器670的稳压器670h的电路图。参照图19h,根据本公开的另一实施例的稳压器 670h包括分压器671h和稳定电压生成器673h。图19h的稳定电压生成器673h可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673h的重复描述。

[0156]

分压器671h连接到焊盘,并且通过第一内部节点ni1输出通过对通过焊盘施加的

电压v_pad进行分压而生成的分压电压v_div。在图 19h的实施例中,分压器671h可以包括在焊盘和第一内部节点ni1之间串联连接的i个第一二极管dg1、dg2、

……

、和dgi,以及在第一内部节点ni1和接地节点之间并联连接的j个第二二极管dh1、 dh2、

……

、和dhj。第一二极管dg1至dgi的数量i和第二二极管dh1 至dhj的数量j是自然数,并且可以是相同的数或不同的数。当i和j的值为1时,图19h的分压器671h可以与图19a的分压器671a基本上相同。根据本公开的实施例,i和j可以是任意自然数。

[0157]

在图19h的实施例中,稳定电压生成器673h与图19a的稳定电压生成器673a基本上相同。然而,本公开的实施例不限于此,图19h的稳压器670h可以包括图19b的稳定电压生成器673b或图19d的稳定电压生成器673d,而不是稳定电压生成器673h。

[0158]

图19i是示出根据另一实施例的适于用作图18的稳压器670的稳压器670i的电路图。参照图19i,根据本公开的另一实施例的稳压器 670i包括分压器671i和稳定电压生成器673i。图19i的稳定电压生成器 673i可以与图19a的稳定电压生成器673a基本上相同。因此,省略了对稳定电压生成器673i的重复描述。

[0159]

分压器671i连接到焊盘,并且通过第一内部节点ni1输出通过对通过焊盘施加的电压v_pad进行分压而生成的分压电压v_div。在图 19i的实施例中,分压器671i可以包括在焊盘和第一内部节点ni1之间串联连接的x个第一二极管di1、di2、

……

、和dix,在焊盘和第一内部节点ni1之间并联连接的y个第二二极管dj1、dj2、

……

、和djy,在第一内部节点ni1和接地节点之间串联连接的u个第三二极管dk1、 dk2、

……

、和dku,以及在第一内部节点ni1和接地节点之间并联连接的v个第四二极管dl1、dl2、

……

、和dlv。数x、y、u和v是自然数,并且可以是相同的数或不同的数。在图19i的实施例中,稳定电压生成器673i与图19a的稳定电压生成器673a基本上相同。然而,本公开的实施例不限于此,图19i的稳压器670i可以包括图19b的稳定电压生成器673b或图19d的稳定电压生成器673d,而不是稳定电压生成器 673i。

[0160]

图20是示出根据本公开的另一实施例的输出驱动电路700的电路图。

[0161]

参照图20,根据本公开的实施例的输出驱动电路700包括在焊盘720和接地节点之间顺序地串联连接的第一、第二和第三晶体管nm1、 nm2和nm3、输入/输出控制逻辑710、栅极控制逻辑750、反相器inv 和稳压器770。输入/输出控制逻辑710接收时钟信号clk和使能信号 enb,并且将第一控制信号ng输出到第三晶体管nm3。栅极控制逻辑750接收焊盘720的电压pad_r。另外,栅极控制逻辑750将反馈电压vfgb输出到第一晶体管nm1的栅极端子。反相器inv反转使能信号enb并且将反转后的使能信号enb_in输出到栅极控制逻辑750。另外,栅极控制逻辑750接收第二控制信号vsel。同时,焊盘720通过外部电阻器r0连接到外部高电压vddh。另外,输出驱动电路700可以进一步包括内部电阻器r1,内部电阻器r1连接在焊盘720和栅极控制逻辑750之间。如上所述,内部电阻器r1可以用作esd保护电阻器。

[0162]

图20的输出驱动电路700可以与图14的输出驱动电路500基本上相同,除了输出驱动电路700进一步包括稳压器770。同时,图20的输出驱动电路700与图18的输出驱动电路600之间的差异在于栅极控制逻辑750另外地接收第二控制信号vsel。因此,图20的栅极控制逻辑 750可以被实施为图15的栅极控制逻辑550a或图16的栅极控制逻辑 550b中的一个。稳压器770连接到焊盘720以接收施加到焊盘720的电压,并且将稳定电压vstb输出到第二晶体管nm2的栅极端子。图20 的稳压器770可以与图18的稳压器670基本上相同。因此,图

20的稳压器770可以被实施为分别在图19a、图19b、图19c、图19d、图19e、图19f、图19g、图19h和图19i中示出的稳压器670a、670b、670c、 670d、670e、670f、670g、670h、670i中的任意一个。

[0163]

图21和图22是当也被称为内部电源电压的第一电源电压vddo 为0v时图18的输出驱动电路600的操作波形图。更具体地,图21和图 22示出了当图18的输出驱动电路600包括图19d所示的稳压器670d时的操作波形图。

[0164]

参照图21,示出了施加到焊盘的外部高电压vddh为第五电平v5 的实施例。在实施例中,第五电平v5可以是3.3v。图21还示出当施加到焊盘的外部高电压vddh为3.3v并且第一电源电压vddo为0v 时的输出到第一内部节点ni1的分压电压v_div和输出到第二内部节点ni2的稳定电压vstb。分压电压v_div可以具有第六电平v6的值。例如,第六电平v6可以是1.65v,其是外部高电压vddh的电平的一半。在这种情况下,稳定电压vstb也可以是等于分压电压v_div的第六电平v6,即1.65v。因此,在根据本公开的实施例的输出驱动电路600的情况下,当第一电源电压vddo为0v且施加到焊盘的外部高电压vddh为相对较高的第五电平v5(例如3.3v)时,可以满足第二晶体管nm2的可靠性条件,如下面将参照图22更详细地描述的。

[0165]

参照图22,当施加到焊盘的外部高电压vddh是第五电平v5并且第一电源电压vddo是0v时,分别示出了第一至第三晶体管nm1至 nm3的栅极电压、漏极电压和源极电压。

[0166]

在第一晶体管nm1的情况下,在图22的第一曲线图中,漏极电压是第五电平v5,其是施加到焊盘的外部高电压vddh,并且栅极电压是从栅极控制逻辑650施加的反馈电压vfgb。在这种情况下,反馈电压vfgb也具有第五电平v5的值。第一晶体管nm1的源极电压是节点 a node a的电压,并且具有比漏极电压略有减小的第七电平v7的值。在实施例中,外部高电压vddh,即,作为外部高电压vddh的第五电平v5,可以为3.3v,因此反馈电压vfgb也可以为3.3v。在这种情况下,作为第一晶体管nm1的源极电压的第七电平v7可以为比3.3v 略有减小的大约3.16v。

[0167]

同时,在第二晶体管nm2的情况下,在图22的第二曲线图中,漏极电压可以具有作为节点a node a的电压的第七电平v7的值,并且栅极电压可以具有作为从稳压器670施加的稳定电压vstb的第八电平v8。如上所述,当作为外部高电压vddh的第五电平v5为3.3v时,第七电平v7可以为3.16v。另外,如以上参照图21所述,稳定电压vstb可以是1.65v。同时,第二晶体管nm2的源极电压可以是节点bnode b的电压,并且可以是比栅极电压略有减小的第九电平v9。在实施例中,第九电平v9可以是1.53v。

[0168]

最后,参照图22的最后一个曲线图,第三晶体管nm3的漏极电压可以具有作为节点b node b的电压的第九电平v9的值。另外,第三晶体管nm3的栅极从输入/输出控制逻辑610接收第一控制信号ng。然而,由于驱动输入/输出控制逻辑510的第一电源电压vddo是0v,所以第一控制信号ng也可以是0v。因此,在第三晶体管nm3的情况下,漏极电压为第九电平v9,例如1.53v,并且栅极电压和源极电压为0v。

[0169]

参照图21和图22,当施加到焊盘的外部高电压vddh为3.3v并且第一电源电压vddo为0v时,第一至第三晶体管nm1至nm3的所有栅极

‑

漏极电压v

gd

、栅极

‑

源极电压v

gs

和漏极

‑

源极电压v

ds

可以小于用于确保第一至第三晶体管nm1至nm3的可靠性的给定值(例如, 1.98v)。因此,满足了第一至第三晶体管nm1至nm3的可靠性条件。

[0170]

图23和图24是当内部电源电压vddo为第十电平v10时图18的输出驱动电路600的操作波形图。在实施例中,内部电源电压vddo可以是1.8v。参照图23,在内部电源电压vddo为的第十电平v10(例如,1.8v)的状态下施加到焊盘的外部高电压vddh从0v增加到第五电平v5,例如,3.3v。因此,输出到第一内部节点ni1的分压电压 v_div可以增加以达到第八电平v8,即,大约1.65v电平,并且稳定电压vstb可以从第九电平v9(例如,大约1.6v)增加,然后稳定到大约1.94v电平。因此,如将在下面参照图24更详细地描述的,第一至第三晶体管nm1至nm3的所有栅极

‑

漏极电压v

gd

、栅极

‑

源极电压 v

gs

和漏极

‑

源极电压v

ds

可以小于1.98v。

[0171]

参照图24,当内部电源电压vddo为第十电平v10并且外部高电压vddh从0v增加到第五电平v5时,分别示出了第一至第三晶体管nm1至nm3的栅极电压、漏极电压和源极电压。例如,第十电平v10 可以是1.8v,并且第五电平v5可以是3.3v。如图24所示,当内部电源电压vddo为1.8v且外部高电压vddh从0v增加至3.3v时,第一至第三晶体管nm1至nm3的所有栅极

‑

漏极电压v

gd

、栅极

‑

源极电压v

gs

和漏极

‑

源极电压v

ds

可以在小于1.98v的范围内变化。因此,满足了第一至第三晶体管nm1至nm3的可靠性条件。

[0172]

在本说明书和附图中所公开的本公开的实施例仅是为了提供特定示例以容易地描述本公开的技术内容并帮助理解本公开,而不旨在限制本公开的实施例的范围。对于本公开所属领域的技术人员显而易见的是,除了本文所公开的实施例之外,还可以实施基于本公开的技术精神的其他修改的示例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1