一种斩波放大器频率补偿电路的制作方法

1.本技术属于生物电子领域,具体设计一种采用并联直流伺服环路对斩波放大器进行频率补偿的补偿电路。

背景技术:

2.脑电信号提取电路中的前置放大器常采用斩波放大器。感兴趣的脑电信号包括局部场电位(local field potential,lfp)信号和动作电位(action potential,ap)信号等。局部场电位信号的频率范围为0.5hz~200hz,动作电位信号的频率范围为200hz~5khz。为了抑制电极引起的直流漂移(electrode dc offset,edo)以及从脑电信号中分离lfp和ap,斩波放大器的下限截止频率需要在一个极低的频率(0.1hz~0.5hz)和一个较高的频率(200hz~300hz)之间进行切换。这一功能可以通过在斩波放大器中加入直流伺服环路(dc servo loop,dsl)来实现。但是,现有的dsl存在着以下两个缺点:1)若采用单个一阶直流伺服回路,其阻带衰减速率只有20db/10倍频,在提取ap信号时,不能完全滤除lfp信号产生的影响,易使lfp和ap信号发生混叠;2)对于ap信号,若采用单个二阶直流伺服回路,虽然阻带衰减速率达到40db/10倍频(满足分离提取lfp与ap的要求),但是,此时斩波放大器的系统极点为一对共轭极点且分布在s域的虚轴上,其品质因数为无穷大,导致ap信号的幅频响应在下限截止频率处存在尖峰,使得斩波放大器的幅频响应在下限截止频率处不能平滑地过渡到中频带。

技术实现要素:

3.本发明的目的是解决和克服上述两项现有技术的缺陷,提供一种斩波放大器频率补偿电路。

4.为了实现上述目的,本发明提供了如下技术方案:

5.一种斩波放大器频率补偿电路,包括:主斩波放大电路、负反馈回路、一阶直流伺服环路、二阶直流伺服环路;所述主斩波放大电路、负反馈回路、一阶直流伺服环路、二阶直流伺服环路均为双端输入双端输出的四端口网络;

6.所述主斩波放大电路与所述负反馈回路并联构成闭环斩波放大器,所述主斩波放大电路用于提供高的开环增益,所述负反馈回路用于提供稳定的闭环增益;

7.所述一阶直流伺服环路与所述主斩波放大电路并联,所述一阶直流伺服环路用于提供斩波放大器的频率补偿;

8.所述二阶直流伺服环路与所述主斩波放大电路并联,所述二阶直流伺服环路用于提供下限截止频率和快的阻带衰减速率。

9.进一步地,所述主斩波放大电路包括:依次级联的全差分斩波开关、差分电容、全差分运算放大器和全差分斩波开关;

10.所述负反馈回路、一阶直流伺服环路和二阶直流伺服环路分别与所述全差分运算放大器和全差分斩波开关组成的级联网络并联。

11.进一步地,所述负反馈回路包括:依次级联的全差分斩波开关和差分电容。

12.进一步地,所述一阶直流伺服环路包括:依次级联的有源全差分积分器、全差分斩波开关和差分电容。

13.进一步地,所述二阶直流伺服环路包括:依次级联的有源全差分积分器、有源全差分积分器、全差分斩波开关和差分电容。

14.本发明的一种斩波放大器频率补偿电路,具有如下优点和有益效果:

15.1)采用二阶直流伺服环路与一阶直流伺服环路的并联结构。阻带衰减速率为40db/十倍频,满足分离lfp和ap信号的阻带衰减要求;

16.2)二阶直流伺服环路与一阶直流伺服环路的并联结构,可以对闭环斩波放大器的下限截止频率处进行频率补偿;因为当二阶直流伺服环路与一阶直流伺服环路的并联时,由于系统的品质因数为1,且系统的零点位于原点处,其极点为s域左半平面的共轭复根,所以可以有效消除ap信号幅频响应中下限截止频率处的尖峰。

附图说明

17.通过参考附图会更加清楚的理解本发明的特征和优点,附图是示意性的而不应理解为对本发明进行任何限制,在附图中:

18.图1为本发明具体实施例的组成框图;

19.图2为本发明具体实施例中的全差分斩波开关101的实施示意图;

20.图3为本发明具体实施例中的伪电阻r

3011

的实施示意图;

21.图4为本发明与现有技术的幅频响应的对比图。

具体实施方式

22.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

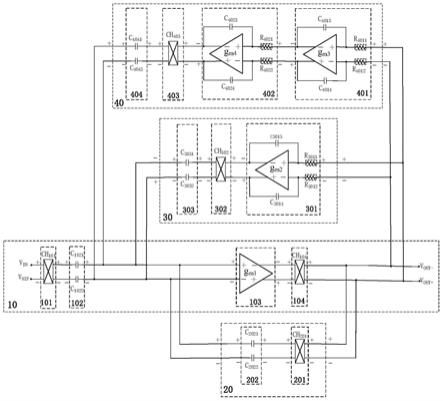

23.如图1

‑

3所示,一种斩波放大器频率补偿电路,包括:主斩波放大电路10、负反馈回路20、一阶直流伺服环路30、二阶直流伺服环路40,主斩波放大电路10、负反馈回路20、一阶直流伺服环路30、二阶直流伺服环路40均为双端输入双端输出的四端口网络;其中,

24.主斩波放大电路10包括:依次级联的全差分斩波开关101、差分电容102、全差分运算放大器103和全差分斩波开关104;且全差分斩波开关101的同相输入端接记录电极信号v

rec

,其反相输入端接参考电极信号v

ref

;全差分运算放大器103的反相输出端、同相输出端分别连接全差分斩波开关104的同相输入端、反相输入端;全差分斩波开关104的同相输出端输出斩波放大器的反相输出信号v

out

‑

,其反相输出端输出斩波放大器的同相输出信号v

out+

;

25.如图2所示,全差分斩波开关101包括:nmos管m

1011

、nmos管m

1012

、nmos管m

1013

、nmos管m

1014

;其中,四个nmos管的w=l=1μm,nmos管m

1011

的栅极连接脉冲信号clka,其源极为全差分斩波开关101的同相输入端v

in+

,其漏极为全差分斩波开关101的同相输出端v

o+

;nmos管m

1012

的栅极连接脉冲信号clkb,其源极为全差分斩波开关的反相输入端v

in

‑

,其漏极与全差

分斩波开关101的同相输入端v

in+

相连;nmos管m

1013

的栅极连接脉冲信号clka,其源极为全差分斩波开关101的反相输入端v

in

‑

,其漏极为全差分斩波开关的反相输出端v

o

‑

;nmos管m

1014

的栅极连接脉冲信号clkb,其源极为全差分斩波开关101的反相输出端v

o

‑

,其漏极为全差分斩波开关的同相输出端v

o+

;

26.差分电容102包括:电容值为12pf的电容c

1021

、电容值为12pf的电容c

1022

;其中,电容c

1021

的输入端、输出端分别为差分电容102的同相输入端、同相输出端;电容c

1022

的输入端和输出端分别为差分电容102的反相输入端、反相输出端;

27.全差分运算放大器103为通用的全差分运算放大器;

28.全差分斩波开关104与全差分斩波开关101具有相同结构。

29.负反馈回路20包括:依次级联的全差分斩波开关201、差分电容202;且全差分斩波开关201的同相输入端、反相输入端分别连接全差分斩波开关104的同相输出端、反相输出端;差分电容202的同相输出端、反相输出端分别连接全差分运算放大器103的同相输入端、反相输入端;

30.全差分斩波开关201与全差分斩波开关101结构相同;

31.差分电容202包括:电容值为0.12pf的电容c

2021

、电容值为0.12pf的电容c

2022

;其中,电容c

2021

的输入端、输出端分别为差分电容202的同相输入端、同相输出端;电容c

2022

的输入端和输出端分别为差分电容202的反相输入端、反相输出端。

32.一阶直流伺服环路30包括:依次级联的有源全差分积分器301、全差分斩波开关302、差分电容303;且有源全差分积分器301的同相输入端、反相输入端分别连接全差分斩波开关104的反相输出端、同相输出端;其同相输出端、反相输出端分别连接全差分斩波开关302的反相输入端、同相输入端;差分电容303的同相输出端、反相输出端分别连接全差分运算放大器103的同相输入端、反相输入端;

33.有源全差分积分器301包括:全差分运算放大器g

m2

、伪电阻r

3011

、伪电阻r

3012

、电容c

3013

、电容c

3014

;其中,伪电阻r

3011

的阻值为1gω、伪电阻r

3012

的阻值为1gω、电容c

3013

的容值为0.5pf、电容c

3014

的容值为0.5pf;全差分运算放大器g

m2

为通用的全差分运算放大器;如图3所示,伪电阻r

3011

包括:直流电压v

p

、pmos管m

30111

、pmos管m

30112

;其中,pmos管m

30111

的w=l=1μm、pmos管m

30112

的w=l=1μm;pmos管m

30111

与pmos管m

30112

各自的栅极均与v

p

相连;pmos管m

30111

的源极与pmos管m

30112

的源极相连;其各自的漏极则分别为伪电阻r

3011

的两个端子;伪电阻r

3012

与伪电阻r

3011

结构相同;电容c

3013

的输入端、输出端分别连接全差分运算放大器g

m2

的同相输入端、反相输出端;电容c

3014

的输入端、输出端分别连接全差分运算放大器g

m2

的反相输入端、同相输出端;伪电阻r

3011

的输出端与全差分运算放大器g

m2

的同相输入端相连,其输入端为有源全差分积分器301的同相输入端;伪电阻r

3012

的输出端与全差分运算放大器g

m2

的反相输入端相连,其输入端为有源全差分积分器301的反相输入端;全差分运算放大器g

m2

的同相输出端、反相输出端分别为有源全差分积分器301的同相输出端、反相输出端;

34.全差分斩波开关302与全差分斩波开关101结构相同;

35.差分电容303包括:电容值为0.12pf的电容c

3031

、电容值为0.12pf的电容c

3032

;其中,电容c

3031

的输入端、输出端分别为差分电容303的同相输入端、同相输出端;电容c

3032

的输入端和输出端分别为差分电容303的反相输入端、反相输出端。

36.二阶直流伺服环路40包括:依次级联的有源全差分积分器401、有源全差分积分器

402、全差分斩波开关403、差分电容404;且有源全差分积分器401的同相输入端、反相输入端分别连接全差分斩波开关104的反相输出端、同相输出端;有源全差分积分器402的同相输入端、反相输入端分别连接有源全差分积分器401的反相输出端、同相输出端;其同相输出端、反相输出端分别连接全差分斩波开关403的反相输入端、同相输入端;差分电容404的同相输出端、反相输出端分别连接全差分运算放大器103的反相输入端、同相输入端;

37.有源全差分积分器401包括:全差分运算放大器g

m3

、伪电阻r

4011

、伪电阻r

4012

、电容c

4013

、电容c

4014

;其中,伪电阻r

4011

的阻值为1gω、伪电阻r

4012

的阻值为1gω、电容c

4013

的容值为0.5pf、电容c

4014

的容值为0.5pf;伪电阻r

4011

、伪电阻r

4012

与伪电阻r

3011

结构相同;全差分运算放大器g

m3

为通用的全差分运算放大器;电容c

4013

的输入端、输出端分别连接全差分运算放大器g

m3

的同相输入端、反相输出端;电容c

4014

的输入端、输出端分别连接全差分运算放大器g

m3

的反相输入端、同相输出端;伪电阻r

4011

的输出端与全差分运算放大器g

m2

的同相输入端相连,其输入端为有源全差分积分器401的同相输入端;伪电阻r

4012

的输出端与全差分运算放大器g

m3

的反相输入端相连,其输入端为有源全差分积分器401的反相输入端;全差分运算放大器g

m3

的同相输出端、反相输出端分别为有源全差分积分器401的同相输出端、反相输出端;

38.有源全差分积分器402包括:全差分运算放大器g

m4

、伪电阻r

4021

、伪电阻r

4022

、电容c

4023

、电容c

4024

;其中,伪电阻r

4021

的阻值为1gω、伪电阻r

4022

的阻值为1gω、电容c

4023

的容值为0.5pf、电容c

4024

的容值为0.5pf;伪电阻r

4021

、伪电阻r

4022

与伪电阻r

3011

结构相同;全差分运算放大器g

m4

为通用的全差分运算放大器;电容c

4023

的输入端、输出端分别连接全差分运算放大器g

m4

的同相输入端、反相输出端;电容c

4024

的输入端、输出端分别连接全差分运算放大器g

m4

的反相输入端、同相输出端;伪电阻r

4021

的输出端与全差分运算放大器g

m4

的同相输入端相连,其输入端为有源全差分积分器402的同相输入端;伪电阻r

4022

的输出端与全差分运算放大器g

m4

的反相输入端相连,其输入端为有源全差分积分器402的反相输入端;全差分运算放大器g

m4

的同相输出端、反相输出端分别为有源全差分积分器402的同相输出端、反相输出端;

39.全差分斩波开关403与全差分斩波开关101结构相同;

40.差分电容404包括:电容值为0.12pf的电容c

4041

、电容值为0.12pf的电容c

4042

;其中,电容c

4041

的输入端、输出端分别为差分电容404的同相输入端、同相输出端;电容c

4042

的输入端和输出端分别为差分电容404的反相输入端、反相输出端。

41.本发明的传输函数如下:

[0042][0043]

其中,

[0044][0045][0046]

公式(1)中,a0为斩波放大器的闭环增益,表达式如公式(2)所示;ω0为斩波放大器

的下限截止频率,表达式如公式(3)所示;本发明和传输函数的零点s0=s1=0,极点

[0047][0048][0049]

本发明通过将二阶直流伺服环路与一阶直流伺服环路并联,使得闭环斩波放大器的系统极点为一对共轭极点且分布在s域的左半平面,其幅频响应如图4所示。本发明与采用单个一阶直流伺服环路的闭环斩波放大器相比,其阻带衰减率为40db/十倍频,满足分离lfp和ap信号的阻带衰减要求。本发明与采用单个二阶直流伺服环路的闭环斩波放大器相比,其幅频响应在下限截止频率处不存在尖峰,可平滑地过渡到中频带,验证了本发明的有效性。

[0050]

虽然结合附图描述了本发明的实施例,但是本领域技术人员可以在不脱离本发明的精神和范围的情况下作出各种修改和变型,这样的修改和变型均落入由所附权利要求所限定的范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1