一种分区域玻纤布拼接的半固化片、PCB板及拼接方法与流程

一种分区域玻纤布拼接的半固化片、pcb板及拼接方法

技术领域

1.本发明涉及半固化片设计领域,尤其是涉及一种分区域玻纤布拼接的半固化片、pcb板及拼接方法。

背景技术:

2.半固化片(pp)是由玻纤布(玻璃纤维布),浸渍上环氧树脂胶液,再经热处理(烘干)而制成的薄片材料。

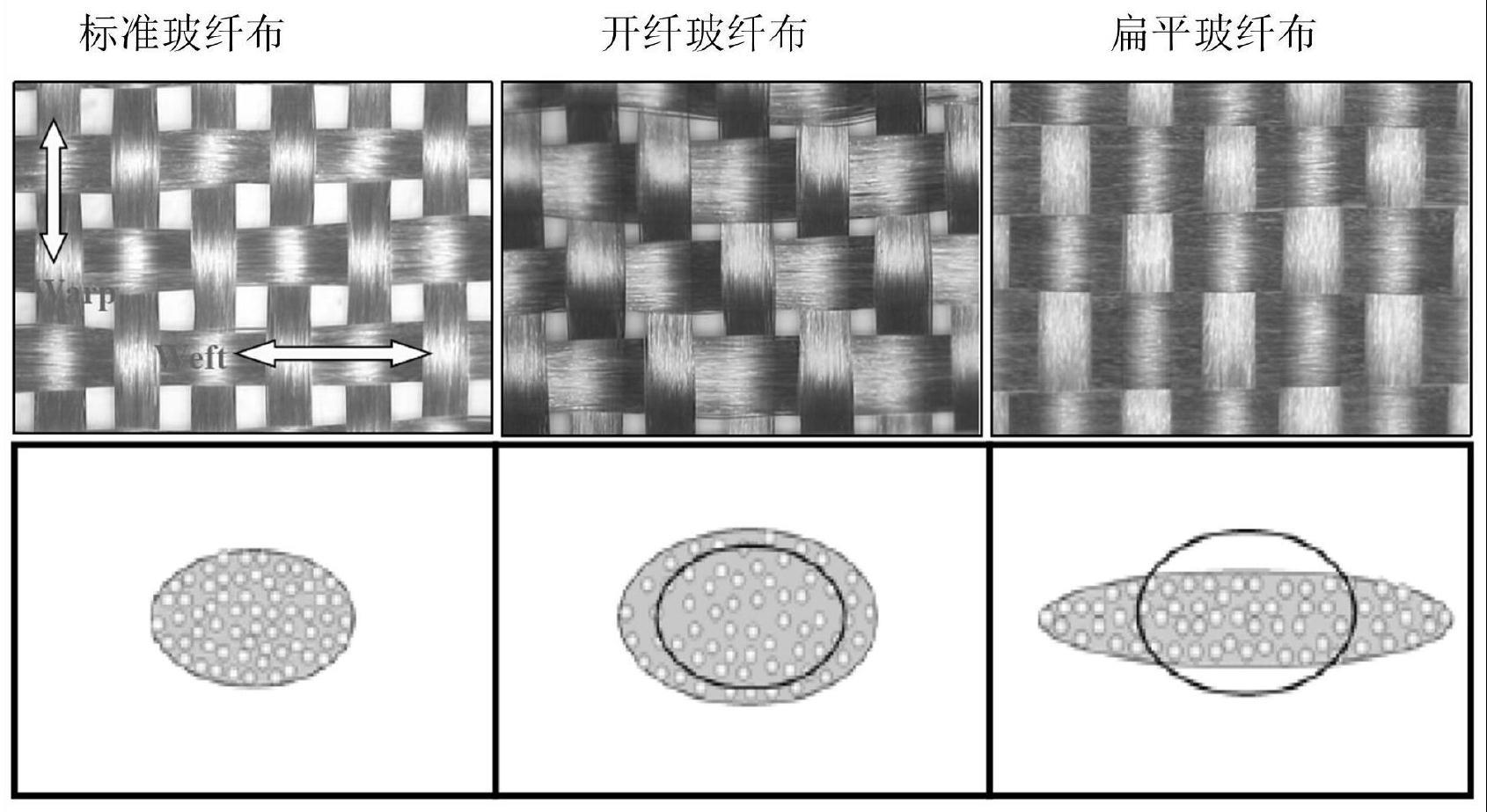

3.如图1所示,玻纤布有标准(standard)、开纤(expanded)、扁平(spread)区分。玻纤布的选择,对应的玻纤效应对高速信号的完整性影响很大,一般高速pcb板材选用低介电常数玻纤布,例如选择扁平布(经过扁平化处理的玻纤布)。

4.现有技术中,即使某一走线层,有不同的速率分布(部分是高速走线,其他部分是低速走线),为了保证信号的完整性,降低玻纤效应的影响,半固化片(pp)中统一选择低介电常数玻纤布,造成了半固化片等成本的提高。

技术实现要素:

5.本发明为了解决现有技术中存在的问题,创新提出了一种分区域玻纤布拼接的半固化片、pcb板、拼接方法,有效解决由于现有技术造成半固化片生产成本高的问题,有效的降低半固化片生产成本,同时兼顾信号的完整性,保证了产品的质量。

6.本发明第一方面提供了一种分区域玻纤布拼接的半固化片,位于第一走线层以及与第一走线层相邻的第二走线层之间,包括:第一玻纤布以及第二玻纤布,第一玻纤布位于半固化片中高速信号线经过的区域,第二玻纤布位于半固化片中低速信号线经过的区域,其中,高速信号线为第一走线层中通过过孔与第二走线层通信连接的高速信号走线路径,低速信号线为第一走线层中通过过孔与第二走线层通信连接的低速信号走线路径,第一玻纤布成本大于第二玻纤布。

7.可选地,高速信号为上升时间不大于第一阈值的信号,低速信号为上升时间大于第一阈值的信号。

8.可选地,第一阈值为第一倍数的信号传输延时。

9.可选地,第一玻纤布为扁平化处理的玻纤布,第二玻纤布为未经过扁平化处理的玻纤布。

10.本发明第二方面提供了一种pcb板,包括若干本发明第一方面所述的分区域玻纤布拼接的半固化片。

11.可选地,相邻走线层之间的半固化片为所述分区域玻纤布拼接的半固化片。

12.本发明第三方面提供了一种分区域玻纤布拼接半固化片的方法,位于第一走线层以及与第一走线层相邻的第二走线层之间,包括:

13.在第一走线层根据信号上升时间划分为高速信号线以及低速信号线;

14.半固化片层中,高速信号线经过的区域设置第一玻纤布,低速信号线经过的区域

设置第二玻纤布,其中,高速信号线为第一走线层中通过过孔与第二走线层通信连接的高速信号走线路径,低速信号线为第一走线层中通过过孔与第二走线层通信连接的低速信号走线路径,第一玻纤布成本大于第二玻纤布。

15.可选地,还包括:对设置完成后的半固化片分别进行信号阻抗测试以及插损测试,任一测试不通过,则调整半固化片的中第一玻纤布以及第二玻纤布的设置。

16.进一步地,调整半固化片的中第一玻纤布以及第二玻纤布的设置具体是:如果测试阻抗小于阻抗预设范围最小值,则增大第一玻纤布或第二玻纤布的厚度;如果测试阻抗大于阻抗预设范围最大值,则减小第一玻纤布或第二玻纤布的厚度。

17.可选地,调整半固化片的中第一玻纤布以及第二玻纤布的设置具体是:如果测试插损大于插损预设值,则减小第一玻纤布或第二玻纤布的厚度。

18.本发明采用的技术方案包括以下技术效果:

19.1、本发明有效解决由于现有技术造成半固化片生产成本高的问题,有效的降低半固化片生产成本,同时兼顾信号的完整性,保证了产品的质量。

20.2、本发明技术方案的pcb板中相邻走线层之间的半固化片为所述分区域玻纤布拼接的半固化片,有效的降低pcb板的生产成本,同时兼顾信号的完整性,保证了产品的质量。

21.3、本发明技术方案中对设置完成后的半固化片分别进行信号阻抗测试以及插损测试,任一测试不通过,则调整半固化片的中第一玻纤布以及第二玻纤布的设置,保证了信号传输效果。

22.应当理解的是以上的一般描述以及后文的细节描述仅是示例性和解释性的,并不能限制本发明。

附图说明

23.为了更清楚说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单介绍,显而易见的,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

24.图1为现有玻纤布分类示意图;

25.图2为本发明方案中实施例一的结构示意图;

26.图3为本发明方案中实施例三方法的流程示意图;

27.图4为本发明方案中实施例四方法的流程示意图。

具体实施方式

28.为能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

29.实施例一

30.如图2所示,本发明提供了一种分区域玻纤布拼接的半固化片,位于第一走线层l1

以及与第一走线层l1相邻的第二走线层l2之间,包括:第一玻纤布1以及第二玻纤布2,第一玻纤布1位于半固化片(pp)中高速信号线经过的区域,第二玻纤布2位于半固化片中低速信号线经过的区域,其中,高速信号线为第一走线层l1中通过过孔与第二走线层l2通信连接的高速信号走线路径,低速信号线为第一走线层l1中通过过孔与第二走线层l2通信连接的低速信号走线路径,第一玻纤布1成本大于第二玻纤布2。

31.高速信号为上升时间不大于第一阈值的信号,低速信号为上升时间大于第一阈值的信号,具体地,第一阈值为第一倍数的信号传输延时,第一倍数可以为6。高速信号可以是高速差分信号,例如pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)、usb(universal serial bus,通用串行总线)、hdmi(high definition multimedia interface,高清多媒体接口)、dp(displayport,数字式视频接口标准)以及bga(球栅阵列封装)区域到sodimm(small outline dual in

‑

line memory module,小型双列直插式内存模块)的走线信号等,低速信号可以是uart(universal asynchronous receiver/transmitter,通用异步收发传输器)、spi(serial peripheral interface,串行外设接口)、i2c(inter-integrated circuit,双向二线制同步串行总线)等信号。

32.第一玻纤布1为扁平化处理的玻纤布(扁平玻纤布),即低介电常数玻纤布;第二玻纤布2为未经过扁平化处理的玻纤布,例如标准玻纤布等。

33.本发明有效解决由于现有技术造成半固化片生产成本高的问题,有效的降低半固化片生产成本,同时兼顾信号的完整性,保证了产品的质量。

34.实施例二

35.本发明技术方案还提供了一种pcb板,包括若干实施例一的分区域玻纤布拼接的半固化片。

36.彼此通信连接的相邻走线层之间的半固化片为分区域玻纤布拼接的半固化片。

37.特殊地,如果第一走线层与第二走线层之间通信连接,且第一走线层与第二走线层之间跨越多个走线层,第一走线层的高速信号线通过对多个半固化片与第二走线层中通信连接,多个半固化片均优先选用第一玻纤布。

38.本发明技术方案的pcb板中相邻走线层之间的半固化片为所述分区域玻纤布拼接的半固化片,有效的降低pcb板的生产成本,同时兼顾信号的完整性,保证了产品的质量。

39.实施例三

40.如图3所示,本发明技术方案还提供了一种分区域玻纤布拼接半固化片的方法,位于第一走线层以及与第一走线层相邻的第二走线层之间,包括:

41.s1,在第一走线层根据信号上升时间划分为高速信号线以及低速信号线;

42.s2,半固化片层中,高速信号线经过的区域设置第一玻纤布,低速信号线经过的区域设置第二玻纤布,其中,高速信号线为第一走线层中通过过孔与第二走线层通信连接的高速信号走线路径,低速信号线为第一走线层中通过过孔与第二走线层通信连接的低速信号走线路径,第一玻纤布成本大于第二玻纤布。

43.其中,在步骤s1中,高速信号为上升时间不大于第一阈值的信号,低速信号为上升时间大于第一阈值的信号,具体地,第一阈值为第一倍数的信号传输延时,第一倍数可以为6。高速信号可以是高速差分信号,例如pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)、usb(universal serial bus,通用串行总线)、

hdmi(high definition multimedia interface,高清多媒体接口)、dp(displayport,数字式视频接口标准)以及bga(球栅阵列封装)区域到sodimm(small outline dual in

‑

line memory module,小型双列直插式内存模块)的走线信号等,低速信号可以是uart(universal asynchronous receiver/transmitter,通用异步收发传输器)、spi(serial peripheral interface,串行外设接口)、i2c(inter-integrated circuit,双向二线制同步串行总线)等信号。

44.在步骤s2中,第一玻纤布为扁平化处理的玻纤布(扁平玻纤布),即低介电常数玻纤布;第二玻纤布为未经过扁平化处理的玻纤布,例如标准玻纤布等。

45.本发明有效解决由于现有技术造成半固化片生产成本高的问题,有效的降低半固化片生产成本,同时兼顾信号的完整性,保证了产品的质量。

46.实施例四

47.如图4所示,本发明技术方案还提供了一种分区域玻纤布拼接半固化片的方法,位于第一走线层以及与第一走线层相邻的第二走线层之间,包括:

48.s1,在第一走线层根据信号上升时间划分为高速信号线以及低速信号线;

49.s2,半固化片层中,高速信号线经过的区域设置第一玻纤布,低速信号线经过的区域设置第二玻纤布,其中,高速信号线为第一走线层中通过过孔与第二走线层通信连接的高速信号走线路径,低速信号线为第一走线层中通过过孔与第二走线层通信连接的低速信号走线路径,第一玻纤布成本大于第二玻纤布;

50.s3,对设置完成后的半固化片分别进行信号阻抗测试以及插损测试,任一测试不通过,则调整半固化片的中第一玻纤布以及第二玻纤布的设置。

51.进一步地,调整半固化片的中第一玻纤布以及第二玻纤布的设置具体是:如果测试阻抗小于阻抗预设范围最小值,则增大第一玻纤布或第二玻纤布的厚度;如果测试阻抗大于阻抗预设范围最大值,则减小第一玻纤布或第二玻纤布的厚度。其中,阻抗预设范围可以是某一标准数值z及出生上下波动10%形成的范围,即[z*(1

‑

10%),z*(1+10%)],例如,标准数值z为85ω,则,阻抗预设范围为[76.5,93.5],阻抗预设范围最小值为76.5,阻抗预设范围最大值为93.5,使其测试阻符合阻抗预设范围。

[0052]

进一步地,调整半固化片的中第一玻纤布以及第二玻纤布的设置具体是:如果测试插损大于插损预设值,则减小第一玻纤布或第二玻纤布的厚度,使其测试插损小于插损预设值即可。

[0053]

本发明技术方案中对设置完成后的半固化片分别进行信号阻抗测试以及插损测试,任一测试不通过,则调整半固化片的中第一玻纤布以及第二玻纤布的设置,保证了信号传输效果。

[0054]

上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制,所属领域技术人员应该明白,在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1