用于校准倍频器的系统和方法与流程

1.本发明总体上涉及一种用于校准倍频器的系统和方法。

背景技术:

2.在许多射频(rf)系统中,诸如被设计为在基于lte或5g的蜂窝系统中运行的便携式无线设备中,各种各样的电路和系统被用于实现rf和基带功能。例如,大多数系统包括:rf下变频器,将从天线接收的rf信号下变频为基带和/或中频信号;模数转换器(adc),将下变频的rf信号数字化;处理器,执行对数字化的信号的计算和处理;数模转换器(dac),生成基带或中间信号以进行传输;rf上变频器,将基带或中间信号上变频为rf频率以通过天线进行传输。除了必需的信号路径电路装置(诸如,用于实现这些功能的放大器、混频器、滤波器和数据转换电路和处理电路)之外,这些功能中的每个功能可能需要时钟信号或振荡器信号才能运行。例如,rf下变频器和rf上变频器通常利用rf本地振荡器(lo)信号,并且adc、dac和处理器利用数字时钟信号。因此,这种rf系统附加地包括频率生成电路装置以支持rf、基带和处理功能。

3.许多rf系统使用频率生成系统,其中一个或多个压控振荡器(vco)的频率参考使用一个或多个锁相环(pll)电路的晶体振荡器的频率。一个或多个附加的pll或延迟锁定环(dll)还可以被用于生成用于数字处理器和/或数据转换器的高频时钟。在一些情况下,这些时钟和振荡器信号可以具有控制相位噪声和占空比的性能要求。在便携式设备中设计被配置为以成本有效的方式生成满足性能要求的多种时钟信号的频率生成系统在板空间、部件成本和功耗方面提出了许多挑战和权衡。

技术实现要素:

4.根据一个实施例,一种方法包括:通过可调倍频电路接收具有第一时钟频率的第一时钟信号;使用可调倍频电路,生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟频率的两倍;测量第二时钟信号的占空比参数,其中占空比参数取决于第一时钟信号的占空比或第二时钟信号的占空比;以及使用可调倍频电路,基于测量调整第一时钟信号的占空比或第二时钟信号的占空比。

5.根据另一个实施例,一种系统包括:可调倍频电路,包括时钟输入、时钟输出和占空比调整输入,可调倍频电路被配置为:在时钟输入处接收具有第一时钟频率的第一时钟信号;在时钟输出处生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟频率的两倍,并且基于在占空比调整输入处接收的占空比调整信号调整第一时钟信号的占空比或第二时钟信号的占空比;以及占空比测量和调整电路,被耦合到可调倍频电路的时钟输出和占空比调整输入,占空比测量和调整电路被配置为测量第二时钟信号的占空比参数并且基于测量的占空比参数生成占空比调整信号。

6.根据进一步的实施例,一种rf系统包括:rf前端,具有被配置为被耦合到天线的输入端口;测试音调生成电路;多路复用器,具有耦合到rf前端的输出的第一输入以及被耦合

到测试音调生成电路的输出的第二输入;可调倍频电路,包括时钟输入、时钟输入和占空比调整输入,可调倍频电路被配置为:在时钟输入处接收具有第一时钟频率的第一时钟信号;在时钟输出处生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟频率的两倍;并且基于在占空比调整输入处接收的占空比调整信号调整第一时钟信号的占空比或第二时钟信号的占空比;以及模数转换器(adc),具有耦合到可调倍频电路的时钟输出的时钟输入,耦合到多路复用器的输出的adc信号输入,以及被配置为提供第一时域数字信号的adc信号输出。

附图说明

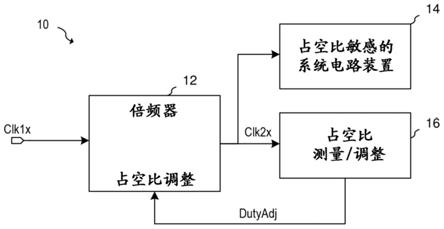

7.图1a和图1b示出了实施例倍频器系统;

8.图2a

‑

图2d示出了描述倍频器系统的性能的图表;

9.图3a

‑

图3i示出了实施例倍频器电路的示意图;

10.图4a和图4b示出了校准倍频器电路的实施例方法的框图;

11.图5a

‑

图5d示出了结合实施例倍频器电路的系统的示意图;并且图5e示出了校准图5a的系统的实施例方法的框图;

12.图6a

‑

图6c示出了结合实施例倍频器电路的系统的示意图;并且图6d示出了校准图6a的系统的实施例方法的框图。

13.图7a和图7b示出了实施例rf系统的示意图;以及

14.图8示出了可以被用于实现实施例系统的部分的处理系统的框图。

15.除非另外指出,否则不同附图中的对应的附图标记和符号通常指代对应的部分。绘制附图以清楚地示出优选实施例的相关方面,并且不一定按比例绘制。为了更清楚地说明某些实施例,指示相同结构、材料或工艺步骤的变化的字母可以在附图编号之后。

具体实施方式

16.下面将详细讨论当前优选实施例的制造和使用。然而,应当理解,本发明提供了可以在各种各样的特定环境中体现的许多可应用的发明构思。所讨论的特定实施例仅说明制造和使用本发明的特定方式,并且不限制本发明的范围。

17.将在特定上下文中针对优选实施例、用于校准在无线电收发器中使用的倍频器的系统和方法来描述本发明。

18.在各种实施例中,使用被配置为提供具有可调占空比的时钟信号的可调时钟倍增电路来将输入时钟信号的频率加倍。通过调整双倍时钟信号的占空比,将双倍时钟信号校准为占空比基本上为50%,双倍时钟信号可以被用于时钟占空比敏感的电路装置(诸如,adc或锁相环电路)。在一些实施例中,通过向adc提供测试音调(诸如,模拟测试音调)、监测adc转换器的杂散虚假响应以及迭代地调整时钟倍增电路的占空比以减小或最小化adc转换器的杂散虚假响应来校准占空比。在其它实施例中,可以在校准期间直接地监测双倍时钟信号,以确定并校准双倍时钟信号的占空比。

19.备选地或除了调整双倍时钟信号的占空比之外,可以在将输入时钟信号被加倍之前调整输入时钟信号的占空比。在各种情况下,输入时钟信号上存在占空比误差可能会导致双倍时钟信号上的交替的持续时间周期。当被用作对双倍时钟信号上的这种错误敏感的

电路的输入时,这些交替的持续时间周期可能会导致杂散行为。例如,表现出这种灵敏度的电路包括每次转换使用奇数个时钟周期的adc。因此,在各种实施例中,在将输入时钟信号加倍之前,可以将输入时钟信号的占空比调整或校准为基本上为50%,从而有利地减少了数据转换器和其它电路装置的杂散行为。

20.在一些便携式无线系统中,为数据转换器和锁相环(pll)电路计时所需的时钟频率可能会比通常用于数字处理电路计时的时钟频率更高。例如,在一些系统中,通常使用38.4mhz晶体来生成用于应用处理器的时钟信号,而在80mhz附近的较高时钟频率可以被用于为模数转换器和pll电路计时。在一些系统中,由于振荡器晶体的尺寸较大并且紧凑型便携式无线设备中可用的板空间有限,因此通常使用倍频电路装置(诸如,延迟锁定环(dll)、附加的pll或基于延迟的倍频电路)来获得用于向数据转换器和pll电路提供时钟信号的较高时钟频率。尽管基于延迟的倍频电路可能在物理上紧凑并且消耗相对较低的功率,但是一些倍频电路可能对晶体振荡器产生的时钟信号中的占空比误差敏感,并且可能附加地倾向于产生具有占空比偏离50%的倍频时钟信号。在一些情况下,这些占空比误差可能会降低占空比敏感电路装置的性能,占空比敏感电路装置以多倍的时钟信号为参考。

21.例如,在利用系统时钟的两个边沿执行采样和其它操作的模数转换器中,时钟的不对称可能导致杂散行为并且降低无杂散动态范围(sfdr)。时钟的占空比中的误差可能会转化为频率误差,从而产生两个频率之间的跳跃。另外,由于时钟的占空比偏离50%,依赖时钟的两个边沿的电荷泵电路可能会遇到操作困难。在利用奇数个系统时钟进行转换的模数转换器中,系统时钟的时钟周期长度中由倍频器的输入时钟的占空比不对称引起的周期性变化也可能导致杂散行为并且降低无杂散动态范围(spurious

‑

free dynamic range)(sfdr)。

22.因此,在本发明的实施例中,经校准的倍频器被用于提供占空比基本上等于50%的时钟和/或提供具有基本上相等的连续时钟周期的时钟,同时有利地受益于基于延迟的倍频器电路所提供的较小的尺寸以及功耗节省。

23.图1a示出了实施例倍频器系统10。如图所示,系统10包括倍频器12、占空比敏感电路装置14以及占空比测量和调整电路16。例如,占空比敏感系统电路装置14可以包括模数转换器、占空比敏感的升压电路(诸如,电荷泵)和/或其它电路装置(诸如,对其输入时钟的占空比敏感或对在预加倍时钟中的占空比误差引起的时钟周期变化敏感的pll和定时敏感数字电路)。倍频器电路12(也称为“可调倍频电路”)被配置为使耦合到倍频器电路12的时钟输入的第一时钟信号clk1x的频率加倍并且形成第二时钟信号clk2x。例如,如果第一时钟信号clk1x具有40mhz的时钟频率,则第二时钟信号clk2x将具有80mhz的时钟频率。然而,应当理解,取决于特定应用及其规格,第一时钟信号clk1x和第二时钟信号clk2x可以是任何频率。

24.如图所示,倍频器电路12包括占空比调整输入,使得占空比调整信号dutyadj被用于调整第一时钟信号clk1x的占空比和/或第二时钟信号clk2x的占空比。占空比调整信号dutyadj可以被实现为包括一位或多位的模拟信号或数字信号。在各种实施例中,倍频器电路12使用本领域中已知的倍频电路来实现。例如,倍频器电路12可以使用如下所述的异或门和可调延迟电路来实现。然而,在备选的实施例中,可以使用其它倍频电路。

25.占空比测量和调整电路16可以被用于直接地或间接地测量第一时钟信号clk1x的

占空比和/或第二时钟信号clk2x的占空比,并且响应于这些测量提供占空比来调整信号dutyadj。所测量的占空比或与占空比相关的测量值也可以被称为占空比参数。在一些实施例中,占空比测量和调整电路16仅在校准时间周期期间(诸如,在校准模式期间)操作。在正常操作的周期期间,占空比测量和调整电路16可以是不活动的或断电的。在其它实施例中,占空比测量和调整电路16可以仅在特定零件的制造和/或测试期间操作。在这种情况下,占空比测量和调整电路16的全部或部分可以驻留在测试夹具上,该测试夹具与包括倍频器电路12和占空比敏感系统电路装置14的电路的剩余部分分开。例如,倍频器12可以在包括占空比敏感系统电路装置14的集成电路的晶片或生产测试期间由占空比测量和调整电路16校准。在其它实施例中,占空比测量和调整电路16可以被驻留在与倍频器电路12和占空比敏感系统电路装置14相同的集成电路或相同的系统上。在又一些其它实施例中,占空比测量和调整电路16可以连续地监测第二时钟信号clk2x,并且提供对由倍频器电路12产生的第一时钟信号clk1x和/或第二时钟信号clk2x的占空比的连续调整。

26.例如,可以使用本领域已知的占空比测量电路来实现占空比测量和调整电路16,占空比测量电路包括但不限于高速计数器、混频器和模数转换器。另外,占空比测量和调整电路16可以包括数字电路装置(诸如,状态机和/或处理电路),其有助于占空比的测量以及占空比调整信号dutyadj的形成。

27.图1b示出了根据本发明的备选实施例的倍频器系统50。如图所示,倍频器系统50包括占空比敏感的模数转换器56,模数转换器56的输入adcin(也称为“adc信号输入”)被选择性地耦合到系统电路装置52或测试音调生成器54(也称为“测试音调生成电路”)。在系统50的正常操作期间,系统电路装置52经由选择开关62在占空比敏感的模数转换器56的输入adcin处提供模拟信号。如图所示,占空比敏感的模数转换器56被耦合到第二时钟信号clk2x,第二时钟信号clk2x在时钟输入处向占空比敏感的模数转换器56提供时钟信号,使得第二时钟信号clk2x在操作期间对占空比敏感的模数转换器56计时。系统电路装置52可以包括产生由系统50利用的模拟信号的任何系统电路装置。例如,在rf系统中,系统电路装置52可以包括rf前端和/或下变频器,rf前端和/或下变频器产生与接收的rf信号相关的模拟信号。在其它系统中,系统电路装置52可以生成其它类型的模拟信号,包括但不限于音频信号、传感器信号、图像信号、视频信号等。

28.占空比敏感的模数转换器56在占空比敏感的模数转换器56的输出处将输入adcin处的模拟信号转换为数字信号adcout(也称为“adc信号输出”)。可以使用多种模数转换器架构来实现占空比敏感的模数转换器56,包括但不限于逐次逼近转换器sigma delta转换器、闪存转换器流水线转换器以及本领域已知的其它数据转换器架构。在校准期间,测试音调生成器54向占空比敏感的模数转换器56提供测试音调,测试音调由占空比分析和调整电路58分析。在一些实施例中,占空比敏感的模数转换器56与占空比分析和调整电路58的组合也可以被称为占空比测量和调整电路。例如,可以使用数字分频器和低通滤波器来实现测试音调生成器54。也可以使用本领域已知的其它测试音调生成电路。

29.占空比分析和调整电路58被配置为分析数字信号adcout的杂散行为,并且使用占空比调整信号dutyadj调整倍频器电路12的占空比。在一些实施例中,占空比分析和调整电路58迭代地调整占空比调整信号dutyadj,直到数字信号adcout的杂散响应满足预先确定性能要求和/或预先确定阈值要求为止。在一些实施例中,占空比分析和调整电路58可以驻

留在与系统电路装置52、测试音调生成器54、占空比敏感的模数转换器56和倍频器电路12相同的系统集成电路、电路板和/或壳体上。在其它实施例中,占空比分析和调整电路58可以驻留在系统50的制造测试和/或校准期间使用的单独的测试夹具上。例如,占空比分析和调整电路58可以包括:微处理器、数字信号处理电路装置、专用逻辑或适用于根据以下进一步说明的系统和方法所确定的数字信号adcout的杂散响应的其它电路装置。

30.在一些实施例中,测试控制器60可以被用于配置倍频器系统50以执行倍频器电路12的校准。例如,在校准期间,测试控制器60可以控制开关62以将测试音调生成器54的输出路由到占空比敏感的模数转换器56的输入。在一些实施例中,校准可以发生在校准测试时间期间或校准模式期间。测试控制器60还可以通过占空比分析和调整电路58启动对数字信号adcout的测量,启动对倍频器电路12的占空比的调整,并且在倍频器电路12的占空比校准期间激活测试音调生成器54。在各种实施例中,测试控制器60或测试控制器60的部分可以驻留在与系统电路装置52、测试音调生成器54、占空比敏感的模数转换器56和倍频器电路12相同的系统集成电路、电路板和/或壳体上。在其它实施例中,测试控制器60或测试控制器60的部分可以驻留在系统50的制造测试和/或校准期间使用的单独的测试夹具上。

31.图2a至2d示出了与本发明的实施例有关的波形图。参考图2a,示出了三个波形图。第一波形图示出了第一时钟信号clk1x,第一时钟信号clk1x表示提供给倍频器电路12的输入的时钟信号;第二图示出了从具有非50%占空比的倍频器电路12输出的第二时钟信号clk2x;并且第三图示出了具有50%占空比的第二时钟信号clk2x。如图所示,第二时钟信号clk2x对于时间周期t

h

具有高值,并且对于时间周期t

l

具有低值。对于非50%占空比,时间周期t

h

和t

l

不相等。在示出的示例中,时间周期t

h

被示出为短于时间周期t

l

。然而,在第二时钟信号clk2x具有非50%占空比的其它情况下,时间周期t

h

可以长于时间周期t

l

。当第二时钟信号clk2x的占空比基本上为50%时,时间周期t

h

基本上等于时间周期t

l

。在各种实施例中,调整第二时钟信号clk2x的占空比直到占空比基本上为50%为止。在一些实施例中,当所测量的占空比参数在预先确定范围内和/或占空比被调整为具有可接受的质量度量时,第二时钟信号clk2x的占空比被认为基本上为50%。

32.图2b示出了波形图,波形图示出了具有非50%占空比的第一时钟信号clk1x以及所得的、具有变化的时间周期的第二时钟信号clk2x。如图所示,第一时钟信号对于时间周期t

h

具有高值并且对于时间周期t

l

具有低值,其中时间周期t

h

不等于时间周期t

l

。所得的双倍第二时钟信号clk2x具有交替的持续时间的时间周期。例如,在与第一时钟信号clk1x的时间t

h

相对应的时间周期中,第二时钟信号clk2x具有t

p1

的时钟周期。然而,在与第一时钟信号clk1x的时间t

l

相对应的时间周期中,第二时钟信号clk2x具有t

p2

的时钟周期,其中时间周期t

p1

不等于时间周期t

p2

。这些时间周期t

p1

和t

p2

相对于彼此交替。因此,随着第一时钟信号clk1x的占空比接近50%,第二时钟信号的时钟周期t

p1

与t

p2

之间的变化减小。

33.在各种实施例中,调整第二时钟信号clk2x的占空比直到连续时钟周期t

h

和t

l

的长度具有基本相等的长度为止。在一些实施例中,当所测量的占空比参数在预先确定范围内和/或第一时钟信号clk1x的占空比被调整为具有可接受的质量时,连续时钟周期t

h

和t

l

的长度被认为具有基本相等的长度。

34.图2c示出了当在输入adcin处呈现来自测试音调生成器54的1mhz测试音调以及当由具有非50%占空比的第二时钟信号clk2x计时时的占空比敏感的模数转换器56的输出频

谱的图。使用快速傅里叶变换(fft)生成图2b的图。在点70处的频谱的峰值表示1mhz测试音调,而在点72处的峰值表示由第二时钟信号clk2x的非50%占空比导致的600khz处的频率杂散。

35.图2c中所示的特定示例表示其中占空比敏感的模数转换器56的采样间隔的持续时间由于非50%占空比的不对称性质而交替的情况。例如,在操作期间,短采样间隔和长采样间隔彼此交替。采样间隔中的这种交替有效地导致了在采样频率f

s

的一半频率的音调。这种音调与输入音调混合会引起以下杂散:

36.f

spur

=f

s

/2

–

f

in

37.其中f

spur

是杂散频率并且f

in

是由测试音调生成器54生成的音调的频率。在所示情况下,采样频率是3.2mhz并且输入音调是1mhz,预期的杂散是在600khz处。应当理解,以上等式假设采样间隔的持续时间在每个采样间隔处交替。在本发明的备选的实施例中,其中在第二时钟信号clk2x的每个周期处都不对占空比敏感的模数转换器56计时,取决于特定的adc的时钟方案,杂散的频率可以不同于f

s

/2

‑

f

in

。

38.图2d示出了针对各种频率的相对于占空比的无杂散动态范围的图。曲线74表示1mhz的输入频率,曲线76表示800khz的输入频率,曲线78示出了600khz的输入频率,曲线80表示400khz的输入频率,并且曲线82表示200khz的输入频率。从图2c的曲线图可以看出,当第二时钟信号clk2x的占空比从50%的占空比偏离时,占空比敏感的模数转换器56的无杂散动态范围降低。例如,对于50%的占空比,占空比敏感的模数转换器56的无杂散动态范围超过90db。然而,对于47%或53%的占空比,占空比敏感的模数转换器56的无杂散动态范围仅为约53db。此外,占空比敏感的模数转换器56的无杂散动态范围也随着音调频率的增加而降低。如图所示,对于47%或53%的占空比,具有200khz的输入音调的无杂散动态范围约为66db,而具有1mhz的输入音调的无杂散动态范围约为53db。应当理解,实际产生的无杂散动态范围可以取决于所使用的特定架构、其架构、其时钟速度、输入音调的幅度以及其它因素而变化。尽管图2c和2d的波形图示出了其中第二时钟信号clk2x的占空比变化的系统中的杂散性能的示例,但是当第一时钟信号clk1x的占空比改变时,对于模数转换器,特别是对于第二时钟信号clk2x的交替周期长度敏感的模数转换器而言,可以看到类似的比较性能,第二时钟信号clk2x的交替周期长度由第一时钟信号clk1x中的占空比误差引起。

39.图3a至3d示出了根据本发明的实施例的倍频器电路12的示意图。图3a示出了倍频器电路12的顶层示意图。如图所示,倍频器电路12包括占空比校正电路102、可调延迟电路104和异或门106。在操作期间,占空比校正电路102校正第一时钟信号clk1x的占空比并且产生调整的占空比时钟信号clk1xc。如上所述,通过在第一时钟信号clk1x的频率加倍之前校正其占空比中的误差,可以产生更精确的双倍时钟信号频率。然而,在一些实施例中,在一些实施例中可以省略占空比校正电路102或可调延迟电路。例如,在第一时钟信号clk1x已经具有相对准确的占空比的实施例中,可以省略占空比校正电路102,而在即时的电路装置对非50%周期不敏感的实施例中,可以使用固定延迟来实现可调延迟电路104。

40.通过可调延迟电路104和异或门106执行时钟频率的实际加倍。在操作期间,可调延迟电路104将可调占空比时钟信号clk1xc延迟其时钟周期的四分之一,以形成延迟的第一时钟信号clk1xd。通过对调整的占空比时钟信号clk1xc和延迟的第一时钟信号clk1xd执行异或操作,生成具有第一时钟信号clk1x的频率的两倍的频率的时钟信号。通过调整可调

延迟电路104的延迟,可以调整第二时钟信号clk2x的所得的占空比。在各种实施例中,通过信号dutyadj设置可调延迟电路104的延迟,信号dutyadj被提供给可调延迟电路104的控制输入。

41.图3b示出了根据本发明的实施例的可调延迟电路104的示意图。如图所示,可调延迟电路104包括彼此串联耦合的多个延迟单元110。延迟单元110还可以被称为可选延迟电路。根据占空比调整信号dutyadj,多路复用器111从多个延迟单元110中选择一个延迟单元110的输出。因此,对于更长的编程延迟,可以选择在一系列延迟单元的末端附近耦合的延迟单元110;对于更短的编程延迟,可以选择在一系列延迟单元110的开始附近耦合的延迟单元110。在各种实施例中,可调延迟电路104可以包含任何数目的延迟单元110。延迟单元110的数目以及每个延迟单元110能够产生的时间延迟量可以根据特定实施例及其规格而变化。例如,与具有较低时钟频率的系统相比,具有较高时钟频率的系统可能需要较少的延迟和较少的延迟单元。

42.图3c

‑

3e示出了可以被用于实现图3b所示的延迟单元110的延迟单元的示意图。图3c的延迟器包括由电容器114加载的缓冲器112。由延迟单元实现的延迟时间量是缓冲器112的强度和电容器114的尺寸的函数。例如,当缓冲器112的强度弱并且电容器114的尺寸大时,延迟单元110可以产生更长的延迟。另一方面,当缓冲器112具有强输出并且电容器114的尺寸小时,延迟单元110可以产生较短的延迟。在各种实施例中,可以使用本领域中已知的数字缓冲器电路装置来实现缓冲器112。例如,可以使用彼此串联耦合的两个反相器来实现缓冲器112。图3d的延迟单元包括由电容器114加载并且由第二反相器113缓冲的反相器113。再次,延迟时间量是电容器114的电容和反相器113驱动电容器114的强度的函数。备选地,可以使用一系列反相器(诸如图3e所示的延迟单元)来构造延迟单元。图3e所示的延迟单元的延迟器是用于构造延迟单元的反相器113的数目和强度的函数。通常,较长的延迟与较弱的反相器和/或大量的反相器相关联,而较短的延迟与较弱的反相器和/或较小数目的反相器相关联。

43.然而,应当理解,图3c

‑

3e所示的延迟单元仅仅是可以在本发明的实施例中使用的许多可能的延迟单元架构的几个示例。在备选的实施例中,可以使用其它结构。例如,延迟单元110可以通过使用可以被使用的其它延迟结构(诸如,缓冲器链、rc网络等)来实现。在一些实施例中,可以组合不同的延迟结构的组合以实现延迟单元。

44.图3f示出了也可以被用于实现图3a中的可调延迟电路104的可调延迟电路118。如图所示,可调延迟电路118包括由可变电容器115加载并且由第二反相器113缓冲的反相器113。可调延迟电路118的延迟可以通过基于占空比可调信号dutyadj的值调整可变电容器115的电容来编程。在一些实施例中,可以使用多个开关电容器来实现可变电容器115。因此,可以通过将多个电容器中的更多电容器耦合到反相器113来增加可调延迟电路118的延迟,并且可以通过将多个电容器中的更少电容器耦合到反相器113来减少延迟。在本发明的备选的实施例中,可以使用本领域已知的其它可变电容器电路(诸如,变容二极管)来实现可变电容器115。

45.在一些实施例中,多个可调延迟电路118可以串联耦合。在另外的实施例中,可调延迟电路118可以被用于实现图3b所示的各个延迟单元110,使得可调延迟电路104的延迟可以通过调整可变电容器115的电容并且通过经由多路复用器111选择一个或多个延迟单

元110来编程。

46.图3g示出了根据本发明的备选的实施例的可调延迟电路104的示意图。如图所示,可调延迟电路104包括彼此串联耦合并且由多路复用器130分隔的多个延迟单元110,多路复用器130被配置为根据由占空比调整信号dutyadj提供的选择信号选择性地旁路与其相关联的延迟单元110。因此,对于更长的编程延迟,使用多路复用器130将更多可选的延迟单元110切换到信号路径中;对于短的编程延迟,使用多路复用器130将较少的延迟单元110切换到信号路径中。在各种实施例中,可调延迟电路104可以包含任何数目的级,级包含延迟单元110和多路复用器130。级的数目和每个延迟单元110能够产生的时间延迟的量可以根据特定实施例及其规格而变化。例如,与具有较低时钟频率的系统相比,具有较高时钟频率的系统可能需要较少的延迟和较少的延迟单元。在一些实施例中,图3f所示的可调延迟电路118可以被用于实现延迟单元110。

47.图3h示出了可以被用于实现图3a中所示的占空比校正电路102的占空比校正电路102。如图所示,占空比校正电路包括反相器113、多路复用器130、可调延迟电路104和或门132。在操作期间,多路复用器根据多路复用器选择信号pol来选择节点clk1x处的时钟输入信号,或者选择由反相器130在节点clk1xb处产生的时钟输入信号的反相。该极性信号确定占空比校正电路的输出节点clk1xc的极性以及在节点clk1xb处的时钟输入信号的哪一部分被调整。例如,当在节点clk1x处的时钟输入信号被选择时,在节点clk1x处的时钟输入信号为高期间的时间是可以通过延伸在节点clk1x处的时钟输入信号的时间周期t

h

调节。另一方面,当输入信号clk1xb被选择时,在节点clk1x处的时钟输入信号为低期间的时间是可以通过延伸在节点clk1x处的时钟输入信号的时间周期t

l

调节。

48.在操作期间,多路复用器mout的输出被可调延迟电路104延迟以形成延迟信号dout。使用或门132将延迟信号dout与多路复用器输出mout进行“或”运算,以在输出节点out处形成占空比校正的信号。随着可调延迟电路104的延迟增加,在输出节点out上存在的时钟信号为高期间的时间增加。相反,随着可调延迟电路104的延迟减小,在输出节点out上存在的时钟信号为高期间的时间减小。在各种实施例中,可调延迟电路104可以如以上关于图3b

‑

3g所描述的来实现。

49.在备选的实施例中,占空比校正电路102可以被不同地实现。例如,图3i示出了占空比校正电路,该占空比校正电路还可以被用于实现图3a所示的占空比校正电路102。如图所示,占空比校正电路102包括彼此并联耦合的多个反相器120。即,每个反相器120的输入被连接到输入节点in并且每个反相器120的输出被连接到输出节点outb。如图所示,每个反相器120包括彼此串联耦合的nmos器件m1和m2以及pmos器件p2和p1。nmos器件m2和pmos器件p2均具有连接到输入节点in的栅极和耦合到输出节点outb的负载路径。反相器120的nmos器件m1的栅极被分别地耦合到数字选择信号dcpn[n:0],并且pmos器件p1的栅极被分别地耦合到数字选择信号dcpb[n:0]。因此,在操作期间,选择性地激活nmos晶体管m1和pmos晶体管p1中的一个或多个晶体管,以便调整反相器120的pmos上拉路径和nmos下拉路径的相对强度。例如,在需要延迟第一时钟信号clk1x的上升沿的情况下,可以选择更少的pmos晶体管p1以减慢或延迟由占空比校正电路102产生的上升沿,而更多的nmos器件m1可以被选择以保持下降沿的延迟较小。类似地,在需要延迟第一时钟信号clk1x的下降沿的情况下,可以选择更少的nmos晶体管m1以减慢或延迟由占空比校正电路102产生的下降沿,而

更多的pmos器件p1可以被选择以保持上升沿的延迟较小。反相器122可以被耦合到反相器120的输出以缓冲反相器120的输出。在各种实施例中,晶体管m1、m2、p1和p2的尺寸在每个反相器120中相同或不同。

[0050]

应当理解,图3a

‑

3i所示的倍频电路12的实现示例仅是倍频电路12的许多可能的实施例实现中的几个示例。在备选的实施例中,其它电路和方法可以被用于实现相同或相似的功能。

[0051]

图4a示出了根据图1a的实施例的校准倍频器电路12的方法200。在步骤202中,使用占空比测量和调整电路16测量第二时钟信号clk2x的占空比参数。在各个实施例中,可以使用高速计数器或本领域已知的其它占空比测量技术直接地测量第二时钟信号clk2x的占空比参数。在步骤204中,调整第一时钟信号clk1x的占空比和/或第二时钟信号clk2x的占空比直到确定的占空比为50%或在50%的预先确定公差内为止,或者调整第一时钟信号clk1x的占空比直到相邻时钟周期中的差异在预先确定公差内为止。在一些实施例中,将确定的占空比参数与阈值占空比参数进行比较,并且迭代地执行图4a中所示的方法200,直到所测量的占空比参数满足预先确定要求为止。

[0052]

图4b示出了根据图1b的实施例的校准倍频器电路12的方法250。在步骤252中,通过测试音调生成器54生成测试音调并且将测试音调路由到占空比敏感的模数转换器56的输入。由测试音调生成器54生成的测试音调的频率可以根据特定的系统及其规格而变化。在一个实施例中,由测试音调生成器54生成的音调的频率是1mhz,然而,在其它实施例中可以使用其它频率。

[0053]

在步骤254中,将由倍频器12产生的第二时钟信号clk2x作为时钟信号被提供给对第一时钟信号clk1x或第二时钟信号clk2x中的占空比变化敏感的占空比敏感的模数转换器56。在步骤256中,以一方式操作占空比敏感的模数转换器56,该方式使得由测试音调生成器54产生的测试音调被数字化,并且将数字输出发送到占空比分析和调整电路58。在步骤258中,对数字化音调执行频率变换,将数字化信号从时域变换到频域以形成频域信号。在一些实施例中,该频率变换是fft,然而在本发明的备选的实施例中,可以使用其它频率变换算法,例如但不限于离散傅里叶变换、离散余弦变换(dct)或本领域已知的其它或其它变换类型。在一些实施例中,可以在执行频率变换之前将开窗功能施加到数字化音调。在步骤260中,确定频率变换信号的sfdr。在一些实施例中,通过确定与测试音调的频率相对应的频率窗(frequency bin)与由第二时钟信号clk2x的占空比中的不对称导致的杂散相对应的频率窗之间的幅度差异来完成sfdr的确定。如上所述,在一些实施例中,该杂散频率可以是f

spur

=f

s

/2

‑

f

in

。在其它实施例中,杂散频率可以取决于特定的实现及其规格而不同。备选地,可以通过确定对应于测试音调的频率窗中的信号的功率与剩余频率窗中的功率之和之间的差异来计算sfdr。

[0054]

在步骤262中,调整第一时钟信号clk1x的占空比和/或第二时钟信号clk2x的占空比,直到确定的sfdr被最小化或在预先确定的范围内为止。在一些实施例中,将确定的sfdr与阈值进行比较,并且迭代地执行图4a中所示的方法250,直到sfdr满足预先确定要求为止。

[0055]

应当理解,在上述方法200和250中,可以调整第一时钟信号clk1x的占空比、第二时钟信号clk2x的占空比或第一时钟信号的占空比和第二时钟信号的占空比两者。在一些

实施例中,顺序地执行第一时钟信号clk1x的占空比和第二时钟信号clk2x的占空比的调整。例如,在一个实施例中,执行方法200和/或250以首先校正第一时钟信号clk1x的占空比,然后校正第二时钟信号clk2x的占空比。在其它实施例中,可以执行方法200和/或250以首先校正第二时钟信号clk2x的占空比,然后校正第一时钟信号clk1x的占空比。

[0056]

图5a示出了系统300,系统300包括耦合到测试夹具308的集成电路302。系统300类似于图1a中所示的系统10,其中倍频器电路12通过直接测量双倍时钟信号来校准。如图所示,集成电路302包括倍频器电路12、占空比敏感的模数转换器56、系统电路装置52、测试多路复用器304和控制逻辑接口电路装置313。在各种实施例中,系统电路装置52表示产生用于由占空比敏感的模数转换器56测量的信号的任何类型的系统电路。例如,系统电路装置52可以包括:rf电路装置、传感器电路装置、音频电路装置或可以被集成在集成电路上的任何其它电路装置。在本发明的备选的实施例中,可以通过不同的方式划分被设置在集成电路302上的各种部件。例如,集成电路302的一个或多个部件可以被设置在多个集成电路上或者可以被实现在电路板上。系统300还包括振荡器306,振荡器306生成第一时钟信号clk1x。在各种实施例中,振荡器306可以是晶体振荡器或能够生成时钟信号的其它类型的振荡器。在一些实施例中,系统300可以被配置为使得振荡器306是晶体并且被用于驱动晶体的有源电路装置(未示出)驻留在集成电路302上。

[0057]

控制逻辑和接口电路装置313包括逻辑,该逻辑控制集成电路302上的各种部件中的一些或所有部件的状态,并且包括被配置为经由数字总线dbus与外部部件通信的数字接口电路装置。在各种实施例中,控制逻辑和接口电路装置313的数字接口可以是串行总线接口电路、并行总线接口电路和/或可以遵循任何总线标准(包括但不限于spi、can、i2c、lvds和usb)的电路。因此,数字总线dbus的信号引脚的数目n可以是适合于所实现的总线协议的任何数目。

[0058]

当倍频器电路12被校准时,测试夹具308可以被耦合到集成电路302。例如,测试夹具308可以在晶片测试、封装测试、制造测试期间或在例行维护或校准操作期间被耦合到集成电路302。例如,可以使用晶片测试夹具、封装测试夹具或被配置为被耦合到用于测试目的的集成系统302的任何其它系统来实现测试夹具308。在一些实施例中,测试夹具308的功能可以被驻留在与集成电路302相同的系统中。如图所示,测试夹具308包括时钟测量电路310、处理器312和存储器314。时钟测量电路310被配置为经由测试接口信号线test被耦合到集成电路302。如图所示,测试接口信号线test被耦合到集成电路302上的多路复用器304的输出。在操作期间,控制逻辑和接口电路装置313选择要被输出到测试接口信号线test的各种信号。在这些可选信号中,第二时钟信号clk2x是倍频的时钟信号。应当理解,多路复用器304可以从集成电路302内的任何数目的可选信号中选择。然而,在一些实施例中,可以省略多路复用器304,并且第二时钟信号clk2x可以被直接地路由到测试接口信号线test。

[0059]

在测试校准期间,时钟测量电路310监测第二时钟信号clk2x并且执行占空比参数测量。在一些实施例中,该占空比参数测量被传输到处理器312。基于该占空比参数测量,处理器312通过经由数字总线dbus向控制逻辑接口电路313发出命令来调整倍频器电路12的占空比。在一些实施例中,由时钟测量电路310测量的占空比的监测和倍频电路12的占空比的调整在功能上通过执行存储器314中驻留的程序来完成。在一些实施例中,存储器314可以被用于存储多个由时钟测量电路310测量的占空比,以及多个对应的占空比调整设置。因

此,在操作期间,处理器312可以选择满足预先确定占空比参数要求的占空比调整设置。

[0060]

在一些实施例中,可以使用微控制器或本领域已知的其它处理电路来实现处理器312。在本发明的备选的实施例中,可以使用专用逻辑(诸如状态机)来实现上述占空比监测和占空比调整功能。在一些实施例中,处理器312还包括被用于辅助确定由时钟测量电路310监测的占空比的数字信号处理电路装置。例如,在一些实施例中,时钟测量电路310包括向处理器312提供数字数据流的模数转换器。在这种实施例中,处理器312接收由时钟测量电路310产生的数据流并且使用一种或多种数字信号处理算法来确定第二时钟信号clk2x的占空比参数。

[0061]

例如,实施例数字信号处理算法可以包括,对第二时钟信号clk2x执行频率变换(诸如fft),并且测量第二时钟信号clk2x的杂散行为。在一个实施例中,与第二时钟信号clk2x的占空比相对应的占空比参数是时钟信号clk2x的二次谐波。因此,根据第二时钟信号clk2x的占空比,第二时钟信号clk2x的频率处的频率窗与第二时钟信号clk2x的二次谐波处的频率窗之间的幅度的差异发生改变。第二时钟信号clk2x的占空比越接近50%,这些频率窗之间的幅度差异越大。

[0062]

在一些实施例中,与第一时钟信号的占空比相对应的占空比参数是第二时钟信号clk2x的一半时钟频率处的杂散的幅度。假定第二时钟信号clk2x的时钟周期每隔一个时钟周期改变一次。因此,根据第一时钟信号clk1x的占空比,第二时钟信号clk2x的频率处的频率窗与第二时钟信号clk2x的一半频率处的频率窗之间的振幅的差异发生改变。第一时钟信号clk1x的占空比越接近50%,这些频率窗之间的幅度的差异越大。在备选的实施例中,可以使用本领域中已知的其它数字信号处理算法来确定占空比参数。

[0063]

图5b示出了可以被用于实现时钟测量电路310的一个电路。在一个实施例中,时钟测量电路310包括计数器322,计数器322监测第二时钟信号clk2x为高和/或低的时间。例如,该时间测量可以通过当第二时钟信号clk2x处于高状态和/或低状态时递增计数器322来实现。该计数的结果可以被发送到处理器312,处理器312可以被配置为基于第二时钟信号clk2x处于高状态(高计数)的计数的数目和第二时钟信号clk2x处于低状态(低计数)的计数的数目的比较来确定第二时钟信号clk2x的占空比。当这些计数相等时,测量的占空比被认为是50%。这些计数不相等的程度与相对于理想的50%占空比的偏差有关。在一些实施例中,出于调整倍频器电路12的占空比的目的,高计数与低计数之间的差异可以被用作占空比度量。

[0064]

在备选的实施例中,可以使用不同的度量。例如,在另一个实施例中,当第二时钟信号clk2x处于第一状态(例如,高或低)时,计数器322可以递增,并且当第二时钟信号clk2x处于第二状态(例如,低或高)时,计数器322可以不递增或递减。预先确定时间周期之后的所得计数可以被用作表示第二时钟信号clk2x的占空比的参数。

[0065]

可以通过使用计数器322测量第二时钟信号clk2x的连续时钟周期的长度来确定与第一时钟信号clk1x相关的占空比参数。因此,随着两个连续的时钟周期的长度彼此接近,第一时钟信号clk1x的占空比接近50%。

[0066]

图5c表示可以实现时钟测量电路310的另一种方式。在实施例中,可以使用模数转换器324来实现时钟测量电路310。在这种实施例中,模数转换器324将第二时钟信号clk2x数字化并且将转换的数字值发送到处理器312。然后,处理器312可以执行转换的数字值的

频率变换,确定无杂散动态范围,并且根据所确定的无杂散动态范围调整倍频器电路12的占空比。

[0067]

图5d示出了可以被用于实现时钟测量电路310的进一步的电路。如图所示,可以使用模数转换器324和混频器326来实现时钟测量电路310。例如,混频器326可以被用于将时钟信号下变频为较低频率,使得较低的采样率可以被用于模数转换器324。在一些实施例中,被用于驱动混频器326的本地振荡器信号lo的频率可以被设置为下变频杂散信号,杂散信号受到第二时钟信号clk2x的占空比的显著影响。类似于图5c的实施例,使用处理器312分析模数转换器324的数字化输出以执行频率变换(诸如,fft),并且比较下变频的时钟信号和下变频的杂散响应的相对幅度。这些相对幅度的差异可以被用作调整倍频器电路12的占空比的基础。在各种实施例中,可以使用适合于特定应用和特定监测时钟频率的任何类型的模数转换器架构来实现模数转换器324。在一些实施例中,可以使用sigma delta模数转换器、流水线模数转换器、闪存模数转换器或其它类型的模数转换器来实现模数转换器324。可以使用本领域已知的混频器电路来实现混频器326。应当理解,图5b

‑

5d的示例仅仅是可以被用于测量第二时钟信号clk2x的占空比的许多类型的电路的三个示例。在本发明的备选的实施例中,可以使用本领域中已知的其它电路。

[0068]

图5e示出了校准图5a所示的系统300的倍频器电路12的占空比的方法350。在步骤352中,倍频器电路12被初始化。例如,该初始化可以包括将倍频器电路12内的各种延迟设置(也称为占空比设置)配置为预先确定值。在一些实施例中,初始化倍频器电路12可以包括将这些预先确定值写入倍频器电路12所驻留的系统或集成电路302上驻留的本地寄存器或存储器。在一个示例中,处理器312可以经由数字总线dbus将配置命令发送到控制逻辑和接口电路装置313。例如,该配置命令可以是控制字内的单个命令,或者是寄存器写命令,寄存器写命令被寻址到特定寄存器和/或专用于倍频器电路12的延迟设置的寄存器。

[0069]

在步骤354中,第二时钟信号clk2x被配置为被路由到测试夹具308上的时钟测量电路310。在实施例中,通过配置多路复用器304以将第二时钟信号clk2x路由到外部测试引脚test,而将第二时钟信号clk2x路由到时钟测量电路310。接下来,在步骤356中初始化时钟测量电路310。在一些实施例中,诸如图5c和图5d的实施例,初始化驻留在时钟测量电路310内的模数转换器324。例如,该初始化可以包括激活模数转换器324和/或将耦合到信号test的输入路由到模数转换器324的输入。

[0070]

在步骤358中,可以根据第一倍频器配置来配置倍频器电路12。例如,该第一倍频器配置可以包括用于倍频器电路12的延迟设置的第一预先确定集合。在一些实施例中,如上所述结合步骤352来执行步骤358。在步骤360中,通过时钟测量电路310捕获第二时钟信号clk2x。在一些实施例中,通过使用如图5c和图5d中所示的模数转换器324数字化第二时钟信号clk2x来执行第二时钟信号clk2x的捕获。在利用频率变换(诸如,fft)的实施例中,可以通过数字化预先确定数目的采样来实现第二时钟信号clk2x的捕获。在一些实施例中,该预先确定数目的采样可以是二的幂。例如,可以通过模数转换器324数字化512、1024、2048或4096个样本。在本发明的备选的实施例中,可以根据特定系统及其规范来捕获两个或甚至不是二的幂的多个采样的其它幂。在一些实施例中,窗口函数可以被应用于数字化采样。这种窗口函数可以包括但不限于矩形窗口、三角形窗口、余弦和窗口、韩恩(hann)窗口、汉明(hamming)窗口、布莱克曼(blackman)窗口以及本领域中已知的其它窗口。在一些

实施例中,这种窗口的应用可以减少光谱泄漏并且提高光谱测量的准确性。

[0071]

在步骤364中,计算并且存储质量度量。可以如根据图4a的实施例所描述的那样计算这种质量度量。例如,可以根据数字化输出直接地测量第二时钟信号clk2x的占空比和/或第二时钟信号clk2x的时钟周期变化。备选地,可以通过确定与第二时钟信号clk2x的频率相对应的音调和与由第二时钟信号clk2x内的占空比误差导致的失真相对应的杂散之间的差异来确定频率变换的数字化输出的无杂散动态范围。在一些实施例中,通过确定与第二时钟信号clk2x相对应的频率窗中的音调的功率与一个或多个其它频率窗的功率的和之间的差异来确定sfdr。备选地,可以使用其它性能度量。在一些实施例中,计算的质量度量被存储在存储器或寄存器中。在一些实施例中,计算的质量度量被存储在测试夹具308内的存储器314中。备选地,计算的质量度量可以被存储在设置在集成电路302上的存储器或寄存器中。

[0072]

在步骤366中,确定是否已经评估了倍频器电路12的所有配置。在一些实施例中,倍频器电路12的所有可能的配置被评估。在备选的实施例中,倍频器电路12的所有配置的子集被评估。在其它实施例中,执行搜索算法(诸如,二进制搜索或线性搜索),直到计算的质量度量满足预先确定的标准(诸如,预先确定的占空比或预先确定的无杂散动态范围)为止。如果不满足步骤366的条件,则提供倍频器12的进一步的配置(步骤362)。一旦提供了所有配置,该方法继续到步骤368。

[0073]

在步骤368中,执行用于最佳质量测量的搜索。在一些实施例中,将每个计算的质量度量相互比较,并且选择对应于最佳质量度量的倍频器配置以在正常操作期间配置倍频器电路12。在其它实施例中,执行搜索直到计算的质量度量在预先确定范围内为止。在一些实施例中,步骤368与捕获步骤360中的时钟输出和步骤364中的质量度量的计算和存储一起迭代执行。然后在步骤370中将具有最佳质量度量的倍频器配置施加到倍频器电路12。在一些实施例中,该倍频器配置被写入耦合到倍频器电路12的寄存器或存储器中。

[0074]

图6a示出了包括耦合到测试夹具408的集成电路402的系统400。系统400类似于图1b中所示的系统10,其中通过监测占空比敏感的模数转换器56并且确定取决于第一时钟信号clk1x的占空比和/或第二时钟信号clk2x的占空比的质量度量(诸如,无杂散动态范围)来校准倍频器电路12。如图所示,集成电路402包括倍频器电路12、占空比敏感的模数转换器56、系统电路装置52、测试多路复用器404、控制逻辑和接口电路装置413、测试音调生成器54和先进先出(fifo)存储器418。在校准期间,控制逻辑和接口电路装置413激活测试音调生成器54,测试音调生成器54的输出经由测试多路复用器404被路由到占空比敏感的模数转换器56的输入。如上面关于图4b所描述的,模数转换器56的输出adcout由fifo418缓冲,并且fifo 418的输出经由数字总线dbus被传输到控制器312,控制器312例如通过执行频率变换(诸如,fft)来确定质量度量,并且基于频率变换的输出来确定sfdr。

[0075]

基于确定的质量度量,处理器312通过经由数字总线dbus向控制逻辑接口电路413发出命令来调整倍频器电路12的占空比。在一些实施例中,质量度量的计算和倍频器电路12的占空比的调整在功能上通过执行驻留在存储器314中的程序来完成。在一些实施例中,存储器314可以被用于存储多个由处理器312确定的质量度量以及多个对应的占空比调整设置。因此,在操作期间,处理器312可以选择满足预先确定的质量度量的占空比调整设置。

[0076]

在本发明的备选的实施例中,可以以不同的方式划分设置在集成电路402上的各

种部件。例如,集成电路402的一个或多个部件可以被设置在多个集成电路上或者可以被实现在电路板上。系统400还包括振荡器306,振荡器306生成第一时钟信号clk1x。在各种实施例中,振荡器306可以是晶体振荡器或能够生成时钟信号的其它类型的振荡器。在一些实施例中,系统400可以被配置使得振荡器306是晶体并且被用于驱动晶体的有源电路装置(未示出)驻留在集成电路402上。

[0077]

控制逻辑和接口电路装置413包括逻辑,该逻辑控制集成电路402上的各种部件中的一些或所有部件的状态,并且包括被配置为经由数字总线dbus与外部部件通信的数字接口电路装置。在各种实施例中,控制逻辑和接口电路装置413的数字接口可以是串行总线接口电路、并行总线接口电路和/或可以遵循任何总线标准(包括但不限于spi、can、i2c、lvds和usb)的电路。因此,数字总线dbus的信号引脚的数目n可以是适合于实现的总线协议的任何数目。

[0078]

在对倍频器电路12进行校准的时间期间,测试夹具408可以被耦合到集成电路402。例如,在晶片测试、封装测试、制造测试期间或在例行维护或校准操作期间,测试夹具408可以被耦合到集成电路402。例如,可以使用晶片测试夹具、封装测试夹具或被配置为耦合到用于测试目的的集成电路402的任何其它系统来实现夹具408。在一些实施例中,测试夹具408的功能可以驻留在与集成电路402相同的系统中。

[0079]

图6b示出了根据实施例的可以被用于实现测试音调生成器54的电路。如图所示,测试音调生成器54包括分频器422,可以使用本领域中已知的分频器电路来实现分频器422。在操作期间,分频器422将第二时钟信号clk2x分频至较低频率。在一个实施例中,如以上关于图4b的实施例所描述的,由分频器422产生的频率大约为1mhz。备选地,取决于特定系统及其规格,可以生成其它频率。在一些实施例中,分频器422的分频比可以根据被提供为频率器422的输入的分频率div来编程。在一些实施例中,可以通过控制逻辑接口413经由信号引脚en使能分频器422的操作。在一些实施例中,分频率422被配置为仅使用第二时钟信号clk2x的上升沿或仅使用第二时钟信号clk2x的下降沿来将第二时钟信号clk2x除以至少两倍。在这种实施例中,即使当第二时钟信号clk2x的占空比不是50%时,也可以确保产生的测试音调的50%的占空比。

[0080]

在一些实施例中,使用具有一个或多个寄存器的波纹计数器或同步计数器来实现分频器422。在其它实施例中,可以使用本领域已知的各种预分频器电路和系统来实现分频器422。

[0081]

在一些实施例中,对分频器422的输出进行低通滤波以便衰减或去除谐波,如图6c所示,其示出了耦合到分频器422的输出的低通滤波器424。可以使用本领域已知的模拟低通滤波器电路来实现低通滤波器424。例如,在一些实施例中,可以使用简单的单极rc滤波器来实现低通滤波器424,单极rc滤波器使用串联电阻器和并联电容器。也可以使用高阶无源滤波器,诸如无源lc和/或rlc滤波器。在其它实施例中,可以使用更复杂的滤波器拓扑。例如,可以使用有源滤波器,该有源滤波器具有一个或多个实现一个或多个极。例如,可以使用基于运算放大器的滤波器结构、基于跨导放大器的滤波器结构(诸如,gmc滤波器)或本领域已知的其它有源滤波器结构来实现这种有源滤波器。在一些实施例中,低通滤波器424被耦合在测试多路复用器404的输出与占空比敏感的模数转换器56的输入之间。在这种实施例中,低通滤波器424还用作用于占空比敏感的模数转换器56的抗锯齿滤波器。低通滤波

器424的带宽可以被设置为适合于所实现的特定系统的频率。例如,在一些实施例中,低通滤波器424的截止频率可以小于占空比敏感的模数转换器56的采样频率的一半。

[0082]

图6d示出了校准图6a中所示的系统400的倍频器电路12的占空比的方法450。在步骤452中,初始化倍频器电路12。例如,该初始化可能需要将倍频器电路12内的各种延迟设置(也称为占空比设置)配置为预先确定值。在一些实施例中,初始化倍频器电路12可以包括将这些预先确定值写入倍频器电路12驻留的系统或集成电路402上驻留的本地寄存器或存储器。在一个示例中,处理器312可以经由数字总线dbus将配置命令发送到控制逻辑和接口电路装置413。例如,该配置命令可以是控制字内的单个命令,或者是寄存器写入命令,该寄存器写入命令被寻址到特定寄存器和/或专用于倍频器电路12的延迟设置的寄存器。

[0083]

在步骤454中,测试音调生成器54被初始化并且被激活,使得生成测试音调。接下来,在步骤456中,占空比敏感的模数转换器被初始化,使得基于第二时钟信号clk2x将测试音调生成器54的输出转换为数字信号。可以通过配置测试多路复用器404以将测试音调生成器54的输出路由到占空比敏感的模数转换器56的输入来执行这种初始化。在步骤458中,可以根据第一倍频器配置来配置倍频器电路12。例如,该第一倍频器配置可以包括用于倍频器电路12的延迟设置的第一预先确定集合。在一些实施例中,结合如上所述的步骤452执行步骤458。

[0084]

在步骤460中,占空比敏感的模数转换器56数字化测试音调,测试音调的输出被发送到fifo 418。接下来,在步骤462中,通过在测试夹具408中的处理器312读取fifo 418中存储的数字化测试音调数据。在一些实施例中,数字化测试音调数据的一个或多个采样可以被存储在测试夹具408上的存储器314中。在一些实施例中,预先确定数目的采样可以被传输到用于每个质量度量测量处理器312。在处理器312对数字化数据执行fft的实施例中,该预先确定数目的采样可以是二的幂。例如,可以通过占空比敏感的模数转换器56将512、1024、2048或4096个采样数字化。在本发明的备选的实施例中,可以根据特定系统及其规范来捕获两个或甚至不是二的幂的多个采样的其它幂。在一些实施例中,窗口函数可以被应用于数字化采样。这种窗口函数可以包括但不限于矩形窗口、三角形窗口、余弦和窗口、韩恩窗口、汉明窗口、布莱克曼窗口以及本领域中已知的其它窗口。在一些实施例中,这种窗口的应用可以减少光谱泄漏并且提高光谱测量的准确性。

[0085]

在步骤464中,计算并且存储质量度量。可以如根据图4b的实施例描述的那样计算这种质量度量。例如,可以将fft施加到数字化音调,并且可以通过确定与数字化音调的频率相对应的频率窗中的音调的功率与一个或多个其它频率窗的功率的和之间的差异来确定sfdr。备选地,可以使用其它性能度量。在一些实施例中,计算的质量度量被存储在测试夹具308内的存储器314中。备选地,计算的质量度量可以被存储在设置在集成电路302上的存储器或寄存器中。

[0086]

在步骤466中,确定是否已经评估了倍频器电路12的所有配置。在一些实施例中,倍频器电路12的所有可能的配置被评估。在备选的实施例中,倍频器电路12的所有配置的子集被评估。在其它实施例中,执行搜索算法(诸如,二进制搜索或线性搜索)直到计算的质量测量满足预先确定的标准(诸如,预先确定的占空比或预先确定的无杂散动态范围)为止。如果不满足步骤466的条件,则提供倍频器电路12的进一步的配置(步骤462)。一旦提供了所有配置,则该方法继续到步骤468。

[0087]

在步骤468中,执行用于最佳质量度量的搜索。在一些实施例中,将每个计算的质量度量相互比较,并且选择对应于最佳质量度量的倍频器配置以在正常操作期间配置倍频器电路12。在其它实施例中,执行搜索直到计算的质量度量在预先确定的范围内为止。在一些实施例中,步骤468与在步骤460中数字化测试音调以及在步骤464中的质量度量的计算和存储一起迭代执行。然后将具有最佳质量度量的倍频器配置施加到倍频器电路12。在一些实施例中,在步骤470中,该倍频器配置被写入耦合到倍频器电路12的寄存器或存储器中。

[0088]

图7a示出了根据本发明的实施例的rf系统500。rf系统500包括相对于图5a中的集成电路302示出和描述的倍频器占空比调整电路装置外加附加的rf电路装置。如图所示,rf系统500包括耦合到天线516和振荡器306的rf集成电路502。rf集成电路502可以包括被配置为被耦合到未在图7a中示出的rf系统500的其它部分的一个或多个附加的接口引脚。在各种实施例中,rf集成电路502可以被用在各种rf应用中,包括但不限于蜂窝通信系统,诸如蜂窝电话雷达系统,诸如汽车雷达和其它rf系统。rf集成电路502包括倍频器电路12、测试多路复用器304、占空比敏感的模数转换器56以及控制逻辑和接口电路装置313。这些块被配置为根据如上所述的图5a

‑

5e的实施例以及图1a的实施例的操作原理进行操作。如以上关于图5a的实施例所述,测试多路复用器304和数字总线dbus的输出可以被耦合到外部测试夹具。在一些实施例中,测试夹具308的功能可以被合并在rf集成电路502内。

[0089]

除了上述框之外,rf集成电路502包括rf部件,诸如rf前端508、下变频器510、vco 512和锁相环电路装置514。rf前端508具有被配置为耦合到天线516的输入端口,并且rf前端508包括rf电路装置,该rf电路装置被配置为放大从天线516接收的rf信号。下变频器510被配置为将放大的rf信号下变频到较低的频率,诸如中频(if)或基带频率。在一些实施例中,下变频器510将放大的rf信号下变频到零中频(零if)。下变频器510的输出被耦合到可选的抗锯齿滤波器506的输入,该抗锯齿滤波器被配置为衰减高于占空比敏感的模数转换器56的采样频率的一半的频率分量。在一些实施例中,rf集成电路502还包括被配置为将发送的rf信号提供给天线516和/或另一个天线(未示出)的发送路径(未示出)。可以使用本领域已知的rf电路装置来实现rf前端508和下变频器510。

[0090]

rf集成电路502还包括频率生成块,诸如压控振荡器(vco)512和锁相环电路装置514。根据本发明的实施例,锁相环电路装置514接收第二时钟信号clk2x并且使用本领域已知的锁相环电路和系统将vco 512调谐到第二时钟信号clk2x的频率的倍数的频率。例如,锁相环电路装置514可以包括相位检测器、电荷泵以及一个或多个分频器和/或预分频器。可以使用本领域中已知的vco电路来实现vco 512。在一个示例中,使用单端或差分柯比兹(differential colpitts)或负电阻振荡器或其它振荡器类型来实现vco 512。在一些实施例中,可以在rf集成电路502的外部实现vco 512和锁相环电路装置514的全部或部分。

[0091]

rf集成电路502还包括可选的处理器504,可选的处理器504被配置为对占空比敏感的模数转换器56的输出adcout执行基带信号处理。在备选的实施例中,代替或除了处理器504之外,可以由外部处理器执行基带信号处理。在一些实施例中,代替或除了基带滤波器506之外,可选的处理器504还可以执行基带滤波。处理器504还可以将数据提供给外部数据总线(未示出)和/或控制逻辑接口电路313。

[0092]

图7b示出了根据本发明的进一步的实施例的rf系统550。rf系统500包括相对于上

述实施例示出和描述的倍频器占空比调整电路装置外加以上相对于图7a所述的附加的rf电路装置。在校准期间,测试音调生成器54的输出经由测试多路复用器404被路由到占空比敏感的模数转换器56的输入。在一些实施例中,基带滤波器506被耦合在测试多路复用器404与占空比敏感的模数转换器56之间,以在其被模数转换器56转换之前执行下变频信号的基带滤波和/或基带信号的抗锯齿滤波。

[0093]

如图所示,rf集成电路552包括倍频器电路12、测试多路复用器404、占空比敏感的模数转换器56以及控制逻辑和接口电路装置413、测试音调生成器54和fifo 418。这些块被配置为根据如上所述的图6a

‑

6d的实施例以及图1b的实施例的操作原理进行操作。fifo 418和数字总线dbus的输出可以被耦合到如上关于图6a的实施例所描述的外部测试夹具408。在一些实施例中,测试夹具408的功能可以被合并在rf集成电路552内。rf前端508、下变频器510、vco 512、锁相环电路装置514和抗锯齿滤波器506如以上关于图7a的实施例所描述地进行操作。

[0094]

应当理解,图7a和图7b的实施例仅是本发明的实施例的许多可能的系统实现中的两个系统实现。

[0095]

现在参考图8,根据本发明的实施例提供了处理系统800的框图。处理系统800描绘了通用平台以及通用部件和功能,该通用部件和功能可以被用于实现实施例雷达系统的部分和/或与实施例雷达系统接口的外部计算机或处理设备。例如,处理系统800可以被用于实现图5a中所示的处理器312和/或控制逻辑和接口电路装置313或图6a中所示的控制逻辑接口电路413和图7a和7b所示的处理器504。在一些实施例中,处理系统800可以被用于确定和评估实施例占空比度量、控制实施例rf系统的操作以及控制倍频器12的校准。

[0096]

例如,处理系统800可以包括中央处理单元(cpu)802和连接到总线808的存储器804,并且可以被配置为执行上述处理。在一些实施例中,存储器804可以被用于实现在图5a和6a中所示的存储器314。备选地,存储器314可以与存储器804分离。如果期望或需要,处理系统800还可以包括:显示适配器810,以提供到本地显示器812的连接性;以及输入输出(i/o)适配器814,以提供用于一个或多个输入/输出设备816(诸如,鼠标、键盘、闪存驱动器等)的输入/输出接口。

[0097]

处理系统800还可以包括网络接口818,可以使用网络适配器来实现网络接口818,网络适配器被配置为耦合到有线链路(诸如,网络电缆、usb接口等)和/或用于与网络820通信的无线/蜂窝链路。网络接口818还可以包括用于无线通信的合适的接收器和发送器。应当注意,处理器系统800可以包括其它部件。例如,如果在外部实现,则处理系统800可以包括硬件部件电源、电缆、主板、可移动存储介质、壳体等。尽管未示出,这些其它部件被认为是处理系统800的一部分。在一些实施例中,可以在单个单片半导体集成电路上和/或在与其它公开的系统部件相同的单片半导体集成电路上实现处理系统800。

[0098]

在此总结了本发明的示例实施例。从本文的整个说明书和权利要求中还可以理解其它实施例。

[0099]

在此总结了本发明的实施例。从本文的整个说明书和权利要求中还可以理解其它实施例。

[0100]

示例1。一种方法,包括:通过可调倍频电路接收具有第一时钟频率的第一时钟信号;使用可调倍频电路生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟

频率的两倍;测量第二时钟信号的占空比参数,其中占空比参数取决于第一时钟信号的占空比或第二时钟信号的占空比;并且使用可调倍频器电路基于测量调整第一时钟信号的占空比或第二时钟信号的占空比。

[0101]

示例2。根据示例1的方法,其中:调整占空比包括调整第一时钟信号的占空比;并且方法还重复进行测量和调整的步骤,直到第二时钟信号的连续的时钟周期具有基本相等的长度为止。

[0102]

示例3。根据示例1或2的方法,其中:调整占空比包括调整第二时钟信号的占空比;并且方法还包括重复进行测量和调整的步骤,直到第二时钟信号的占空比基本为50%为止。

[0103]

示例4。根据示例1至3的方法,其中调整第一时钟信号的占空比或第二时钟信号的占空比包括选择可调倍频器电路的多个占空比设置中的一个占空比设置。

[0104]

示例5。根据示例1至4的方法,其中调整第一时钟信号的占空比包括选择可调倍频器电路的占空比校正电路的多个占空比设置中的一个占空比设置,占空比校正电路被耦合到可调倍频器电路的倍频器的输入。

[0105]

示例6。根据示例1至5的方法,其中可调倍频器电路包括异或门和被耦合到异或门的输入的可调延迟电路;以及调整第二时钟信号的占空比包括调整可调延迟电路的延迟。

[0106]

示例7。根据示例1至6的方法,还包括在生成第二时钟信号之前校正第一时钟信号的占空比。

[0107]

示例8。根据示例1至7的方法,其中测量第二时钟信号的占空比参数包括:利用第二时钟信号对模数转换器(adc)计时;接收adc的信号输入处的模拟测试音调;通过adc将模拟测试音调数字化以形成第一时域数字信号;将第一时域数字信号从时域变换到频域以形成第一频域信号;并且测量与模拟测试音调的频率相对应的第一频域信号的第一频率窗与第一频域信号的至少一个第二频率窗之间的差异,以形成测量的占空比参数;以及基于测量调整第二时钟信号的占空比包括:基于测量的占空比参数生成占空比调整信号;并且将占空比调整信号提供给可调倍频电路。

[0108]

示例9。根据示例8的方法,其中将第一时域数字信号从时域变换到频域包括使用fft。

[0109]

示例10。根据示例8或9的方法,其中至少一个第二频率窗对应于fs/2

‑

f1,其中fs是adc的采样率并且f1是模拟测试音调的频率。

[0110]

示例11。根据示例1至10中的一个示例的方法,还包括:接收rf信号;下变频接收的rf信号以形成下变频信号;并且数字化下变频信号。

[0111]

示例12。根据示例1至11中的一个示例的方法,其中测量第二时钟信号的占空比参数包括使用模数转换器数字化第二时钟信号以形成数字化的第二时钟信号,并且基于数字化的第二时钟信号估计占空比参数。

[0112]

示例13。根据权利要求12的方法,其中基于占空比参数估计包括:将数字化第二时钟信号从时域变换到频域以形成频域第二时钟信号;以及测量对应于第二时钟信号的频率的频域第二时钟信号的第一频率窗与频域第二时钟信号的至少一个第二频率窗之间的差异以形成测量的占空比参数。

[0113]

示例14。一种系统,包括:包括时钟输入的可调倍频电路,时钟输出和占空比调整

输入,可调倍频电路被配置为:在时钟输入处接收具有第一时钟频率的第一时钟信号;在时钟输出处生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟频率的两倍;并且基于在占空比调整输入处接收的占空比调整信号调整第一时钟信号的占空比或第二时钟信号的占空比;以及被耦合到时钟输出和可调倍频电路的占空比调整输入的占空比测量和调整电路,占空比测量和调整电路被配置为测量第二时钟信号的占空比参数并且基于测量的占空比参数生成占空比调整信号。

[0114]

示例15。根据示例14的系统,其中占空比测量和调整电路被配置为迭代地测量第二时钟信号的占空比参数,并且修改占空比调整信号直到第二时钟信号的占空比基本为50%为止或第二时钟信号的连续的时钟周期具有基本上相等的长度为止。

[0115]

示例16。根据示例14或15中的一个示例的系统,其中占空比调整信号是数字信号。

[0116]

示例17。根据示例14至16中的一个示例的系统,其中可调倍频电路包括:具有耦合到时钟输入的信号输入的延迟电路;以及异或门,具有耦合到时钟输入的第一输入、耦合到延迟电路的输出的第二输入、以及耦合到时钟输出的输出。

[0117]

示例18。根据示例17的系统,其中延迟电路是具有耦合到占空比调整输入的控制输入的可调延迟电路。

[0118]

示例19。根据示例18的系统,其中可调延迟电路包括多个可选地延迟电路。

[0119]

示例20。根据示例17至19中的一个示例的系统,还包括占空比校正电路,占空比校正电路具有耦合到时钟输入的输入以及耦合到异或门的第一输入和延迟电路的信号输入的输出。

[0120]

示例21。根据示例14至20中的一个示例的系统,其中占空比测量和校正电路包括:模数转换器(adc),具有耦合到可调倍频电路的时钟输出的时钟输入,adc信号输入,被配置为接收模拟测试音调,以及adc信号输出,被配置为提供第一时域数字信号的;以及占空比分析和调整电路,耦合到adc信号输出,占空比分析和调整电路被配置为:将第一时域数字信号从时域变换到频域以形成第一频域信号,测量与模拟测试音调的频率相对应的第一频域信号的第一频率窗与第一频域信号的至少一个第二频率窗之间的差异,以形成测量的占空比参数,并且基于测量的占空比参数生成占空比调整信号。

[0121]

示例22。根据示例21的系统,其中可调倍频电路和adc被设置在第一单片集成电路上并且占空比分析和调整电路被设置在耦合到第一单片集成电路的测试夹具上。

[0122]

示例23。根据示例21或22的系统,还包括射频(rf)前端,射频(rf)前端具有选择性地耦合到adc信号输入的输出。

[0123]

示例24。根据示例14至23中的一个示例的系统,其中占空比测量和调整电路包括:模数转换器(adc),具有耦合到可调倍频电路的时钟输出的adc信号输入以及被配置为提供数字化的第二时钟信号的adc信号输出;以及处理器,耦合到adc的adc信号输出,处理器被配置为:将数字化的第二时钟信号从时域变换到频域以形成频域第二时钟信号,测量与第二时钟信号的频率相对应的频域第二时钟信号的第一频率窗与频域第二时钟信号的至少一个第二频率窗之间的差异以形成测量的占空比参数,并且基于测量的占空比参数生成占空比调整信号。

[0124]

示例25。根据示例24的系统,其中可调倍频电路被设置在第一单片集成电路上,并且占空比测量和调整电路被设置在耦合到第一单片集成电路的测试夹具上。

[0125]

示例26。一种rf系统,包括:rf前端,具有被配置为被耦合到天线的输入端口;测试音调生成电路;多路复用器,具有耦合到rf前端的输出的第一输入,以及耦合到测试音调生成电路的输出的第二输入;可调倍频电路,包括时钟输入、时钟输出和占空比调整输入,可调倍频电路被配置为:在时钟输入处接收具有第一时钟频率的第一时钟信号;在时钟输出处生成具有第二时钟频率的第二时钟信号,第二时钟频率是第一时钟频率的两倍;并且基于在占空比调整输入处接收的占空比调整信号调整第一时钟信号的占空比或第二时钟信号的占空比;以及具有耦合到可调倍频电路的时钟输出的时钟输入的模数转换器(adc),耦合到多路复用器的输出的adc信号输入,以及被配置为提供第一时域数字信号的adc信号输出。

[0126]

示例27。根据示例26的rf系统,还包括:耦合到测试音调生成电路的测试夹具、多路复用器、可调倍频电路、以及adc,测试夹具被配置为在校准模式期间:激活测试音调生成电路,配置多路复用器以选择测试音调生成电路的输出,基于从adc信号输出接收的数字数据确定第二时钟信号的占空比参数,以及基于确定的占空比生成占空比调整信号。

[0127]

尽管已经参考说明性实施例描述了本发明,但是该描述并非旨在以限制性的意义来解释。参考说明书,示例性实施例以及本发明的其它实施例的各种修改和组合对于本领域技术人员将是显而易见的。因此,意图是所附权利要求涵盖任何这样的修改或实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1