一种PD快充PWM芯片的电磁兼容频率源的制作方法

一种pd快充pwm芯片的电磁兼容频率源

技术领域

1.本实用新型涉及功率集成电路领域,具体涉及一种pd快充pwm芯片的电磁兼容频率源。

背景技术:

2.作为智能终端的pd快速充电器的技术基石,反激式转换器近些年已有长足的发展。反激式转换器能够在输入级和输出级之间提供绝缘隔离,为普通用户提供安全可靠的低压直流电源,而脉冲宽度调制(pwm)芯片是其重要的关键部件。

3.pwm波是一种周期性且每周期高电平持续时间可变的脉冲波,在反激式转换器中,pwm波控制功率mos管对输入电源进行通断,在互感线圈、续流二极管和电容的作用下为达到降压且直流输出的作用。然而这种机制却有着不可忽视的缺陷,周期性开通和关断的运行过程会使得外部供电母线发生周期性的阻抗突变,产生emi电磁干扰效应。

4.目前,国内外不少研发团队以及科研组织对反激式转换器充电设备的电磁兼容进行了深入的研究,但大部分研究均采用滤波的方式抑制电磁干扰效应,例如在pd充电器的母线上加装磁环或共轭线圈,虽是一种有效方案,但却使得充电器体积庞大、重量不轻,携带不便。

技术实现要素:

5.针对现有技术中的上述不足,本实用新型提供的一种pd快充pwm芯片的电磁兼容频率源解决了pd快速设备电磁兼容能力不足的问题。

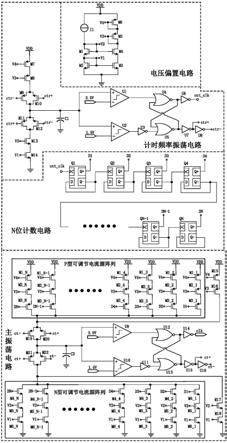

6.为了达到上述发明目的,本实用新型采用的技术方案为:一种pd快充pwm芯片的电磁兼容频率源,包括:电压偏置电路、计时频率振荡电路、n位计数电路和主振荡电路;

7.所述电压偏置电路分别与计时频率振荡电路和主振荡电路连接,用于产生mos管栅极电压偏置;所述计时频率振荡电路的时钟输出端与n位计数电路的时钟输入端连接,用于产生n位计数电路的基准频率;所述n位计数电路与主振荡电路连接,用于产生增计数模式的n位自增数据,控制主振荡电路,持续性地微调其频率输出;所述电压偏置电路的供电端vdd分别与计时频率振荡电路的供电端vdd和主振荡电路的供电端vdd连接,并作为电磁兼容频率源的直流供电端;所述计时频率振荡电路的3.5v输入端与主振荡电路的3.5v输入端连接,并作为电磁兼容频率源的第一输入端;所述计时频率振荡电路的1.5v输入端与主振荡电路的1.5v输入端连接,并作为电磁兼容频率源的第二输入端;所述主振荡电路的clk端作为电磁兼容频率源的输出端;n为闭区间[1,14]内的正整数。

[0008]

进一步地,所述电压偏置电路包括:电流源i1、nmos管m1、nmos管m2、nmos管m3、nmos管m4、pmos管m5和pmos管m6;

[0009]

所述电流源i1的一端与pmos管m6的源极连接,并作为电压偏置电路的供电端vdd;所述电流源i1的另一端分别与nmos管m1的漏极、nmos管m1的栅极和nmos管m4的栅极连接,并作为电压偏置电路的v2端;所述nmos管m2的漏极分别与nmos管m1的源极、nmos管m2的栅

极和nmos管m3的栅极连接,并作为电压偏置电路的v1端;所述pmos管m5的源极分别与pmos管m6的漏极和pmos管m6的栅极连接,并作为电压偏置电路的v4端;所述pmos管m5的漏极分别与pmos管m5的栅极和nmos管m4的漏极连接,并作为电压偏置电路的v3端;所述nmos管m3的漏极与nmos管m4的源极连接,其源极与nmos管m2的源极连接,并接地。

[0010]

进一步地,所述计时频率振荡电路包括:pmos管m7、pmos管m8、pmos管m9、nmos管m10、pmos管m11、nmos管m12、nmos管m13、nmos管m14、电容c1、比较器u1、比较器u2、反相器u3、或非门u4、或非门u5、反相器u6、反相器u7和反相器u8;

[0011]

所述pmos管m7的源极作为计时频率振荡电路的供电端vdd,其漏极与pmos管m8的源极连接,其栅极作为计时频率振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m8的漏极分别与pmos管m9的源极和nmos管m10的源极连接,其栅极作为计时频率振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m9的漏极分别与nmos管m10的漏极、pmos管m11的源极、nmos管m12源极、电容c1的上极板、比较器u1的同相端和比较器u2的同相端连接,其栅极分别与nmos管m12的栅极和反相器u8的输出端连接;所述pmos管m11的漏极分别与nmos管m12的漏极和nmos管m13的漏极连接,其栅极分别与nmos管m10的栅极、反相器u7的输出端和反相器u8的输入端连接;所述nmos管m13的源极与nmos管m14的漏极连接,其栅极作为计时频率振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m14的源极接地,其栅极作为计时频率振荡电路的v1端,并与电压偏置电路的v1端连接;所述电容c1的下极板接地;所述或非门u4的第一输入端与比较器u1的输出端连接,其第二输入端分别与或非门u5的输出端和反相器u7的输入端连接,其输出端分别与反相器u6的输入端和或非门u5的第一输入端连接;所述反相器u3的输入端与比较器u2的输出端连接,其输出端与或非门u5的第二输入端连接;所述反相器u6的输出端作为计时频率振荡电路的时钟输出端;所述比较器u1的反相端作为计时频率振荡电路的3.5v输入端;所述比较器u2的反相端作为计时频率振荡电路的1.5v输入端。

[0012]

进一步地,所述n位计数电路包括:n个d触发器;所述n个d触发器包括:第1d触发器、

……

、第id触发器、

……

和第nd触发器;

[0013]

所述第1d触发器的时钟输入端c作为n位计数电路的时钟输入端;所述第id触发器的反相输出端q

‑

分别与第i+1d触发器的时钟输入端c和第id触发器的数据输入端d连接,其中,n>i>=1;所述第id触发器的正相输出端q+作为n位计数电路的第i个输出端di;所述第nd触发器的反相输出端q

‑

与第nd触发器的数据输入端d连接,其正相输出端q+作为n位计数电路的第n个输出端dn。

[0014]

进一步地,所述主振荡电路包括:p型可调节电流源整列、n型可调节电流源整列、pmos管m15、pmos管m16、nmos管m17、nmos管m18、pmos管m19、nmos管m20、pmos管m21、nmos管m22、电容c2、比较器u9、比较器u10、反相器u11、或非门u12、或非门u13、反相器u14、反相器u15和反相器u16;

[0015]

所述pmos管m19的漏极分别与nmos管m20的漏极、pmos管m21的源极、nmos管m22的源极、电容c2的上极板、比较器u9的同相端和比较器u10的同相端连接,其栅极分别与nmos管m22的栅极和反相器u16的输出端连接,其源极分别与nmos管m20的源极和pmos管m16的漏极连接,并作为p型mos电流源端;所述pmos管m15的漏极与pmos管m16的源极连接,其栅极与电压偏置电路的v4端连接;所述pmos管m15的源极与主振荡电路的供电端vdd连接;所述

pmos管m16的栅极与电压偏置电路的v3端连接;所述pmos管m21的栅极分别与nmos管m20的栅极、反相器u16的输入端和反相器u15的输出端连接;所述pmos管m21的漏极分别与nmos管m22的漏极和nmos管m17的漏极连接,并作为n型mos电流源端;所述nmos管m17的源极与nmos管m18的漏极连接,其栅极与电压偏置电路的v2端连接;所述nmos管m18的源极接地,其栅极与电压偏置电路的v1端连接;所述电容c2的下极板接地;所述或非门u12的第一输入端与比较器u9的输出端连接,其第二输入端分别与或非门u13的输出端和反相器u15的输入端连接,其输出端分别与反相器u14的输入端和或非门u13的第一输入端连接;所述反相器u11的输入端与比较器u10的输出端连接,其输出端与或非门u13的第二输入端连接;所述反相器u14的输出端作为主振荡电路的clk端;所述比较器u9的反相端作为主振荡电路的3.5v输入端;所述比较器u10的反相端作为主振荡电路的1.5v输入端。

[0016]

进一步地,所述p型可调节电流源阵列包括:n列p型开关电流源;所述n列p型开关电流源包括:第1列p型开关电流源、

……

、第i列p型开关电流源、

……

和第n列p型开关电流源;

[0017]

所述第i列p型开关电流源包括:pmos管m1_i、pmos管m2_i和pmos管m3_i;所述pmos管m1_i的源极作为第i列p型开关电流源的供电端vdd,并与主振荡电路的供电端vdd连接;所述pmos管m1_i的漏极与pmos管m2_i的源极连接,其栅极作为主振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m2_i的漏极与pmos管m3_i的源极连接,其栅极作为主振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m3_i的漏极与p型mos电流源端连接,其栅极作为p型可调节电流源阵列的第i个输入端di,并与n位计数电路的第i个输出端di连接;所述pmos管m1_n的源极与第i列p型开关电流源的供电端vdd连接;所述pmos管m1_n的漏极与pmos管m2_n的源极连接,其栅极作为主振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m2_n的漏极与pmos管m3_n的源极连接,其栅极作为主振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m3_n的漏极与p型mos电流源端连接,其栅极作为p型可调节电流源阵列的第n个输入端dn,并与n位计数电路的第n个输出端dn连接。

[0018]

进一步地,所述n型可调节电流源阵列包括:n列n型开关电流源;所述n列n型开关电流源包括:第1列n型开关电流源、

……

、第i列n型开关电流源、

……

和第n列n型开关电流源;

[0019]

所述第i列n型开关电流源包括:nmos管m4_i、nmos管m5_i和nmos管m6_i;所述nmos管m4_i的漏极与n型mos电流源端连接,其源极与nmos管m5_i的漏极连接,其栅极作为n型可调节电流源阵列的第i个输入端di,并与n位计数电路的第i个输出端di连接;所述nmos管m5_i的源极与nmos管m6_i的漏极连接,其栅极作为主振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m6_i的源极接地,其栅极作为主振荡电路的v1端,并与电压偏置电路的v1端连接;所述nmos管m4_n的漏极与n型mos电流源端连接,其源极与nmos管m5_n的漏极连接,其栅极作为n型可调节电流源阵列的第n个输入端dn,并与n位计数电路的第n个输出端dn连接;所述nmos管m5_n的源极与nmos管m6_n的漏极连接,其栅极作为主振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m6_n的源极接地,其栅极作为主振荡电路的v1端,并与电压偏置电路的v1端连接。

[0020]

本实用新型的有益效果为:通过电压偏置电路为计时频率振荡电路以及主振荡电路产生mos管栅极电压偏置,采用计时频率振荡电路产生n位计数电路的基准频率,通过n位

计数电路在基准频率下的自增计数,持续性地微调主振荡电路输出信号的频率,形成一个振荡频率周期性缓慢变化的频率源。在频域上,这样的频率源频谱更宽,故而基于此实现的pwm波的pd快速充电器开关过程的能量突变不集中于单一频点,电磁干扰相对较弱,电磁兼容能力较传统技术更强。

附图说明

[0021]

图1为一种pd快充pwm芯片的电磁兼容频率源电路图;

[0022]

图2为一种pd快充pwm芯片的电磁兼容频率源频率输出频域示意图。

具体实施方式

[0023]

下面对本实用新型的具体实施方式进行描述,以便于本技术领域的技术人员理解本实用新型,但应该清楚,本实用新型不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本实用新型的精神和范围内,这些变化是显而易见的,一切利用本实用新型构思的发明创造均在保护之列。

[0024]

如图1所示,一种pd快充pwm芯片的电磁兼容频率源,包括:电压偏置电路、计时频率振荡电路、n位计数电路和主振荡电路;

[0025]

所述电压偏置电路分别与计时频率振荡电路和主振荡电路连接,用于产生mos管栅极电压偏置;所述计时频率振荡电路的时钟输出端与n位计数电路的时钟输入端连接,用于产生n位计数电路的基准频率;所述n位计数电路与主振荡电路连接,用于产生增计数模式的n位自增数据,控制主振荡电路,持续性地微调其频率输出;所述电压偏置电路的供电端vdd分别与计时频率振荡电路的供电端vdd和主振荡电路的供电端vdd连接,并作为电磁兼容频率源的直流供电端;所述计时频率振荡电路的3.5v输入端与主振荡电路的3.5v输入端连接,并作为电磁兼容频率源的第一输入端;所述计时频率振荡电路的1.5v输入端与主振荡电路的1.5v输入端连接,并作为电磁兼容频率源的第二输入端;所述主振荡电路的clk端作为电磁兼容频率源的输出端;n为闭区间[1,14]内的正整数。

[0026]

电压偏置电路包括:电流源i1、nmos管m1、nmos管m2、nmos管m3、nmos管m4、pmos管m5和pmos管m6;所述电流源i1的一端与pmos管m6的源极连接,并作为电压偏置电路的供电端vdd;所述电流源i1的另一端分别与nmos管m1的漏极、nmos管m1的栅极和nmos管m4的栅极连接,并作为电压偏置电路的v2端;所述nmos管m2的漏极分别与nmos管m1的源极、nmos管m2的栅极和nmos管m3的栅极连接,并作为电压偏置电路的v1端;所述pmos管m5的源极分别与pmos管m6的漏极和pmos管m6的栅极连接,并作为电压偏置电路的v4端;所述pmos管m5的漏极分别与pmos管m5的栅极和nmos管m4的漏极连接,并作为电压偏置电路的v3端;所述nmos管m3的漏极与nmos管m4的源极连接,其源极与nmos管m2的源极连接,并接地。

[0027]

电压偏置电路中,nmos管m1和nmos管m2各自的栅漏相接,形成了被标记为v2和v1的自偏置栅压,pmos管m5及pmos管m6同理,这些偏置电压可供给后续与其同等漏源堆叠关系的mos的栅极驱动电压,而每条mos管源漏通路的电流大小均由其名为宽长比的工艺参数决定。

[0028]

计时频率振荡电路包括:pmos管m7、pmos管m8、pmos管m9、nmos管m10、pmos管m11、nmos管m12、nmos管m13、nmos管m14、电容c1、比较器u1、比较器u2、反相器u3、或非门u4、或非

门u5、反相器u6、反相器u7和反相器u8;

[0029]

所述pmos管m7的源极作为计时频率振荡电路的供电端vdd,其漏极与pmos管m8的源极连接,其栅极作为计时频率振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m8的漏极分别与pmos管m9的源极和nmos管m10的源极连接,其栅极作为计时频率振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m9的漏极分别与nmos管m10的漏极、pmos管m11的源极、nmos管m12源极、电容c1的上极板、比较器u1的同相端和比较器u2的同相端连接,其栅极分别与nmos管m12的栅极和反相器u8的输出端连接;所述pmos管m11的漏极分别与nmos管m12的漏极和nmos管m13的漏极连接,其栅极分别与nmos管m10的栅极、反相器u7的输出端和反相器u8的输入端连接;所述nmos管m13的源极与nmos管m14的漏极连接,其栅极作为计时频率振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m14的源极接地,其栅极作为计时频率振荡电路的v1端,并与电压偏置电路的v1端连接;所述电容c1的下极板接地;所述或非门u4的第一输入端与比较器u1的输出端连接,其第二输入端分别与或非门u5的输出端和反相器u7的输入端连接,其输出端分别与反相器u6的输入端和或非门u5的第一输入端连接;所述反相器u3的输入端与比较器u2的输出端连接,其输出端与或非门u5的第二输入端连接;所述反相器u6的输出端作为计时频率振荡电路的时钟输出端;所述比较器u1的反相端作为计时频率振荡电路的3.5v输入端;所述比较器u2的反相端作为计时频率振荡电路的1.5v输入端。

[0030]

在计时频率振荡电路中,pmos管m7和pmos管m8分别由v3端和v4端的栅极驱动电压驱动,形成了电容c1的充电电流源,与pmos管m9和nmos管m10构成了电容c1的充电链路;nmos管m13和nmos管m14分别由v1端和v2端的栅极驱动电压驱动,形成了电容c1的放电电流源,与pmos管m11和nmos管m12构成了电容c1的放电链路;pmos管m9和nmos管m10构成了cmos互补开关,pmos管m11和nmos管m12构成了同样结构的cmos互补开关,两个cmos互补开关由互为180

°

反相的两个信号控制,即不让电容c1的充放电链路同时开启,又受后续电路的反馈控制。反相器u3、反相器u6、反相器u7、或非门u4和或非门u5构成了一个实现逻辑转换的电路,将比较器u1和比较器u2的输出信号进行转换,实现一个特定的功能,即当电容c1的上极板电压大于3.5v,计时频率振荡电路的时钟输出端由低电平翻转为高电平,电容c1充电链路关断,放电链路开启,继而当电容c1的上极板电压小于1.5v,计时频率振荡电路的时钟输出端输出低电平,同时放电链路关断,充电链路开启。在上述机理的运行过程下,实现了在1.5v阈值和3.5v阈值辖制下,一个与充电电流大小、放电电流大小以及电容容值三个因素相关的精准频率源,该频率源输出方波信号,占空比以及频率分别由充电时间和放电时间的比例以及总长决定。

[0031]

n位计数电路包括:n个d触发器;所述n个d触发器包括:第1d触发器、

……

、第id触发器、

……

和第nd触发器;所述第1d触发器的时钟输入端c作为n位计数电路的时钟输入端;所述第id触发器的反相输出端q

‑

分别与第i+1d触发器的时钟输入端c和第id触发器的数据输入端d连接,其中,n>i>=1;所述第id触发器的正相输出端q+作为n位计数电路的第i个输出端di;所述第nd触发器的反相输出端q

‑

与第nd触发器的数据输入端d连接,其正相输出端q+作为n位计数电路的第n个输出端dn。

[0032]

上述结构实现了一个增计数工作模式的计数器,即计时频率振荡电路的时钟输出端每出现一个上升沿,便自增一次的n位计数器,在本实施例中,n设置为8,n位计数器可计

数范围为0~255。

[0033]

主振荡电路包括:p型可调节电流源整列、n型可调节电流源整列、pmos管m15、pmos管m16、nmos管m17、nmos管m18、pmos管m19、nmos管m20、pmos管m21、nmos管m22、电容c2、比较器u9、比较器u10、反相器u11、或非门u12、或非门u13、反相器u14、反相器u15和反相器u16;

[0034]

所述pmos管m19的漏极分别与nmos管m20的漏极、pmos管m21的源极、nmos管m22的源极、电容c2的上极板、比较器u9的同相端和比较器u10的同相端连接,其栅极分别与nmos管m22的栅极和反相器u16的输出端连接,其源极分别与nmos管m20的源极和pmos管m16的漏极连接,并作为p型mos电流源端;所述pmos管m15的漏极与pmos管m16的源极连接,其栅极与电压偏置电路的v4端连接;所述pmos管m15的源极与主振荡电路的供电端vdd连接;所述pmos管m16的栅极与电压偏置电路的v3端连接;所述pmos管m21的栅极分别与nmos管m20的栅极、反相器u16的输入端和反相器u15的输出端连接;所述pmos管m21的漏极分别与nmos管m22的漏极和nmos管m17的漏极连接,并作为n型mos电流源端;所述nmos管m17的源极与nmos管m18的漏极连接,其栅极与电压偏置电路的v2端连接;所述nmos管m18的源极接地,其栅极与电压偏置电路的v1端连接;所述电容c2的下极板接地;所述或非门u12的第一输入端与比较器u9的输出端连接,其第二输入端分别与或非门u13的输出端和反相器u15的输入端连接,其输出端分别与反相器u14的输入端和或非门u13的第一输入端连接;所述反相器u11的输入端与比较器u10的输出端连接,其输出端与或非门u13的第二输入端连接;所述反相器u14的输出端作为主振荡电路的clk端;所述比较器u9的反相端作为主振荡电路的3.5v输入端;所述比较器u10的反相端作为主振荡电路的1.5v输入端。

[0035]

p型可调节电流源阵列包括:n列p型开关电流源;所述n列p型开关电流源包括:第1列p型开关电流源、

……

、第i列p型开关电流源、

……

和第n列p型开关电流源;所述第i列p型开关电流源包括:pmos管m1_i、pmos管m2_i和pmos管m3_i;所述pmos管m1_i的源极作为第i列p型开关电流源的供电端vdd,并与主振荡电路的供电端vdd连接;所述pmos管m1_i的漏极与pmos管m2_i的源极连接,其栅极作为主振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m2_i的漏极与pmos管m3_i的源极连接,其栅极作为主振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m3_i的漏极与p型mos电流源端连接,其栅极作为p型可调节电流源阵列的第i个输入端di,并与n位计数电路的第i个输出端di连接;所述pmos管m1_n的源极与第i列p型开关电流源的供电端vdd连接;所述pmos管m1_n的漏极与pmos管m2_n的源极连接,其栅极作为主振荡电路的v4端,并与电压偏置电路的v4端连接;所述pmos管m2_n的漏极与pmos管m3_n的源极连接,其栅极作为主振荡电路的v3端,并与电压偏置电路的v3端连接;所述pmos管m3_n的漏极与p型mos电流源端连接,其栅极作为p型可调节电流源阵列的第n个输入端dn,并与n位计数电路的第n个输出端dn连接。

[0036]

n型可调节电流源阵列包括:n列n型开关电流源;所述n列n型开关电流源包括:第1列n型开关电流源、

……

、第i列n型开关电流源、

……

和第n列n型开关电流源;所述第i列n型开关电流源包括:nmos管m4_i、nmos管m5_i和nmos管m6_i;所述nmos管m4_i的漏极与n型mos电流源端连接,其源极与nmos管m5_i的漏极连接,其栅极作为n型可调节电流源阵列的第i个输入端di,并与n位计数电路的第i个输出端di连接;所述nmos管m5_i的源极与nmos管m6_i的漏极连接,其栅极作为主振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m6_i的源极接地,其栅极作为主振荡电路的v1端,并与电压偏置电路的v1端连接;所述nmos

管m4_n的漏极与n型mos电流源端连接,其源极与nmos管m5_n的漏极连接,其栅极作为n型可调节电流源阵列的第n个输入端dn,并与n位计数电路的第n个输出端dn连接;所述nmos管m5_n的源极与nmos管m6_n的漏极连接,其栅极作为主振荡电路的v2端,并与电压偏置电路的v2端连接;所述nmos管m6_n的源极接地,其栅极作为主振荡电路的v1端,并与电压偏置电路的v1端连接。

[0037]

主振荡电路的机理与计时频率振荡电路完全一致,而其他方面与之不同的是,充电电流和放电电流的大小根据工程所需,远低于计时频率振荡电路,由前文所述,电流大小由各个mos管的工艺参数宽长比进行设定;同时还在充电链路和放电链路中分别并联了受n位计数电路的n个输出端作为开关控制的p型可调节电流源阵列和n型可调节电流源阵列,以此实现电流的周期性缓慢变化,从而形成一个振荡频率周期性缓慢变化的频率源。频率输出频域示意如图2所示。

[0038]

综上,本实用新型通过电压偏置电路为计时频率振荡电路以及主振荡电路产生mos管栅极电压偏置,采用计时频率振荡电路产生n位计数电路的基准频率,通过n位计数电路在基准频率下的自增计数,持续性地微调主振荡电路输出信号的频率,形成一个振荡频率周期性缓慢变化的频率源。在频域上,这样的频率源频谱更宽,故而基于此实现的pwm波的pd快速充电器开关过程的能量突变不集中于单一频点,电磁干扰相对较弱,电磁兼容能力较传统技术更强。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1