比较器迟滞电路的制作方法

比较器迟滞电路

背景技术:

1.比较器是比较两个模拟输入电压或电流信号的振幅且产生指示两个模拟输入信号中的一者是否大于另一者的振幅的输出信号的电路装置。在一些比较器中,当两个输入信号大体上相等时,输出改变状态,此可导致比较器输出响应于输入信号上的噪声而切换于状态之间。为了防止此问题,一些比较器应用迟滞来基于输出状态提供个别跳变阈值,借此降低在输入信号的电压电平彼此非常接近时噪声诱发切换的发生率。

技术实现要素:

2.本文中公开降低由基于比较器输出的转变在不同差分对之间切换引起的输出瞬态故障的发生率的比较器电路。在一个实例中,一种比较器电路包含信号输入端子、输出端子、第一晶体管、第二晶体管、第三晶体管、第四晶体管及时序电路。所述第一晶体管包含耦合到第一迟滞电压电路的第一端子。所述第二晶体管包含耦合到所述信号输入端子的第一端子及耦合到所述第一晶体管的第二端子的第二端子。所述第三晶体管包含耦合到所述第一晶体管的第三端子的第一端子及耦合到电力轨的第二端子。所述第四晶体管包含耦合到所述第二晶体管的第三端子的第一端子及耦合到所述电力轨的第二端子。所述时序电路包含输入端子、第一输出、第二输出及延迟电路。所述输入端子耦合到所述输出端子。所述第一输出耦合到所述第三晶体管的第三端子。所述第二输出耦合到所述第四晶体管的第三端子。所述延迟电路包含耦合到所述第一输出的输入端子及耦合到所述第二输出的输出端子。

3.在另一实例中,一种比较器电路包含第一晶体管、第二晶体管、第一开关、第二开关及时序电路。所述第一晶体管及所述第二晶体管耦合为差分对且经配置以比较输入信号与迟滞电压。所述第一开关耦合到所述第一晶体管且经配置以可选择地启用所述第一晶体管。所述第二开关耦合到所述第二晶体管且经配置以可选择地启用所述第二晶体管。所述时序电路耦合到所述第一开关及所述第二开关且经配置以响应于所述比较器电路的输出处的信号转变而闭合所述第一开关且在所述第一开关闭合之后的预定延迟时间闭合所述第二开关。

4.在另一实例中,一种比较器电路包含信号输入端子、输出端子、第一输入电路、第二输入电路及时序电路。所述第一输入电路包含第一晶体管、第二晶体管、第三晶体管及第四晶体管。所述第一晶体管包括耦合到第一迟滞电压电路的第一端子。所述第二晶体管包含耦合到所述信号输入端子的第一端子及耦合到所述第一晶体管的第二端子的第二端子。所述第三晶体管包含耦合到所述第一晶体管的第三端子的第一端子及耦合到电力轨的第二端子。所述第四晶体管包含耦合到所述第二晶体管的第三端子的第一端子及耦合到所述电力轨的第二端子。所述第二输入电路包含第五晶体管、第六晶体管、第七晶体管及第八晶体管。所述第五晶体管包含耦合到第二迟滞电压电路的第一端子。所述第六晶体管包含耦合到所述信号输入端子的第一端子及耦合到所述第五晶体管的第二端子的第二端子。所述第七晶体管包含耦合到所述第五晶体管的第三端子的第一端子及耦合到所述电力轨的第

二端子。所述第八晶体管包含耦合到所述第六晶体管的第三端子的第一端子及耦合到所述电力轨的第二端子。所述时序电路包含输入端子、第一输出、第二输出、第三输出及第四输出。所述输入端子耦合到所述输出端子。所述第一输出耦合到所述第三晶体管的第三端子。所述第二输出耦合到所述第四晶体管的第三端子。所述第三输出耦合到所述第七晶体管的第三端子。所述第四输出耦合到所述第八晶体管的第三端子。

附图说明

5.关于各种实例的详细描述,现将参考附图,其中:

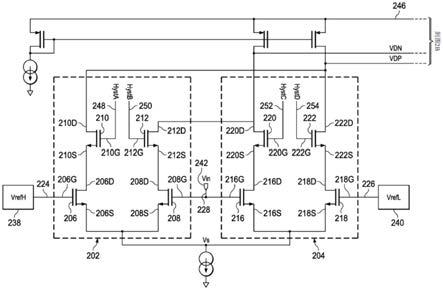

6.图1展示使用两个输入电路提供准确迟滞的实例比较器电路的示意图;

7.图2a及2b展示在两个输入电路之间切换时提供准确迟滞同时减少输出瞬态故障的实例比较器电路的示意图;

8.图3展示在图2a及2b的比较器电路中产生的实例信号;

9.图4a及4b展示由图1的比较器电路及图2a及2b的比较器电路产生的输出信号的比较;及

10.图5a及5b展示在图2a及2b的比较器电路中提供的定时器电路中的延迟电路系统的实例。

具体实施方式

11.在本描述中,术语“耦合”意指间接或直接有线或无线连接。因此,如果第一装置耦合到第二装置,那么所述连接可通过直接连接或通过经由其它装置及连接的间接连接。此外,在本描述中,表述“基于”意指“至少部分基于”。因此,如果x基于y,那么x可为y及各种其它因素的函数。

12.许多比较器应用迟滞来抑制输入信号上的噪声。跨比较器施加的迟滞的准确性广泛变化。举例来说,在一些比较器中,迟滞电压可变化高达50%。提供准确迟滞的一些比较器使用两个差分对产生迟滞,其中每一差分对连接到不同参考电压。

13.图1展示使用两个输入电路提供准确迟滞的实例比较器电路100的示意图。比较器电路100包含输入电路102及输入电路104。输入电路102包含形成差分对的晶体管106及108及用作开关以启用或停用差分对的晶体管110及112。类似地,输入电路104包含形成差分对的晶体管116及118及用作开关以启用或停用差分对的晶体管120及122。如果比较器电路100的输出端子114处的电压为逻辑“低”,那么启用输入电路102以比较输入信号128与高迟滞电压124,且当输入信号128大于高迟滞电压124时,比较器电路100的输出将改变为逻辑“高”。如果比较器电路100的输出端子输出端子114处的电压为逻辑“高”,那么启用输入电路104以比较输入信号128与低迟滞电压126,且当输入信号128小于低迟滞电压126时,比较器电路100的输出将改变为逻辑“低”。因此,比较器电路100中应用的迟滞由高迟滞电压124与低迟滞电压126的差精确确定。

14.当输入信号128缓慢减小且例如穿越低迟滞电压126时,输出节点130处的电压也将缓慢改变。然而,控制信号132及134将快速改变以停用输入电路104且启用输入电路102。随着输入电路102启用,晶体管106及晶体管108的漏极处的寄生电容器被充电,此在晶体管110及晶体管112中诱发共模电流且又引起晶体管110及晶体管112的漏极处的电压下降。因

为从晶体管112的漏极到输出节点130的信号路径比从晶体管110的漏极到输出节点130的信号路径更短,所以输出节点130处的电压将瞬时增大且可能在输出端子114上引起瞬态故障。

15.比较器电路100的一些实施方案匹配从晶体管110、晶体管112、晶体管120及晶体管122的漏极到输出节点130的信号路径以抵消寄生电容器充电电流的效应。然而,匹配这些路径的时序较困难,且即使时序匹配,但晶体管106、晶体管108、晶体管116及晶体管118的漏极端子处的寄生电容差可产生足以在输出端子114处引起瞬态故障的时序差。

16.图2a及2b展示在两个输入电路之间切换时提供准确迟滞同时减少输出瞬态故障的实例比较器电路200的示意图。比较器电路200不是尝试匹配路径时序,而是控制差分对的启用时序以减少或消除比较器输出处的瞬态故障。比较器电路200包含输入电路202、输入电路204、信号输入端子242、输出端子214、输出电路系统258及时序电路232。输入电路202包含形成差分对的晶体管206及208及用作开关以启用或停用差分对的晶体管210及212。晶体管206的源极端子206s耦合到晶体管208的源极端子208s。晶体管206的栅极端子206g耦合到产生迟滞电压224的迟滞电压电路238。迟滞电压224设置从逻辑“低”转变到逻辑“高”的阈值。晶体管206的漏极端子206d耦合到晶体管210的源极端子210s。晶体管210的漏极端子210d耦合到电力轨246及输出电路系统258。

17.晶体管208的栅极端子208g耦合到信号输入端子242用于接收输入信号228来与迟滞电压224比较。晶体管208的漏极端子208d耦合到晶体管212的源极端子212s。晶体管212的漏极端子212d耦合到电力轨246及输出电路系统258。

18.输入电路204包含形成差分对的晶体管216及218及用作开关以启用或停用差分对的晶体管220及222。晶体管216的源极端子216s耦合到晶体管218的源极端子218s。晶体管216的栅极端子216g耦合到信号输入端子242用于接收输入信号228。晶体管216的漏极端子216d耦合到晶体管220的源极端子220s。晶体管220的漏极端子220d耦合到晶体管212的212d、电力轨246及输出电路系统258。

19.晶体管218的栅极端子218g耦合到产生迟滞电压226用于与输入信号228比较的迟滞电压电路240。晶体管218的漏极端子218d耦合到晶体管222的源极端子222s。晶体管222的漏极端子222d耦合到晶体管210的210d、电力轨246及输出电路系统258。

20.时序电路232包含耦合到输出端子214的输入端子232a、耦合到输入端子232a的输出232b、耦合到输入端子232a的输出232c、延迟电路234及延迟电路236。延迟电路234包含耦合到输出232b的输入端子234a及耦合到时序电路232的输出232c的输出端子234b。延迟电路236包含耦合到时序电路232的输出232d的输入端子236a及耦合到时序电路232的输出232e的输出端子236b。时序电路232的输出232b耦合到晶体管210的栅极端子210g。时序电路232的输出232c耦合到晶体管212的栅极端子212g。时序电路232的输出232d耦合到晶体管220的栅极端子220g。时序电路232的输出232e耦合到晶体管222的栅极端子222g。

21.时序电路232在比较器输出信号244的每一转变处使晶体管210、晶体管212、晶体管220及晶体管222中的每一者的导通及关断排序以抑制输出端子214处的瞬态故障。时序电路232延迟晶体管212相对于晶体管210的导通且延迟晶体管222相对于晶体管220的导通。由延迟电路234及延迟电路236提供的延迟操作为时域迟滞以防止输出端子214处的瞬态故障。由延迟电路234提供的延迟时间至少与从晶体管210的漏极端子210d及晶体管212

的漏极端子212d到输出节点230的传播延迟差一样大。类似地,由延迟电路236提供的延迟时间至少与从晶体管220的漏极端子220d及晶体管222的漏极端子222d到输出节点230的传播延迟差一样大。延迟确保较长路径中的信号不晚于较短路径中的信号到达输出节点230。

22.图3展示在比较器电路200中产生的实例信号。随着输出节点230处的电压256缓慢下降,比较器输出信号244(vout)在302处从逻辑“高”切换到逻辑“低”。此后不久,在时间304,时序电路232激活控制信号248(hysta)以导通晶体管210,且取消激活控制信号252(hystc)及控制信号254(hystd)以关断晶体管220及晶体管222。在延迟306之后,时序电路232激活控制信号250(hystb)以导通晶体管212。

23.随着输出节点230处的电压256缓慢上升,比较器输出信号244(vout)在310处从逻辑“低”切换到逻辑“高”。此后不久,在时间312,时序电路232激活控制信号252(hystc)以导通晶体管220,且取消激活控制信号248(hysta)及控制信号250(hystb)以关断晶体管210及晶体管212。在延迟314之后,时序电路232激活控制信号254(hystd)以导通晶体管222。

24.图4a及4b展示由比较器电路100及比较器电路200产生的输出信号的比较。图4a将输入信号128及输入信号228展示为缓慢改变的三角形斜坡。比较器电路100的输出节点130处的电压156及比较器电路200的输出节点230处的电压256随着输入信号128上升及下降而切换。在图4a的时标处,瞬态故障在电压156或电压256的边沿处不可见。图4b展示电压156及电压256在明显更高时标处的下降沿。随着电压156下降,瞬态故障402由来自晶体管120及晶体管122的路径延迟差引起。瞬态故障可触发输出端子114处逻辑信号电平的改变。随着电压256下降,产生明显更小瞬态故障404。瞬态故障404的电平不足以触发比较器输出信号244的逻辑电平改变。

25.图5a及5b展示比较器电路200的时序电路232中的电路系统的实例。图5a展示用于产生控制信号248(hysta)及控制信号250(hystb)的实例电路系统。耦合到输入端子232a及输出端子232b的反相器502产生控制信号248。延迟电路234包含延迟单元504及and门506。延迟单元504使反相器502的输出延迟达延迟306,且and门506组合反相器502的输出与延迟单元504的输出以产生控制信号250。延迟单元504可包含产生延迟306所需的任何数目个延迟元件(例如反相器)。

26.图5b展示用于产生控制信号252(hystc)及控制信号254(hystd)的实例电路系统。耦合到输入端子232a及输出232d的非反相缓冲器512产生控制信号252。延迟电路236包含延迟单元514及and门516。延迟单元514使非反相缓冲器512的输出延迟达延迟314,且and门516组合非反相缓冲器512的输出与延迟单元514的输出以产生控制信号254。延迟单元514可包含产生延迟314所需的任何数目个延迟元件(例如反相器)。

27.在权利要求书的范围内,可修改所描述实施例,且其它实施例是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1