传感器电路的制作方法

1.本说明书总体上涉及包括δ-σ模数转换器的传感器电路。传感器电路可以与光传感器和其他传感器一起使用。

背景技术:

2.对于诸如移动电话的电子设备来说,能够感测环境光水平是有用的,例如,使得可以控制显示器照明以降低功耗。环境传感器电路的先前公开包括us2014/293272(us9146162)和ep2863192。us 2014/293272描述了一种积分模数转换器,其可在光传感器和温度传感器之间切换。ep2863192描述了一种具有两阶段操作的模数转换器,一个阶段包括电荷平衡操作。

技术实现要素:

3.总体上描述了一种传感器电路,传感器电路包括具有开关网络配置的δ-σ模数转换器,与一些现有技术的δ-σ模数转换技术相比,开关网络配置有助于增加增益和降低噪声操作。

4.根据第一方面,提供了一种包括传感器输入的传感器电路。传感器电路可以包括δ-σ模数转换器,δ-σ模数转换器包括具有在第一积分器输入处的第一求和结点的第一积分器、第一反馈电容器和第一积分器输出。传感器输入可以耦合到第一求和结点。传感器电路还可以包括比较器,其耦合到第一积分器输出并且被配置为将第一积分器输出与比较器参考进行比较以生成比较器输出。传感器电路还可以包括耦合到比较器输出的数字输出以及转换器时钟。

5.δ-σ模数转换器还可以包括第一开关电容器、提供共模电压(v

cm

)的共模电压源、提供参考电压(v

ref

)的参考电压源和第一开关网络。第一开关网络可以被配置为:在第一时钟阶段中,将第一开关电容器连接到共模电压和参考电压之一,以将开关电容器充电到共模电压与参考电压之和或共模电压与参考电压之差,以及在第二时钟阶段中,连接第一开关电容器以将电荷从第一开关电容器转移到第一求和结点中,以及控制器,其响应于比较器输出来控制第一开关网络,以在第一时钟阶段中将第一开关电容器选择性地连接到共模电压和参考电压之一。

6.在实施方式中,这种方法允许第一开关电容器取决于比较器输出对(v

cm

+v

ref

)或(v

cm-v

ref

)进行采样。因此,在实施方式中,积分器输出(和数字码)可以取决于时钟的周期(频率)而不是总转换时间。然而,这种方法的简单实施方式可能会导致时钟馈通。上述第一开关网络的实施方式可以显著减少这种和其他开关相关的误差,例如由电荷注入引起的误差。在一些实施方式中,v

ref

可以小于v

cm

。

7.以上和稍后描述的特征的一些其他优点包括增益可编程性,例如通过改变时钟频率或参考电压。所描述的电路配置有助于高增益和低噪声,例如,在fa范围内解析电流,这有助于测量非常低的光水平。在实施方式中,噪声通过过采样率(over-sampling ratio,

osr)降低,并且对于给定增益,噪声可以独立于感测信号(光输入)。所描述的切换布置可以提供噪声整形并且有助于用于改进信噪比(snr)感测的抽取。

8.传感器电路的实施方式可以测量正光电二极管电流和负光电二极管电流两者,特别是光电二极管泄漏或暗电流。然后可以为数字输出定义对应于零电流输入的零光条件;这可以被定义为中间码数字输出。

9.在实施例中,开关网络包括可控共模电压开关和可控参考电压开关,可控共模电压开关和可控参考电压开关各自耦合到第一开关电容器的第一端子。可控接地开关可以耦合到第一开关电容器的第二端子。可控积分器输入开关可以耦合在第一开关电容器的第二端子与求和结点之间。这提供了第一开关网络的高效实现。

10.控制器然后可被配置为在第一时钟阶段中控制可控共模电压开关和可控参考电压开关以将第一开关电容器的第一端子连接到共模电压和参考电压之一,并且控制可控接地开关以将第一开关电容器的第二端子接地。控制器可以被配置为在第二时钟阶段中控制可控积分器输入以将第一开关电容器的第二端子耦合到求和结点。

11.在实施例中,模数转换器还包括耦合在第一积分器和比较器之间的第二积分器,第二积分器包括在第二积分器输入处的第二求和结点、第二反馈电容器和第二积分器输出,第二积分器输入耦合到第一积分器输出,并且第二积分器输出耦合到比较器输入。这可以有助于在低噪声的情况下提高增益。

12.传感器电路还可以包括耦合电容器和耦合开关网络,以将第一积分器输出耦合到第二积分器输入。耦合开关网络可以被配置为首先耦合来自第一积分器输出的电压以对耦合电容器充电,然后将来自耦合电容器的电荷耦合到第二积分器输入。传感器电路的增益可以由第二反馈电容器的值与耦合电容器的值的比率来确定。

13.在特定实施例中,耦合开关网络包括:将第一积分器输出与耦合电容器的第一端子耦合的第一耦合开关;将耦合电容器的第一端子与共模电压源耦合的第二耦合开关,将耦合电容器的第二端子耦合到第二积分器输入的第三耦合开关,以及将耦合电容器的第二端子耦合到共模电压源的第四耦合开关。

14.这有助于耦合二阶δ-σ模数转换器的两个级,其中每个级包括如前所述的开关网络。

15.因此,传感器电路还可以包括耦合到第二求和结点的第二开关电容器,以及第二开关网络,该第二开关网络被配置为:在第二时钟阶段中,将第二开关电容器连接到共模电压和参考电压之一,以将开关电容器充电到共模电压与参考电压之和或共模电压与参考电压之差,并且在第一时钟阶段中,连接第二开关电容器以将电荷从开关电容器转移到第二求和结点中。

16.在二阶δ-σ模数转换器中,转换器时钟可以被配置为提供定义第一时钟阶段并控制第三耦合开关的第一阶段定时信号(φ1)、控制第二耦合开关的第一另外的阶段定时信号(φ

1d

)、定义第二时钟阶段并控制第四耦合开关的第二阶段定时信号(φ2)以及控制第一耦合开关的第二另外的阶段定时信号(φ

2d

)。

17.在实施例中,第一开关电容器、耦合电容器、第二开关电容器、第一反馈电容器和第二反馈电容器中的一个或多个(在存在的情况下)可以是可变的(例如开关电容器)。这可以有助于对模数转换器的增益进行编程。然而,在一些实施方式中,可能优选的是使用时钟

频率和/或参考电压来改变增益,而不是将开关引入到信号路径中。

18.传感器电路还可以包括耦合在比较器输出和数字输出之间的抽取器。这进一步有助于降噪。在实施方式中,抽取器可以包括级联积分梳状(cascaded integrator

–

comb,cic)滤波器,例如三阶cic滤波器。

19.在实施例中,控制器还包括耦合在比较器输出和控制器之间的锁存电路,以将比较器输出的变化同步到第一时钟阶段和第二时钟阶段中的一个或两个。这可以帮助确保不重叠的控制信号。

20.在一些实施方式中,控制器还可以包括逻辑电路,以将与第一时钟阶段(φ1)同步的比较器输出与第一另外的阶段定时信号(φ

1d

)组合;以及将与第二时钟阶段(φ2)同步的比较器输出与第二另外的阶段定时信号(φ

2d

)组合,以生成用于逻辑电路的组合信号,以生成一个或多个控制信号来控制第一开关网络。然而,在一些其他实施方式中,可以省略这样的逻辑电路,并且可以复制第一(或第二)开关网络的开关,例如可控共模电压开关和可控参考电压开关。

21.在一些实施方式中,传感器电路被配置为在每个时钟周期将电荷转移到第一反馈电容器,而不管由比较器输出指示的比较器判定。

22.该电路可以与用于诸如便携式计算设备或移动电话的电子设备的光传感器(诸如环境光传感器)的光电二极管一起使用。因此,光电二极管可以耦合到传感器输入。

附图说明

23.现在将参考以下附图通过示例实施例来描述传感器电路:

24.图1是环境光传感器系统的示意图。

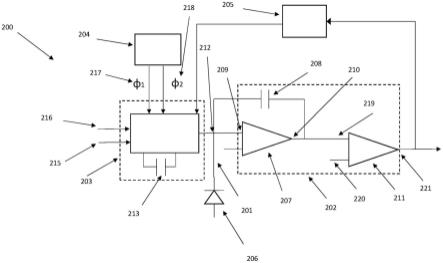

25.图2是根据实施例的传感器电路的示意图。

26.图3是根据实施例的第一开关网络的示意图。

27.图4是指示根据实施例的控制器的操作的流程图。

28.图5(a)是根据第一时钟阶段配置的开关网络的示意图。

29.图5(b)是根据第二时钟阶段配置的开关网络的示意图。

30.图6是根据实施例的具有第二级积分器的传感器电路的示意图。

31.图7是根据实施例的耦合电路的示意图。

32.图8是根据实施例的第二开关网络的示意图。

33.图9(a)是示出定时电路的图。

34.图9(b)是示出图9(a)的定时电路的输出信号的时序图。

35.图10是示出根据实施例的锁存电路的示意图。

36.图11是示出根据图10的实施例的锁存电路的输入、输出和中间信号的时序图。

37.图12(a)和12(b)是根据实施例的示例传感器电路的示意图。

具体实施方式

38.本文描述了一种用于传感器的低噪声、高灵敏度δ-σ模数转换器传感器电路。传感器可以是光传感器,诸如环境光传感器;δ-σ模数转换器可以是二阶转换器。

39.图1是环境光传感器系统100的示意图。该系统包括光电二极管101、被配置为通过

积分电容器cf 103作为积分器操作的运算放大器102、包括参考电容器cref的开关参考电路104、比较器105、以及提供数字输出107和可选地提供微调信号108以控制运算放大器102的偏移的控制逻辑106。高和低(例如接地)参考电压vrefh和vrefl被提供给开关参考电路104。

40.在操作中,积分器对通过光电二极管的电流101a进行积分,从而使运算放大器的输出处的电压斜升。使用比较器将该电压与参考电压进行比较。当运算放大器的输出电压越过参考电压时,比较器触发,并且在输出处提供电压,并且重复该过程。比较器输出在给定时间内被触发的次数被称为计数;该计数给出了环境光水平的指示。该系统使用异步时钟。

41.在输出处提供的电压由下式给出:

42.(vrefl+vrefh)*(cf/cref)

ꢀꢀꢀ

等式1

43.计数等式为:

[0044][0045]

现在描述低噪声、高灵敏度δ-σ模数转换器传感器电路。更具体地,描述了一种δ-σ转换器,其中电荷转储(charge dump)包括根据比较器判定的两个电平。在实施例中,电荷转储发生在每个时钟周期。在另一实施例中,提供用于δ-σ转换器的第二级。这使得能够改善信噪比。抽取器可以提供信噪比和噪声整形的进一步改进。

[0046]

在实施方式中,输出信号与时钟速率tclk成比例,而与传统的光-数字转换器相比,与总转换时间无关。实施方式具有测量正暗电流和负暗电流(光电二极管泄漏、电路泄漏)的能力。零光条件(零电流输入)可以称为中间码。此外,可以通过改变时钟速率和参考电压来实现增益可编程性。使用根据本公开的实施例的装置的结果表明,与传统的光-数字转换器相比,可以实现更高的增益(高达40倍)。根据本公开的实施例的设备还可以在降低噪声的情况下测量非常低的光水平。

[0047]

在第一实施例中,提供了一种单级δ-σ转换器。在该实施例中,使用两阶段方法。传感器电路包括连接到积分器的负端子的二极管、采样网络和比较器,该采样网络被配置为在第一阶段对参考电压进行采样,并且在第二阶段将采样的电压传送到积分器电路。传送的电压取决于前一时钟周期的比较器判定。提供两个电压电平。在实施例中,这些电压是共模电压(称为vcm)和参考电压vref。通常,参考电压低于共模电压。在实施例中,共模电压也是比较器的判定电平电压。如果比较器判定为高,则连接的参考电压等于vcm+vref,并且如果比较器判定为低,则连接vcm-vref。以这种方式,在每个时钟周期发生电荷转移,其中时钟周期tclk包括第一阶段和第二阶段。每个时钟周期上发生转移,而与比较器判定无关。本领域技术人员将理解,存在替代实施方式,诸如提供两个电压电平,一个高于比较器判定电平,一个低于比较器判定电平。本发明不限于采样电路的布置的细节。

[0048]

使用单个参考方案来创建平衡参考vrefp(vcm+vref)和vrefn(vcm-vref))可以克服小的失配可能导致输出码中的大误差的问题。单个参考方案仅使用vref和vcm来创建平衡参考。在一些实施方式中,通过在每个时钟阶段φ1和φ2锁存比较器输出来有助于稍后描述的切换定时。

[0049]

图2是根据实施例的传感器电路200的示意图。传感器电路包括传感器输入201、

δ-σ模数转换器202、第一开关网络203、转换器时钟204和控制器205。在实施方式中,传感器输入201接收模拟输入信号,例如电流输入信号。

[0050]

在图2的实施例中,传感器输入被示出为附接到光电二极管206。光电二极管的第二端子可以连接到地或另一参考电压。在一些实施方式中,传感器电路可以具有多通道输入和数字输出,例如通过复制图2中所示的电路的部分或全部和/或通过多路复用该电路。例如,光电二极管206可以感测多于一种波长,例如,它可以感测红色、绿色和/或蓝色和/或可以感测这些颜色中的多于一种。例如,可以采用诸如光像素(photopixel)的传感器,例如在一个或多个光感测元件(例如光电二极管)上具有红色、绿色、蓝色和透明滤光器。在其他应用中,该电路可以与其他输入设备一起使用,例如但不限于温度传感器。

[0051]

δ-σ转换器202包括第一积分器207、第一反馈电容器208、第一积分器输入209、第一积分器输出210和比较器211。积分器具有在第一积分器输入处的第一求和结点212,其中传感器输入耦合到第一求和结点。在实施例中,积分器被配置为反相放大器,其中负端子是第一积分器输入,并且正端子处于接地或另一参考电压。第一积分器的输出210耦合到比较器211的第一输入219。比较器的第二输入220耦合到参考电压电平,在实施例中,参考电压电平是共模电压。比较器的输出221连接到控制器205,并且还可以提供来自模数转换器的数字输出。

[0052]

传感器电路还包括第一开关电容器213,其在操作中被充电到第一电压电平或第二电压电平。在该实施例中,第一电压电平等于共模电压和参考电压之和,并且第二电压电平等于共模电压和参考电压之差。在实施例中,共模电压等于比较器211的参考电压。第一开关网络203控制第一开关电容器的充电,并且具有提供共模电压的共模电压源215和提供参考电压的参考电压源216。

[0053]

在操作中,根据图2的实施例的设备具有两个阶段。在第一阶段,由第一开关网络对电压进行采样。在第二阶段,第一开关网络连接到积分器的求和输入。以这种方式,发生电荷转储到第一反馈电容器上。

[0054]

在实施例中,转换器时钟提供第一定时信号217和第二定时信号218,以分别启动第一阶段和第二阶段。在第一阶段中,第一开关网络被配置为将第一开关电容器连接到一个或多个电压源,以便提供第一电压电平或第二电压电平。在实施例中,提供共模电压和参考电压,以便将开关电容器充电到共模电压和参考电压之和或共模电压和参考电压之差。

[0055]

在第二阶段,第一开关电容器与第一积分器的求和结点耦合,以便将电荷从第一开关电容器转移到第一求和结点。电压的电平由比较器输出上的第一开关电容器采样。如果比较器输出为逻辑“1”,则电压等于第一电平,即共模电压和参考电压之和。如果比较器输出为逻辑“0”,则电压等于第二电平,即共模电压与参考电压之差。

[0056]

在实施例中,第一开关网络包括各自耦合到第一开关电容器的第一端子的可控共模电压开关和可控参考电压开关、耦合到第一开关电容器的第二端子的可控接地开关、以及耦合在第一开关电容器的第二端子与求和结点之间的可控积分器输入开关。

[0057]

图3是根据实施例的开关网络300的示意图。提供了提供共模电压301的电压源、提供参考电压302的电压源、可控共模电压开关303、可控参考电压开关304和可控接地开关305。可控共模电压开关303和可控参考电压开关304连接到第一开关电容器307的第一端子

306。可控共模电压开关303使得第一端子306能够连接到共模电压源301,并且可控参考电压开关304使得第一端子306能够连接到参考电压源302。可控接地开关305使得第一开关电容器的第二端子308能够连接到地309。可控共模电压开关和可控参考电压开关使得能够对第一开关电容器307充电。第一开关网络还包括可控积分器输入开关310,其使得第一开关电容器的第二端子能够连接到第一开关网络的输出311。

[0058]

图4是示出图2的实施例的操作步骤的流程图。这些步骤由控制器205响应于比较器判定以及由转换器时钟204提供的第一和第二定时信号来控制。在第一定时信号401之后,如果比较器判定402处于逻辑电平“1”405,则将采样电压设置404为等于共模电压和参考电压之和。如果比较器判定402处于逻辑电平“0”403,则将采样电压设置406为等于共模电压与参考电压之差。对电压进行采样407,并且对第一开关电容器充电。在接收到第二定时信号408时,第一开关电容器耦合409到求和结点。这导致电荷转储到第一反馈电容器上。

[0059]

图5(a)和5(b)是分别示出在第一时钟阶段500和第二时钟阶段501期间的图3的实施例的第一开关网络的示意图。在图5(a)中,可控共模电压开关303、可控参考电压开关304和可控接地开关305被示出为闭合,以使得能够对第一开关电容器充电。可控积分器输入开关310断开。在图5(b)中,可控共模电压开关303、可控参考电压开关304和可控接地开关305断开,并且可控积分器输入开关310闭合,以将开关电容器与积分器电路的求和结点耦合。在第二阶段期间,将开关电容器耦合到求和结点导致电荷转储到积分器电路的反馈电容器上。电荷转储可以处于两个电平,一个对应于第一电压电平,并且第二个对应于第二电压电平。电压电平以及因此电荷转储的电平由前一时钟周期的比较器判定来控制。在实施例中,第一电压电平等于共模电压与参考电压之和,并且第二电压电平等于共模电压与参考电压之差。该布置实现混合电压和电流输入,其中传感器输入连续地连接到积分器电路。在包括第一和第二阶段的时钟周期期间,来自传感器的电流在第一反馈电容器上累积。

[0060]

在实施例中,δ-σ转换器是两级设备。与单级设备相比,两级δ-σ转换器能够实现增加的噪声降低,并因此改善信噪比。除了单级设备的特征之外,两级转换器通常还具有第二积分器、第二反馈电容器、反馈电路和用于将该设备耦合到第一级的耦合电路。第二级接收来自第一级的输入并向比较器提供输出。

[0061]

图6是根据实施例的具有两级σ-δ转换器的传感器电路的示意图。图6中所示的实施例包括图2的实施例的特征,以及另外的第二级601。提供了耦合在第一积分器207和比较器211之间的第二积分器602。第二积分器602包括在第二积分器输入604处的第二求和结点603、第二反馈电容器605和第二积分器输出606。第二积分器输入604耦合到第一积分器输出210,并且第二积分器输出606耦合到第一比较器输入219。在实施例中,第二积分器被配置为反相放大器,其中负端子是第二积分器输入,并且正端子处于诸如共模电压的参考电压。在实施例中,提供了耦合开关网络607以连接δ-σ转换器的第一级和第二级。在实施例中,提供了具有第二开关电容器609的第二开关电路608,以为第二级积分器提供反馈电路。

[0062]

图7是根据实施例的耦合开关网络700的示意图。耦合开关网络包括第一输入701,其耦合到第一积分器输出210。第一耦合开关702经由第一输入701耦合第一积分器输出并且耦合耦合电容器704的第一端子703。第二耦合开关705耦合耦合电容器704的第一端子703和共模电压源706。第三耦合开关707将耦合电容器704的第二端子708耦合到共模电压

源709。第四耦合开关710将耦合电容器704的第二端子708耦合到耦合网络的输出711,耦合网络的输出711耦合到第二积分器输入604。

[0063]

图8是第二开关网络800的示意图。该网络包括第一输入801、第二输入802、第二可控公共电压开关803、第二可控参考开关804、具有第一端子806和第二端子808的第二开关电容器807、连接到地809的第二可控接地开关805、连接到输出811的第二可控输出开关810。第一输入801连接到共模电压源,第二输入802连接到参考电压源,并且第二开关网络的输出811耦合到第二积分器的求和结点。

[0064]

在实施例中,定时引擎在每个时钟周期中提供四个定时信号。图9(a)是定时引擎901的布置的图。时钟信号902被接收,并且定时引擎901被配置为依次提供四个定时信号,即定义第一时钟阶段的第一阶段定时信号(φ1)903、第一另外的阶段定时信号(φ

1d

)904、定义第二时钟阶段的第二阶段定时信号(φ2)905和控制第一耦合开关的第二另外的阶段定时信号(φ

2d

)906。

[0065]

图9(b)是根据实施例的由图9(a)的定时引擎输出的时钟信号的图。该图示出了四个输出信号903、904、905、906,其中第一另外的定时信号904是第一定时信号903的略微延迟的版本。第一定时信号比第一另外的定时信号超前第一延迟907。第二定时信号与第一定时信号近似反相,但是在第一定时信号的下降沿和第二定时信号的上升沿之间存在第二延迟908。第二另外的定时信号比第二定时信号滞后第三延迟909。第二另外的定时信号的下降沿比第一时间输入信号的上升沿超前第四延迟910。因此,在实施方式中,φ

1d

和φ

2d

是φ1和φ2的延迟时钟,并且第一和第二阶段定时信号如图所示不重叠(即,φ1、φ

1d

不重叠φ2、φ

2d

)。可以改变相应定时信号的相对定时,并且本发明不限于任何一个特定的定时序列。

[0066]

定时信号和分别控制第一开关电路的阶段。定时信号启动第一阶段,其中在第一开关电路中对电压进行采样,并且根据比较器输出使用两个电压电平之一对第一开关电容器充电。定时信号启动第二阶段,其中第一开关电容器连接到第一积分器的求和结点,并且发生电荷转储到第一反馈电容器上。

[0067]

在操作中,耦合开关网络和第二开关网络由定时信号控制。第一耦合开关702由第二另外的定时信号(φ

2d

)控制。第二耦合开关705由第一另外的定时信号(φ

1d

)控制。第三耦合开关707由第一信号(φ1)控制。第四耦合开关710由第二定时信号(φ2)控制。

[0068]

在实施例中,定时信号和还控制第二开关网络。在实施例中,切换的定时与第一开关网络的顺序相反。第二网络被配置为使得第一定时信号控制第二可控输出开关810的操作,并且第二定时信号控制第二可控接地开关805的操作。

[0069]

图10是根据实施例的锁存电路的示意图。锁存电路包括锁存电路输入1001、第一触发器1002、第二触发器1003、第一与门1004、第二与门1005、第三与门1006、第四与门1007、第一输出1028、第二输出1029、第三输出1030和第四输出1031。还有分别连接到与门的输入的四个定时信号输入1016、1018、1020、1022(分别用于φ

2d

、φ

2d

、φ

1d

、φ

1d

)。分别链接到第一和第二与门的输入的第一定时信号输入1016和第二定时信号输入1018接收来自第二另外的定时信号的信号。分别链接到第三和第四与门的输入的第三定时信号输入1020和第四定时信号输入1022接收来自第一另外的定时信号的信号。第一触发器1002具有连接到锁存电路的输入1001的第一输入1008,锁存电路的输入1001接收用于比较器的输出的输入。第一触发器的第二输入1009接收来自第二定时信号的信号。第二触发器也从锁存电路

1001的输入接收第一输入1012和从第一定时信号接收第二触发器的第二输入1013。第一触发器的第一输出1010和第二输出1011分别输出到第一和第二与门的第二输入。第二触发器的第一输出1014和第二输出1015分别提供给第三和第四与门的第二输入。第一与门1024的输出连接到锁存电路的第一输出1028。第二与门1025的输出连接到锁存电路的第二输出1029。第三与门1026的输出连接到锁存电路的第三输出1030。第四与门1027的输出连接到锁存电路的第四输出1031。在实施例中,第一输出1028和第三输出1030连接到可控参考电压开关304的控制端子,并且第二输出1029和第四输出1031连接到共模电压开关305的控制端子。

[0070]

在实施例中,第一输出1028和第三输出1030另外连接到第二可控参考开关804的控制端子,并且第二输出1029和第四输出1031另外连接到共模电压开关305的控制端子。在实施例中,第二输出1029和第四输出1031另外连接到第二耦合开关705和第三耦合开关707。

[0071]

图11是示出锁存电路的定时输入、中间信号和输出的时序图。输入包括由定时引擎从时钟信号1101导出的第一定时信号1102和第二定时信号1103。两个中间信号1104、1105分别是第一触发器和第二触发器的第一输出。四个输出信号1106、1107、1108、1109分别输出到第一锁存器输出1028、第二锁存器输出1029、第三锁存器输出1030和第四锁存器输出1031。这些输出提供共模电压和基准电压的控制信号。

[0072]

图12a是根据实施例的传感器电路。该实施例包括根据图3的实施例的第一开关网络1201、根据图8的实施例的第一级积分器1202、光电二极管1203、第二开关网络1204。积分器1202可具备经配置以连接积分器输入的可控自动归零开关az。根据图7的实施例,传感器电路可以包括耦合网络1205。传感器电路还可以包括例如根据图10的实施例的第二级积分器1206、比较器1207和锁存电路1208。锁存电路1208可以包括逻辑块1215,逻辑块1215组合图10中所示的信号以例如通过或运算向第一开关网络1201提供控制信号p_v

ref

、v_v

cm

。系统由时钟和定时引擎1209控制,例如如图9(a)所示。抽取器1210或其他滤波器可以用于对例如从电路的比较器输出(q)导出的数字输出进行滤波,以提供多位(例如,16位)数字输出1216,其是模拟输入信号的数字化版本。替代地,从比较器输出导出的数字信号可以用作数字输出信号而无需进一步滤波。在实施例中,抽取器1210包括三阶抽取器。在实施例中,可以通过选择第二开关电容器和第二反馈电容器的相对电容来实现增益。电容的典型比率是1:4,但是本发明不限于任何给定比率和随后的增益值。如图所示,翻转开关可用于减少开关引起的误差。这已经显示出实现了50%更好的性能。

[0073]

在实施例中,增益可编程性通过vref、和tclk来实现,而不是在反馈电容器中引入可编程性(该方法将在信号路径中具有更多开关,因此易于产生更多开关引起的误差)。通过过采样可以进一步降低噪声。根据实施例的架构可以实现相同的噪声性能,而与给定增益设置的光输入无关。与传统的异步光-数字转换器相比,根据实施例的架构可以实现非常低噪声的性能。

[0074]

在实施例中,输出码可以被截断为16位。因此,数字输出码(code)可以由以下等式给出:

[0075]

[0076]

其中iphoto是光电二极管电流,tclk是σ-δ操作的频率,4*c

s1

是反馈电容器,并且vref是参考电压。其他截断也是可能的,并且本发明不限于任何一种编码方案。

[0077]

图12b示出了根据实施例的替代传感器电路;与图12(a)的元件相同的元件由相同的附图标记表示。在替代传感器电路中,不是使用根据图3的实施例的第一开关网络1201,而是第一开关网络1201和第二开关网络1204中的一个或两个包括分别用于v

cm

和v

ref

中的每一个的一对开关。这些开关可以分别由信号qb.φ

1d

、q.φ

2d

和q.φ

1d

、qb.φ

2d

控制,其中q表示(同步的)比较器输出(并且)。

[0078]

附图标记列表:

[0079]

100

ꢀꢀ

环境光传感器系统的示意图

[0080]

101

ꢀꢀ

光电二极管

[0081]

101a 光电二极管电流

[0082]

102

ꢀꢀ

运算放大器

[0083]

103

ꢀꢀ

积分电容器

[0084]

104

ꢀꢀ

开关参考电路

[0085]

105

ꢀꢀ

比较器

[0086]

106

ꢀꢀ

控制逻辑

[0087]

107

ꢀꢀ

数字输出

[0088]

108

ꢀꢀ

微调信号

[0089]

200

ꢀꢀ

传感器电路的示意图

[0090]

201

ꢀꢀ

传感器输入

[0091]

202

ꢀꢀ

δ-σ模数转换器

[0092]

203

ꢀꢀ

第一开关网络

[0093]

204

ꢀꢀ

转换器时钟

[0094]

205

ꢀꢀ

控制器

[0095]

206

ꢀꢀ

光电二极管

[0096]

207

ꢀꢀ

第一积分器

[0097]

208

ꢀꢀ

第一反馈电容器

[0098]

209

ꢀꢀ

第一积分器输入

[0099]

210

ꢀꢀ

第一积分器输出

[0100]

211

ꢀꢀ

比较器

[0101]

212

ꢀꢀ

第一求和结点

[0102]

213

ꢀꢀ

第一开关电容器

[0103]

215

ꢀꢀ

共模电压源

[0104]

216

ꢀꢀ

参考电压源

[0105]

217

ꢀꢀ

第一定时信号

[0106]

218

ꢀꢀ

第二定时信号

[0107]

219

ꢀꢀ

第一比较器输入

[0108]

220

ꢀꢀ

第二比较器输入

[0109]

221

ꢀꢀ

比较器输出

[0110]

300

ꢀꢀ

开关网络

[0111]

301

ꢀꢀ

共模电压

[0112]

302

ꢀꢀ

参考电压

[0113]

303

ꢀꢀ

可控共模电压开关

[0114]

304

ꢀꢀ

可控参考电压开关

[0115]

305

ꢀꢀ

可控接地开关

[0116]

306

ꢀꢀ

第一开关电容器的第一端子

[0117]

307

ꢀꢀ

第一开关电容器

[0118]

308

ꢀꢀ

第一开关电容器的第二端子

[0119]

309

ꢀꢀ

地

[0120]

310

ꢀꢀ

可控积分器输入开关

[0121]

311

ꢀꢀ

第一开关网络的输出

[0122]

401

ꢀꢀ

第一定时信号

[0123]

402

ꢀꢀ

比较器判定

[0124]

403

ꢀꢀ

比较器判定逻辑电平“0”[0125]

404

ꢀꢀ

采样电压设置为vcm-vref

[0126]

405

ꢀꢀ

比较器判定逻辑电平“1”[0127]

406

ꢀꢀ

采样电压设置为vcm+vref

[0128]

407

ꢀꢀ

电压采样

[0129]

408

ꢀꢀ

接收到第二定时信号

[0130]

409

ꢀꢀ

将第一开关电容器的第二端子耦合到求和结点

[0131]

500

ꢀꢀ

第一时钟阶段

[0132]

501

ꢀꢀ

第二时钟阶段

[0133]

601

ꢀꢀ

第二级

[0134]

602

ꢀꢀ

第二积分器

[0135]

603

ꢀꢀ

第二求和结点

[0136]

604

ꢀꢀ

第二积分器输入

[0137]

605

ꢀꢀ

第二反馈电容器

[0138]

606

ꢀꢀ

第二积分器输出

[0139]

607

ꢀꢀ

耦合开关网络

[0140]

608

ꢀꢀ

第二开关电路

[0141]

609

ꢀꢀ

第二开关电容器

[0142]

700

ꢀꢀ

耦合开关网络

[0143]

701

ꢀꢀ

第一输入

[0144]

702

ꢀꢀ

第一耦合开关

[0145]

703

ꢀꢀ

耦合电容器的第一端子

[0146]

704

ꢀꢀ

耦合电容器

[0147]

705

ꢀꢀ

第二耦合开关

[0148]

706

ꢀꢀ

共模电压源

[0149]

707

ꢀꢀ

第三耦合开关第四耦合开关

[0150]

708

ꢀꢀ

耦合电容器的第二端子

[0151]

709

ꢀꢀ

共模电压源

[0152]

710

ꢀꢀ

第四耦合开关

[0153]

711

ꢀꢀ

耦合网络的输出

[0154]

800

ꢀꢀ

第二开关网络

[0155]

801

ꢀꢀ

第一输入

[0156]

802

ꢀꢀ

第二输入

[0157]

803

ꢀꢀ

第二可控公共电压开关

[0158]

804

ꢀꢀ

第二可控参考开关

[0159]

805

ꢀꢀ

第二可控接地开关

[0160]

806

ꢀꢀ

第一端子

[0161]

807

ꢀꢀ

第二开关电容器

[0162]

808

ꢀꢀ

第二端子

[0163]

809

ꢀꢀ

地

[0164]

810

ꢀꢀ

第二可控输出开关

[0165]

811

ꢀꢀ

输出

[0166]

901

ꢀꢀ

定时引擎

[0167]

902

ꢀꢀ

时钟信号

[0168]

903

ꢀꢀ

第一阶段定时信号

[0169]

904

ꢀꢀ

第一另外的阶段定时信号

[0170]

905

ꢀꢀ

第二阶段定时信号

[0171]

906

ꢀꢀ

第二另外的阶段定时信号

[0172]

907

ꢀꢀ

第一延迟

[0173]

908

ꢀꢀ

第二延迟

[0174]

909

ꢀꢀ

第三延迟

[0175]

910

ꢀꢀ

第四延迟

[0176]

1001 锁存电路输入

[0177]

1002 第一触发器

[0178]

1003 第二触发器

[0179]

1004 第一与门

[0180]

1005 第二与门

[0181]

1006 第三与门

[0182]

1007 第四与门

[0183]

1008 第一输出

[0184]

1009 第一触发器的第二输入

[0185]

1010 第一触发器的第一输出

[0186]

1011 第一触发器的第二输出

[0187]

1012 第二触发器的第一输入

[0188]

1013 第二触发器的第二输入

[0189]

1014 第二触发器的第一输出

[0190]

1015 第二触发器的第二输出

[0191]

1016 定时信号输入

[0192]

1018 定时信号输入

[0193]

1020 定时信号输入

[0194]

1022 定时信号输入

[0195]

1024 第一与门的输出

[0196]

1025 第二与门的输出

[0197]

1026 第三与门的输出

[0198]

1027 第四与门的输出

[0199]

1028 锁存电路的第一输出

[0200]

1029 锁存电路的第二输出

[0201]

1030 锁存电路的第二输出

[0202]

1031 锁存电路的第二输出

[0203]

1201 第一开关网络

[0204]

1202 第一级积分器

[0205]

1203 光电二极管

[0206]

1204 第二开关网络

[0207]

1205 耦合网络

[0208]

1206 第二级积分器

[0209]

1207 比较器

[0210]

1208 锁存电路

[0211]

1209 定时引擎

[0212]

1210 抽取器

[0213]

1215 逻辑块

[0214]

1216 数字输出

[0215]

在本文中例如在实施例中已经组合描述或描绘的电路和方法的特征可以单独实现或以子组合实现。可以组合来自不同实施例的特征。因此,本说明书中公开或示出的每个特征可以单独地或以与本文公开或示出的任何其他特征的任何适当组合并入本发明中。除非特别说明,否则方法步骤不应被视为需要特定顺序,例如描述或描绘它们的顺序。

[0216]

已经根据实施例描述了方法和系统的各方面,但是这些实施例仅是说明性的,并且权利要求不限于那些实施例。本领域技术人员将能够鉴于本公开进行修改和替代,这些修改和替代被认为落入权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1