基于自适应Kalman滤波器的全数字锁相环低噪声数字鉴相器

基于自适应kalman滤波器的全数字锁相环低噪声数字鉴相器

技术领域

1.本发明涉及的是一种数字信号处理领域的技术,具体是一种应用自适应kalman滤波器优化全数字锁相环中数字鉴相器的噪声的设计。

背景技术:

2.在全数字锁相环架构下,锁相环输出的相位噪声一般来自时间数字转换器(tdc)的量化噪声,数控振荡器(dco)的量化噪声及参考信号的相位噪声。其中tdc的量化噪声源自tdc的延迟单元的延迟时间不能无限小,即其时间分辨率有限所导致。针对此量化噪声,会选择时间分辨率较高的tdc,即使用延迟单元的延迟时间较小的tdc以优化噪声;dco的量化噪声则源自决定振荡频率的控制电容的电容值在数字输入下不能连续变化,即频率分辨率有限所导致。针对此量化噪声,一般会使用最小电容较小的先进工艺制造dco;为了实现亚分辨率载波综合,常常会利用积分

‑

微分调制器(delta

‑

sigma modulator,dsm)以提高dco的输出频率分辨率。在环路设计中,则会在锁定阶段换用窄通带的iir低通滤波器以过滤环路中处于高频的各种噪声,从而提供较好的噪声性能。

技术实现要素:

3.本发明针对现有技术存在的上述不足,提出一种基于自适应kalman滤波器的全数字锁相环低噪声数字鉴相器,针对全数字锁相环各噪声源进行了噪声优化,利用自适应kalman滤波器对鉴相过程中的tdc的量化噪声及dco的量化噪声进行优化,从而减小鉴相结果中的噪声成分,进而优化环路的噪声性能。

4.本发明是通过以下技术方案实现的:

5.本发明涉及一种基于自适应kalman滤波器的应用于多段调节式的全数字锁相环的低噪声数字鉴相器,包括:基于相位累加器的多段调节全数字锁相环以及设置于多段调节全数字锁相环内的用于降低噪声的自适应kalman滤波器,其中:自适应kalman滤波器的输入端分别接收上一周期的dco控制字(otw)及当前周期测量到的dco输出信号的相位信息,利用量化噪声的估计信息进行滤波,从而得到优化的dco输出信号的相位信息。

6.所述的量化噪声的估计信息包括:e(q(n)v

*

(k))=0,e(v(n))=0,(k))=0,e(v(n))=0,e(q(n))=0,其中:q(n)为dco的量化噪声,v(n)为tdc的量化噪声,f

ckv

为通过环路中的周期估计环节获得的dco输出信号的瞬时频率,tdc的量化噪声的方差通过理论得到较好的估计;dco的量化噪声在kalman滤波器内通过自适应调节获得。

7.所述的dco的增益即为参考频率,即k

dco

=f

r

,dco输出信号的相位与otw之间满足:

8.所述的dco输出信号的相位信息,即当前周期的相位观测值其中:为理想相位信息,v(n)为量化噪声。技术效果

9.本发明整体解决了现有数字鉴相器的精度输出,受限于延迟单元的缺陷;与现有技术相比,本发明利用自适应滤波器技术成功降低了全数字锁相环内的鉴相器噪声,降低了对鉴相器精度的要求。在测试例中降低了鉴相器噪声约16db。

附图说明

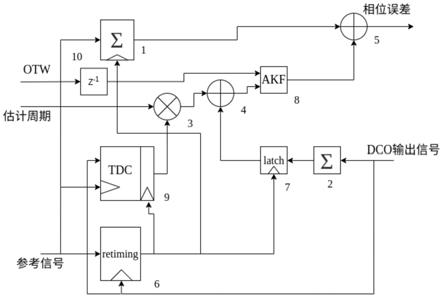

10.图1为本发明结构示意图;

11.图中:可变相位累加器1、固定相位累加器2、乘法器3、加法器4、5、重定时单元6、锁存器7、自适应卡尔曼滤波器8、时间数字转换器9、延迟单元10;

12.图2为kalman滤波器示意图;

13.图3为实施例采用与未采用自适应kalman滤波器的鉴相器输出信号的噪声比较;

14.图4为实施例采用与未采用自适应kalman滤波器的鉴相器输出信号的噪声方差比较,采用自适应kalman滤波器后输出噪声的方差降低了约16db。

具体实施方式

15.如图1所示,为本实施例涉及的一种基于kalman滤波器设计的数字鉴相器,包括:可变相位累加器1、固定相位累加器2、乘法器3、加法器4、5、重定时单元6、锁存器7、自适应卡尔曼滤波器8、时间数字转换器9和延迟单元10,其中:可变相位累加器和固定相位累加器分别接收参考信号与dco输出信号并累加两者的相位信息,数字时间转换器接收参考信号与dco输出信号并输出二者的绝对相位差,经与估计周期通过第一乘法器3相除后得到归一化相位差,再与dco输出信号的归一化相位相加后得到当前周期的相位观测值kalman滤波器分别接收经延迟单元11的上一周期的otw控制字以及当前周期测量到的dco输出信号的相位信息,利用量化噪声的估计信息进行滤波,从而得到优化的dco输出信号的相位信息。

1.如图2所示,所述的kalman滤波器包括:六个运算单元f1、p1、p2、k1、i1、h1和三个延迟单元12、13、14,其中:第一运算单元f1根据第二延迟单元13输出的otw生成相位的后验预测,即其中:为相位的后验预测,为相位信息的前验预测,otw为振荡器控制字;第二运算单元p1根据第一延迟单元12输出的dco量化噪声的方差和第二延迟单元13输出的otw生成真实值与前验预测值之间的误差的协方差,即其中:为真实值与前验预测值之间的误差的协方差,为真实值与后验预测值之间的误差的协方差,e(q(n)q

*

(n))为dco量化噪声的方差q;第三运算单元k1根据真实值与前验预测值之间的误差的协方差和dco噪声的方差生成kalman滤波器的增益,即其中:k

k

(n)为kalman滤波器的增益,e(v(n)v

*

(n))为dco噪声的方差。即r;第四运算单元h1根据相位的前验预测、kalman滤波器的增益和相位信息的观测值生成相位的后验预测,即其中:为相位信息的观测值,即图中的第五运算单元p2根据真实值与前验预测值之间的误差的协方差以及kalman滤波器的增益生成真实值与后验预测值之间的误差的协方差,即

第六运算单元i1根据真实值与前验预测值之间的误差的协方差以及后验预测与前验预测的差生成dco量化噪声的方差估计值,即化噪声的方差估计值,即

2.ν(n)为观测值与前验预测的差,此序列被称为innovation sequence;δφ(i)为后验预测与前验预测的差;

3.如图3和图4所示,为数字鉴相器的相位信息输出比较,图3为采用与未采用自适应kalman滤波器的鉴相器输出信号的噪声比较。图4采用与未采用自适应kalman滤波器的鉴相器输出信号的噪声方差比较。

4.经过具体实际实验,通过上述锁相环环路结构及鉴相器结构,以时间数字转换器精度为10ns参数运行,采用了自适应kalman滤波器的鉴相器输出的量化噪声方差较未使用自适应kalman滤波器的鉴相器输出的量化噪声方差减小了约16db.。

5.与现有技术相比,本发明减小了全数字锁相环中鉴相器输出噪声的能量,从而提升了环路整体噪声性能。

6.上述具体实施可由本领域技术人员在不背离本发明原理和宗旨的前提下以不同的方式对其进行局部调整,本发明的保护范围以权利要求书为准且不由上述具体实施所限,在其范围内的各个实现方案均受本发明之约束。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1