基于RFSoC的FIR滤波器系统及滤波方法

基于rfsoc的fir滤波器系统及滤波方法

技术领域

1.本公开涉及滤波器技术领域,尤其涉及一种基于rfsoc的fir滤波器系统及滤波方法,适用于射电天文、无线通信等高速数字信号处理。

背景技术:

2.在通讯领域,2018年面向5g无线通讯和雷达信号处理推出了第一代rfsoc(radio frequency system on chip,片上射频系统)技术。rfsoc在soc(system on chip,系统级芯片)架构中集成了射频信号转换器和软判决前向纠错(sd

‑

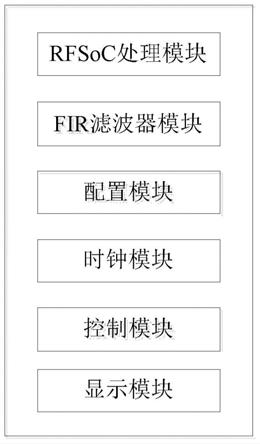

fec),配有对应的处理单元和可编程逻辑器件。单个芯片中集成了fpga、arm cpu、adc/dac、10/40/100gb网络等多种资源,实现16通道2gsps

‑

12bit或8通道4gsps

‑

12bit采样,芯片集成度高、性能强大,已成为高速信号处理未来的发展趋势。

3.fir(finite impulse response,有限脉冲响应)滤波器是信号处理系统中最基本的元件,是一种非递归型滤波器。fir滤波器可以做到严格的线性相移,系统性能始终非常稳定,其单位冲击响应有限长的,可以设计满足特殊频率特性形状要求的数字滤波器,例如高通、低通及带通滤波器等。fir滤波器在通信、模式识别、图像处理、射电天文等领域都有着广泛的应用。然而随着数字技术的迅速发展,现有技术无法用于高性能领域。一般在数字信号处理中采用dsp或fpga实现fir滤波器,但是灵活性及扩展性较差,并且和rfsoc技术相比,系统功耗及体积大、信号处理速度慢等缺点。目前5g通信或高速射频领域要求高性能、高可靠性及稳定性,通用的dsp、fpga等技术实现fir滤波器系统,不能满足实际应用需求。

技术实现要素:

4.(一)要解决的技术问题

5.基于上述问题,本公开提供了一种基于rfsoc的fir滤波器系统及滤波方法,以缓解现有技术中fir tap数较高时,在实际应用中数据处理速度慢、滤波器配置模式不灵活、扩展性差、功耗高等技术问题。

6.(二)技术方案

7.本公开的一个方面,提供一种基于rfsoc的fir滤波器系统,包括:rfsoc处理模块,用于传输数据及发送控制指令;fir滤波器模块,用于在可编程逻辑器件中执行fir滤波器算法,实现数字滤波器;配置模块,用于实时对所述fir滤波模块进行配置;时钟模块,用于提供时钟信号;控制模块,用于调用ip软核控制fir滤波器系统的运行;以及显示模块,用于读取并显示fir滤波器处理的结果。

8.根据本公开实施例,所述rfsoc处理模块,包括:arm a53处理芯片,在sd卡中安装的pynq操作系统下运行。

9.根据本公开实施例,通过可编程逻辑器件zynq ultrascale mpsoc ip配置arm a53处理芯片,开通需要的端口,通过axi接口的master hp0及slave hpm0接口传输数据及发送控制指令。

10.根据本公开实施例,所述配置模块通过dma对所述fir滤波器模块进行配置。

11.根据本公开实施例,所述配置模块通过dma对所述fir滤波器模块进行配置,包括:选择fir滤波器的类型,以及将所述fir滤波器的系数从外面传进到可编程逻辑器件。

12.根据本公开实施例,所述fir滤波器可选择为低通滤波器、高通滤波器或带通滤波器中任意一种。

13.根据本公开实施例,所述可编程逻辑器件执行的数字滤波器算法的计算公式为:

[0014][0015]

其中,h(k)为滤波器的系数,r(n

‑

k)为经过k延迟单元的参考信号,n表示序号,n表示滤波器长度。

[0016]

根据本公开实施例,所述fir滤波器模块的传输函数h(z)表示成:

[0017][0018]

根据本公开实施例,通过采用pynq overlay类加载vivado生成的二进制bit文件,调用vivado中的ip软核,控制fir滤波器模块。

[0019]

本公开的另一方面,一种基于rfsoc的fir滤波器系统的滤波方法,包括:通过rfsoc处理模块传输数据及发送控制指令;通过fir滤波器模块在可编程逻辑器件中执行fir滤波器算法,实现数字滤波器;实时对所述fir滤波模块进行配置;通过时钟模块提供时钟信号;通过调用ip软核控制fir滤波器系统的运行;以及通过显示模块读取并显示fir滤波器处理的结果。

[0020]

(三)有益效果

[0021]

从上述技术方案可以看出,本公开基于rfsoc的fir滤波器系统及滤波方法至少具有以下有益效果其中之一或其中一部分:

[0022]

(1)功耗低、集成度高、速度快、低延迟等优势,高速实现多阶fir滤波器,能够满足射频信号的实时滤波需求;

[0023]

(2)采用了ip核的集成设计方式,很大程度上简化了数字滤波器设计架构,滤波器性能稳定及可靠;

[0024]

(3)fir滤波器的配置方式非常灵活,通过脚本程序的修改实现低通、高通及带通等多种fir数字滤波器;

[0025]

(4)fir滤波器通过对应程序控制及显示处理结果,以网页的形式打开,可以在网页页面中直接编写代码和运行代码,代码的运行结果也会直接在代码块下显示。

附图说明

[0026]

图1为本公开实施例的基于rfsoc的fir滤波器系统组成示意图。

[0027]

图2为本公开实施例的基于rfsoc的fir滤波器系统的工作原理框架示意图。

[0028]

图3为本公开实施例的fir滤波器的输入信号的类型示意图。

[0029]

图4为本公开实施例的fir滤波器的输入信号经滤波处理后的结果示意图。

[0030]

图5为本公开实施例的基于rfsoc的fir滤波器系统的输入信号频域示意图。

[0031]

图6为本公开实施例的基于rfsoc的fir滤波器系统的输出信号频域示意图。

[0032]

图7为本公开实施例的基于rfsoc的fir滤波器系统的滤波方法的流程图。

具体实施方式

[0033]

本公开提供了一种基于rfsoc的fir滤波器系统及滤波方法,采用第一代ultrascale+rfsoc芯片xczu28dr实现高速数字滤波器,通过软件配置实现低通滤波器、高通滤波器及带通滤波器等多种数字滤波器。fir数字滤波器的滤波频段根据实际应用需求可调,灵活性及扩展性好。

[0034]

为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。

[0035]

在本公开实施例中,提供一种基于rfsoc的fir滤波器系统,结合图1和图2所示,所述基于rfsoc的fir滤波器系统,包括:

[0036]

rfsoc处理模块,用于传输数据及发送控制指令;

[0037]

fir滤波器模块,能够在可编程器件中执行fir滤波器算法,实现数字滤波器;

[0038]

配置模块,能够对所述fir滤波模块进行配置;

[0039]

时钟模块,用于提供时钟信号;

[0040]

控制模块,用于控制fir滤波器的运行;以及

[0041]

显示模块,用于读取并显示fir滤波器处理的结果。

[0042]

根据本公开实施例,数据处理模块为rfsoc处理模块,rfsoc芯片包含arm coretexa53处理器,它运行在sd卡中安装的pynq操作系统,通过zynq ultrascale mpsoc ip配置arm处理器,开通需要的端口,利用axi接口的master hp0及slave hpm0接口传输数据及发送相关模块的控制指令。

[0043]

根据本公开实施例,fir滤波器模块,在可编程(pl)器件中执行fir滤波器算法,高速实现数字滤波器。pl执行的fir滤波器算法的计算公式为:

[0044][0045]

上式中,h(k)为滤波器的系数,r(n

‑

k)为经过k延迟单元的参考信号,n为滤波器长度,n为序号,r与r(n

‑

k)同为参考信号,k为延迟。fir滤波器模块的传输函数h(z)可表示成:

[0046][0047]

根据本公开实施例,滤波器配置模块,通过dma(direct memory access,直接存储器访问)对fir滤波器进行配置,选择fir滤波器的类型,例如低通滤波器、高通滤波器及带通滤波器等,将fir滤波器的系数从外面传进到可编程逻辑器件。

[0048]

根据本公开实施例,时钟模块,对fpga提供时钟信号,保证系统指令和相关任务正确执行。

[0049]

根据本公开实施例,滤波器控制模块,采用pynq overlay类加载vivado生成的二进制bit文件,调用vivado中设计的ip(intellectual property)软核,控制fir滤波器系统。

[0050]

根据本公开实施例,显示模块,利用axi dma读取数据,显示fir滤波器处理的结果。以网页的形式打开,在网页页面中直接编写和运行python脚本程序,代码的运行结果也会直接在浏览器的代码块下显示。

[0051]

根据本公开实施例,采用zcu111 rfsoc电路板进行实验,rfsoc通过sd卡模式启动,采用pynq操作系统。

[0052]

根据本公开实施例,fir滤波器的输入信号是由3个正弦波组成,频率分别为0.2mhz、12mhz及48mhz,滤波器的输入信号如下图3所示。

[0053]

根据本公开实施例,在zcu111上设计fir低通滤波器,滤掉信号的高频部分后,处理结果如图4中细实线所示,可以看到,信号通过滤波器之后,显示低频正弦波。

[0054]

根据本公开实施例,图5、图6是frfsoc fir滤波器的输入和输出信号频域表示,图中可以看到信号通过低通滤波器之后,将信号的高频部分滤掉,只保留信号的低频部分。

[0055]

根据本公开实施例,还可以通过修改python脚本程序,实现高通及带通滤波器。

[0056]

本公开还提供一种基于rfsoc的fir滤波器系统的滤波方法,通过上述滤波器系统进行滤波,如图7所示,该滤波方法包括:

[0057]

操作s1:通过rfsoc处理模块传输数据及发送控制指令;

[0058]

操作s2:通过fir滤波器模块在可编程逻辑器件中执行fir滤波器算法,实现数字滤波器;

[0059]

操作s3:实时对所述fir滤波模块进行配置;

[0060]

操作s4:通过时钟模块提供时钟信号;

[0061]

操作s5:通过调用ip软核控制fir滤波器系统的运行;以及

[0062]

操作s6:通过显示模块读取并显示fir滤波器处理的结果。

[0063]

至此,已经结合附图对本公开实施例进行了详细描述。需要说明的是,在附图或说明书正文中,未绘示或描述的实现方式,均为所属技术领域中普通技术人员所知的形式,并未进行详细说明。此外,上述对各元件和方法的定义并不仅限于实施例中提到的各种具体结构、形状或方式,本领域普通技术人员可对其进行简单地更改或替换。

[0064]

依据以上描述,本领域技术人员应当对本公开基于rfsoc的fir滤波器系统及滤波方法有了清楚的认识。

[0065]

综上所述,本公开提供了一种基于rfsoc的fir滤波器系统及滤波方法,采用了xilinx公司的推出的全球首款rfsoc芯片,功耗低、集成度高、速度快、低延迟等优势,高速实现多阶fir滤波器,能够满足射频信号的实时滤波需求。采用了ip核的集成设计方式,很大程度上简化了数字滤波器设计架构,使用xilinx提供的标准vivado ip核设计,滤波器性能稳定及可靠。fir滤波器的配置方式非常灵活,通过python脚本程序的修改实现低通、高通及带通等多种fir数字滤波器。fir滤波器通过jupyter notebook控制及显示处理结果,以网页的形式打开,可以在网页页面中直接编写代码和运行代码,代码的运行结果也会直接在代码块下显不。

[0066]

还需要说明的是,实施例中提到的方向用语,例如“上”、“下”、“前”、“后”、“左”、“右”等,仅是参考附图的方向,并非用来限制本公开的保护范围。贯穿附图,相同的元素由相同或相近的附图标记来表示。在可能导致对本公开的理解造成混淆时,将省略常规结构或构造。

[0067]

并且图中各部件的形状和尺寸不反映真实大小和比例,而仅示意本公开实施例的内容。另外,在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。

[0068]

再者,单词“包含”不排除存在未列在权利要求中的元件或步骤。位于元件之前的单词“一”或“一个”不排除存在多个这样的元件。

[0069]

说明书与权利要求中所使用的序数例如“第一”、“第二”、“第三”等的用词,以修饰相应的元件,其本身并不意味着该元件有任何的序数,也不代表某一元件与另一元件的顺序、或是制造方法上的顺序,该些序数的使用仅用来使具有某命名的一元件得以和另一具有相同命名的元件能做出清楚区分。

[0070]

此外,除非特别描述或必须依序发生的步骤,上述步骤的顺序并无限制于以上所列,且可根据所需设计而变化或重新安排。并且上述实施例可基于设计及可靠度的考虑,彼此混合搭配使用或与其他实施例混合搭配使用,即不同实施例中的技术特征可以自由组合形成更多的实施例。

[0071]

本领域那些技术人员可以理解,可以对实施例中的设备中的模块进行自适应性地改变并且把它们设置在与该实施例不同的一个或多个设备中。可以把实施例中的模块或单元或组件组合成一个模块或单元或组件,以及此外可以把它们分成多个子模块或子单元或子组件。除了这样的特征和/或过程或者单元中的至少一些是相互排斥之外,可以采用任何组合对本说明书(包括伴随的权利要求、摘要和附图)中公开的所有特征以及如此公开的任何方法或者设备的所有过程或单元进行组合。除非另外明确陈述,本说明书(包括伴随的权利要求、摘要和附图)中公开的每个特征可以由提供相同、等同或相似目的的替代特征来代替。并且,在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。

[0072]

以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1