振荡器频率的快速数字校准方法与流程

1.本发明属于锁相环芯片的设计技术技领域,具体涉及振荡器频率的快速数字校准方法。

背景技术:

2.随着无线通信技术和半导体技术的日益进步,无线通信芯片的设计要求也越来越高。在射频及微波等通信领域,用于产生本地振荡器(lo)的锁相环(pll)经常需要快速切换到不同的输出信道频率上。通信技术标准的日趋提高,要求锁相环的频率切换时间越来越短。锁相环中压控或数控振荡器(vco或dco)用数字控制的二进制(binary)或亚二进制(sub

‑

binary)电容阵列来调节频率。锁相环的频率切换时间通常由两部分组成:即开环的振荡器频率数字粗糙校准(digital coarse tuning),加上闭环后振荡器频率模拟控制电压精细调整(analog fine tuning)的锁相过程。由于振荡器经常使用超过10位的数字校准(digital calibration),而且校准精度又通常超过千分之一,其频率的数字校准通常需要很长的时间才能完成。

3.最常用的振荡器频率数字校准方法,是在一定的时间内通过计数振荡器的周期数目来实现的。既有的方法主要用固定的精度和时间来完成每一位控制数字的校准。假如每位数字校准需要3微秒,总共13位数字则需要约40微秒才能完成数字校准。在跳频无线射频通信(如蓝牙)或时分通信(如gsm和td

‑

scdma)应用中,锁相环频率综合器的频率切换时间要求很短。因此,缩短振荡器频率的数字校准时间非常关键。

技术实现要素:

4.本发明的目的在于提供振荡器频率的快速数字校准方法,从最高位到最低位数字的逐位频率校准过程中,采用可变的时间步长来显著地减少校准时间,满足锁相环更短的频率切换时间要求,以解决上述背景技术中提出的问题。

5.为实现上述目的,本发明提供如下技术方案:振荡器频率的快速数字校准方法,该方法包括:对振荡器的每个数字位进行频率校准过程中,采用可变的时间步长来减少校准时间。

6.优选地,所述每个数字位所需的校准时间大致上和频率差成反比例。

7.优选地,所述每个数字位的校准过程中,频率差越大,校准时间越短,最短为一个参考时钟周期。

8.优选地,所述振荡器的频率校准从最高数字位到最低数字位的顺序进行。

9.优选地,所述时间步长由振荡器的频率校准所需的精度决定。

10.优选地,所述当振荡器的数字位如果经过最大时间步长进行校准,其周期计数值与目标值的差仍然小于一个由校准精度决定的误差值,则表明当前的数字位即是最终的校准值,可以提前结束校准。

11.优选地,所述振荡器校准后的最大频率误差是传统二进制搜索法校准的一半。

12.与现有技术相比,本发明的有益效果是:

13.(1)本发明完全消除了传统的振荡器频率数字校准中的冗余时间。

14.(2)本发明将校准时间缩短至传统方法的大约1/3以下。

15.(3)本发明将传统二进制搜索法校准后的最大频率误差减小了一半。

16.(4)本发明保持了振荡器频率数字校准的简单性和可靠性。

17.(5)本发明可广泛应用于锁相环频率综合器中。

附图说明

18.图1是传统的振荡器频率数字校准流程;

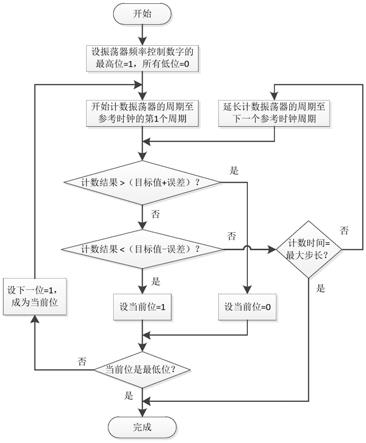

19.图2是本发明的振荡器频率数字校准流程;

20.图3是本发明的振荡器频率数字校准时间与传统方法的比较;

21.图4是本发明的振荡器频率数字校准后的归一化频率误差;

22.图5是基于锁相环的频率综合器;

23.图6是振荡器中的开关电容阵列示意图。

24.图7是振荡器频率校准可变步长计数功能模块图。

具体实施方式

25.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

26.传统的校准流程如图1所示;传统的振荡器频率数字校准方法使用固定的时间步长进行每一位的数字校准,而时间步长是由最终的频率校准精度决定的,从最高位到最低位,采用二进制的搜索(binary search)算法。

27.如图2所示,本发明实施例提供了振荡器频率的快速数字校准方法,该方法包括:对振荡器的每个数字位进行频率校准过程中,采用可变的时间步长来减少校准时间。从最高位数字(msb)开始的频率校准过程中,由于在校准的每一步振荡器的频率与最终的目标频率可能相差很大,采用可变的时间步长会显著地减少校准时间。同时,采用本发明的校准方法,可以将校准后的最大频率误差减小一半。

28.作为本发明的一个实施方式,所述每个数字位所需的校准时间大致上和频率差成反比例。

29.作为本发明的一个实施方式,所述每个数字位的校准过程中,频率差越大,校准时间越短,最短校准时间为一个参考时钟周期。

30.作为本发明的一个实施方式,所述振荡器的频率校准从最高数字位到最低数字位的顺序进行。

31.作为本发明的一个实施方式,所述最大时间步长由振荡器频率校准的精度决定。

32.作为本发明的一个实施方式,所述当振荡器的某个数字位如果经过最大时间步长进行校准,其周期计数值与目标值的差仍然小于一个由校准精度决定的误差值,则表明当前的数字位即是最终的校准值,可以提前结束校准。

33.作为本发明的一个实施方式,所述振荡器校准后的最大频率误差是传统二进制搜

索法校准的一半。

34.为了说明本发明的有效性,用仿真比较本发明和传统方法的振荡器校准时间。设数字最低位对应的频率步长(δf

lsb

)与最大时间步长时的频率计数误差的比例为r

ferr

,r

ferr

取典型值2或3。图3为本发明的校准时间与传统方法校准时间的比例分布,由图3可见,这个时间比例分布从最小值约10%到最大值约1/3。可见,本发明显著地减少了振荡器频率的数字校准时间。

35.图3中的时间比例分布比较特别,为了进一步验证本发明的正确性和有效性,图4给出了经过本发明的数字频率校准后频率误差的分布;这里频率误差被归一化到δf

lsb

。当r

ferr

=2时,本发明的校准后频率误差范围为

±

0.75

·

δf

lsb

;当r

ferr

=3时,本发明的校准后频率误差为范围

±

0.667

·

δf

lsb

。作为比较,对应这两个r

ferr

值用传统二进制搜索法校准后的频率误差范围分别为(

‑

1.5~0.5)

·

δf

lsb

和(

‑

1.333~0.333)

·

δf

lsb

。由此可见,本发明的校准与传统方法相比,校准后的最大误差减小了一半。

36.图5所示为基于锁相环的频率综合器,由相频检测器,电荷泵,环路滤波器,压控振荡器,可编程环路分频器,及振荡器频率数字校准等模块组成。锁相环输入参考频率为fref,环路分频比为n,则pll的vco输出频率为fosc=n

·

fref。

37.图6所示为振荡器中开关电容阵列的示意图;图中n位(n是正整数)电容阵列,由c<n

‑

1>,c<n

‑

2>,

…

,c<1>和c<0>组成。设整数i且1≤i≤n

‑

1,则电容阵列值满足c<i>≤2

×

c<i

‑

1>。n位电容阵列c<n

‑

1:0>的开关控制为n位数字d<n

‑

1:0>。设整数j且0≤j≤n

‑

1,当数字d<j>=0(低电位)时,电容c<j>对应的开关合上;否则d<j>=1(高电位)时,开关断开。c

fixed

为不受开关影响的固定电容值,则lc振荡器的总体电容值为所以,lc振荡器频率为可见,开关合上时c

total

增大,fosc减小。

38.图7为振荡器频率校准可变步长计数功能模块图;在每个数字位的校准过程中,同时对振荡器和参考时钟进行计数,其计数值分别为整数mosc和mref;因为振荡器频率数字校准的目标值为fosc=n

·

fref,所以经校准后,mosc和n

·

mref的差在一个由校准精度决定的误差范围(

±

δm)内即可达到目的;其中,可变步长计数意味着振荡器的技术时间不是传统方法中的最大步长时间,而是在达到最大步长时间之前每经过一个参考时钟周期都进行判断。

39.如图2的本发明频率校准流程所示,计数值比较有三种结果:如果mosc≥n

·

mref+δm,则认为fosc高于目标值;如果mosc≤n

·

mref

‑

δm,则认为fosc低于目标值;否则n

·

mref

‑

δm<mosc<n

·

mref+δm,则不能断定fosc是高于还是低于目标值;在上述的第三种比较结果下,如果振荡器的计数时间没有达到最大值,则继续计数以进行下一次数值比较;否则,认为当前的所有频率校准数字位就是最终校准结果,而提前结束校准。

40.正如图3仿真结果所示,本发明的可变步长快速振荡器频率数字校准方法,校准时间最多只有传统固定步长校准方法的大约1/3,显著地减少了校准时间。

41.正如图4仿真结果所示,本发明的可变步长快速振荡器频率数字校准方法,校准后的最大频率误差只有传统固定步长校准方法的1/2,将校准精度提高了1倍。

42.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1