三维存储器元件的形成方法与流程

1.本发明是有关于一种半导体元件的形成方法,且特别是有关于一种三维存储器元件的形成方法。

背景技术:

2.非易失性存储器(例如快闪存储器)由于具有使存入的数据在断电后也不会消失的优点,因此成为个人电脑和其他电子设备所广泛采用的一种存储器。

3.目前业界较常使用的三维快闪存储器包括或非门(nor)快闪存储器以及与非门(nand)快闪存储器。此外,另一种三维快闪存储器为与门(and)快闪存储器,其可应用在多维度的快闪存储器阵列中而具有高集成度与高面积利用率,且具有操作速度快的优点。因此,三维快闪存储器的发展已逐渐成为目前的趋势。

4.公开内容

5.本发明提供一种三维存储器元件的形成方法,包括以下步骤。提供具有第一区与第二区的缓冲层。第二区环绕第一区。在缓冲层上形成停止层与包括交替堆叠的多个介电层与多个牺牲层堆叠结构。堆叠结构包括至少一垂直通道结构,以贯穿第一区中的堆叠结构。在第一区的堆叠结构中形成第一开口,且在第二区的堆叠结构中形成第二开口。第二开口的宽度大于第一开口的宽度。形成介电材料,以填入第一开口与第二开口。进行第一蚀刻工艺,至少移除第二开口的底面上的部分介电材料,以暴露出停止层的一部分,进而在第一开口中形成第一介电层并在第二开口的侧壁上形成第二介电层。进行第二蚀刻工艺,以移除外露于第二开口的底面处的停止层,进而形成空腔。空腔侧向延伸至堆叠结构的下方,使得空腔连接第二开口以形成封闭环。

6.本发明提供一种三维存储器元件的形成方法,包括以下步骤。在缓冲层上形成放电层(discharging layer)与包括交替堆叠的多个介电层与多个牺牲层的堆叠结构。在堆叠结构中形成多个垂直通道结构。在堆叠结构中形成开口。开口包括沿着x方向延伸的两个第一狭缝与沿着y方向延伸的两个第二狭缝,且两个第一狭缝与两个第二狭缝彼此分隔。在开口的侧壁上形成绝缘层。绝缘层暴露出开口的底面处的放电层。移除外露于开口的底面处的放电层,以形成空腔。空腔延伸至堆叠结构的下方,以连接两个第一狭缝与两个第二狭缝,进而形成环状开口。进行栅极替换工艺,以将堆叠结构中的多个牺牲层替换为多个导体层。多个导体层分别环绕多个垂直通道结构以形成多个存储单元。将隔离材料填入环状开口中,以形成隔离环结构。

7.基于上述,本实施例在阵列区与隔离环区中同时形成第一开口与第二开口,以通过第一开口与第二开口来进行栅极替换工艺。第二开口可包括未封闭的狭缝环结构,以避免放电层被第二开口截断,进而防止电弧效应的产生。另外,本实施例可进行后续蚀刻工艺,移除外露于第二开口的底面处的放电层,进而形成空腔。此空腔可侧向贯穿未封闭的狭缝环结构,以形成环状开口,进而电性分隔或物理分隔阵列区的放电层与外部区的放电层。在此情况下,本实施例可在切割放电层时,同时避免了电弧效应的产生,进而改善三维存储

器元件的可靠度。

附图说明

8.图1是依照本发明一实施例的一种三维存储器元件的剖面示意图。

9.图2a、图3a以及图4a绘示出依照本发明各种实施例的垂直通道结构的剖面示意图。

10.图2b、图3b以及图4b分别是图2a、图3a以及图4a的平面示意图。

11.图5是依照本发明一实施例的一种三维存储器元件的平面示意图。

12.图6a、图7a、图8a、图9a、图10a、图11a、图12a以及图13a是沿着图5的a-a切线的制造流程的剖面示意图。

13.图6b、图7b、图8b、图9b、图10b、图11b、图12b以及图13b是沿着图5的b-b切线的制造流程的剖面示意图。

14.图9c是图9a与图9b的结构的平面示意图。

15.图14是依照本发明另一实施例的一种三维存储器元件的平面示意图。

16.图15是依照本发明替代实施例的一种三维存储器元件的平面示意图。

17.附图标记说明

18.10:第一开口

19.12:第三沟道

20.20:第二开口

21.20bt:底面

22.22:第一沟道

23.23:断口

24.24:第二沟道

25.25:凹部开口

26.26:连接点

27.30:空腔

28.40:环状开口

29.100:缓冲层

30.102:停止层

31.110、210:堆叠结构

32.112:介电层

33.114:牺牲层

34.115:开口

35.116:顶盖层

36.120:介电材料

37.120a:第一材料

38.120b:第二材料

39.130、130a、130b、130c:垂直通道结构

40.132:电荷存储结构

41.133:第一源极/漏极柱

42.134:通道层

43.135:第二源极/漏极柱

44.136:介电材料

45.140:第一介电层

46.140a、150a:第一材料层

47.140b、150b:第二材料层

48.150:第二介电层

49.154:导体层

50.160、160a:填充材料

51.170:隔离材料

52.180:隔离环结构

53.234:通道结构

54.234a:衬层

55.234b:插塞

56.236:介电柱

57.334:通道柱

58.mr:存储单元区

59.r1:第一区

60.r2:第二区

61.r3:第三区

62.w1、w2、w3:宽度

63.x、y:方向

具体实施方式

64.参照本实施例的图式以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。图式中的层与区域的厚度会为了清楚起见而放大。相同或相似的元件标号表示相同或相似的元件,以下段落将不再一一赘述。

65.图1是依照本发明一实施例的一种三维存储器元件的剖面示意图。

66.请参照图1,本发明实施例的三维存储器元件可包括缓冲层100、停止层102、堆叠结构110、顶盖层116以及垂直通道结构130。在一实施例中,缓冲层100包括介电基底。介电基底可以是形成在硅基板上的介电层,例如是氧化硅层。也就是说,缓冲层100的下方可具有周边电路。另外,缓冲层100可包括第一区r1与第二区r2。在一实施例中,第一区r1可以是阵列区,而第二区r2可以是隔离环区。

67.停止层102可形成在缓冲层100上。在一实施例中,停止层102的材料包括导体材料。导体材料可包含包括有多晶硅、iii-v族化合物半导体或其组合的半导体材料。当该三维存储器元件为三维与非门(nand)快闪存储器的实施例时,此停止层102可用以当作源极线(source line)。当该三维存储器元件为三维或非门(nor)快闪存储器的实施例时,此停止层102可用以当作虚拟字线(dummy word line)。虽然图1所绘示的停止层102为单层结

构,但本发明不以此为限。在替代实施例中,停止层102亦可以是多层结构。此多层结构可包括交替堆叠的多个介电层(例如氧化硅层)与多个导体层(例如多晶硅层)。

68.堆叠结构110可形成在停止层102上,以使停止层102配置在缓冲层100与堆叠结构110之间。在一实施例中,堆叠结构110可包括交替堆叠的多个介电层112与多个牺牲层114。在一实施例中,介电层112与牺牲层114可以是不同材料,或是具有不同蚀刻率的材料。举例来说,介电层112可以是氧化硅层;牺牲层114可以是氮化硅层、多晶硅层或金属钨层。介电层112与牺牲层114的数量可以依据需求来调整,本发明不以此为限。

69.顶盖层116可形成在堆叠结构110上,以使堆叠结构110配置在停止层102与顶盖层116之间。在一实施例中,顶盖层116的材料可包括介电材料,例如是氧化硅。

70.垂直通道结构130可形成在第一区r1中的堆叠结构110与停止层102中。如图1所示,垂直通道结构130可贯穿堆叠结构110、停止层102且部分延伸至缓冲层100中。值得注意的是,在形成可容纳垂直通道结构130的开口115时,停止层102不仅可用以当作蚀刻停止层,还可用以防止在等离子体蚀刻时所产生的电弧效应(arcing effect),进而改善元件的可靠度。在此实施例中,停止层102可视为放电层(discharging layer),其通常会接地至硅基板,以降低上述等离子体蚀刻所累积的电荷,进而避免元件的损坏。因此,在进行高深宽比的蚀刻工艺时,通常会将停止层102接地至硅基板,以避免电弧放电发生。

71.基本上,根据三维存储器元件的不同形式,垂直通道结构130可具有不同情况,详细说明如下所述。

72.图2a、图3a以及图4a绘示出依照本发明各种实施例的垂直通道结构的剖面示意图。图2b、图3b以及图4b分别是图2a、图3a以及图4a的平面示意图。

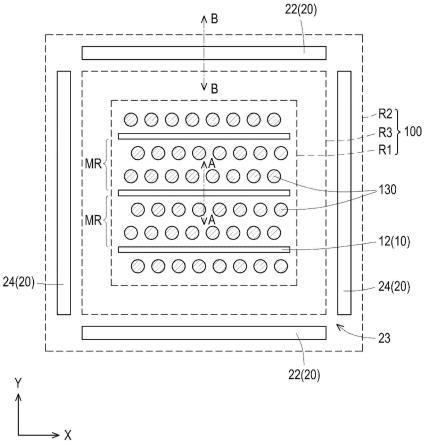

73.请参照图2a与图2b,当该三维存储器元件为三维及式(and)快闪存储器,垂直通道结构130a可包括电荷存储结构132、通道层134、介电材料136、第一源极/漏极柱133以及第二源极/漏极柱135。如图2a所示,第一源极/漏极柱133与第二源极/漏极柱135可贯穿顶盖层116、堆叠结构110以及停止层102,并部分延伸至缓冲层100中。在一实施例中,第一源极/漏极柱133与第二源极/漏极柱135可具有相同的导体材料,例如是n型掺杂(n+)多晶硅材料。介电材料136可配置在第一源极/漏极柱133与第二源极/漏极柱135之间,以分隔第一源极/漏极柱133与第二源极/漏极柱135。另外,如图2b所示,通道层134可横向环绕介电材料136、第一源极/漏极柱133以及第二源极/漏极柱135。第一源极/漏极柱133与第二源极/漏极柱135分别物理接触通道层134的一部分。电荷存储结构132可横向环绕通道层134。在一实施例中,电荷存储结构132可以是由隧穿层、电荷存储层以及阻挡层所构成的复合层。隧穿层、电荷存储层以及阻挡层可分别被视为氧化物/氮化物/氧化物(ono)。在另一实施例中,隧穿层可以是氧化物/氮化物/氧化物(ono)的复合层。在其他实施例中,阻挡层可以是氧化物/氮化物/氧化物(ono)的复合层或是其他合适的材料。通道层134可包括掺杂多晶硅层或是未掺杂多晶硅层。介电材料136可包括氧化硅、氮化硅、氮氧化硅或其组合。

74.请参照图3a与图3b,当该三维存储器元件为第一类型的三维与非门(nand)快闪存储器,垂直通道结构130b可包括电荷存储结构132、通道结构234以及介电柱236。如图3a所示,介电柱236可贯穿顶盖层116、堆叠结构110以及停止层102,并部分延伸至缓冲层100中。通道结构234可包括衬层234a与插塞234b。衬层234a可覆盖介电柱236的侧壁与底面,而插塞234b可密封介电柱236的顶面。在此情况下,通道结构234可完整包覆介电柱236的所有表

面。电荷存储结构132可配置在通道结构234与顶盖层116之间,以及通道结构234与堆叠结构110之间。通道结构234与停止层102之间的电荷存储结构132则是被移除。从剖面图3b的角度来看,电荷存储结构132可横向环绕通道结构234。电荷存储结构132、通道结构234以及介电柱236的材料分别与电荷存储结构132、通道层134以及介电材料136的材料相同,且已在上述段落详述过,于此便不再赘述。

75.请参照图4a与图4b,当该三维存储器元件为第二类型的三维与非门(nand)快闪存储器,垂直通道结构130c可包括电荷存储结构132以及通道柱334。如图4a所示,通道柱334可贯穿顶盖层116、堆叠结构110以及停止层102,并部分延伸至缓冲层100中。电荷存储结构132可配置在通道柱334与顶盖层116之间、通道柱334与堆叠结构110之间以及通道柱334与停止层102之间。从剖面图4b的角度来看,电荷存储结构132可横向环绕通道柱334。通道柱334与停止层102之间的电荷存储结构132则是被移除。通道柱334直接接触停止层102。电荷存储结构132与通道柱334的材料分别与电荷存储结构132与通道层134的材料相同,且已在上述段落详述过,于此便不再赘述。

76.图5是依照本发明一实施例的一种三维存储器元件的平面示意图。图6a、图7a、图8a、图9a、图10a、图11a、图12a以及图13a是沿着图5的a-a切线的制造流程的剖面示意图。图6b、图7b、图8b、图9b、图10b、图11b、图12b以及图13b是沿着图5的b-b切线的制造流程的剖面示意图。图14是依照本发明另一实施例的一种三维存储器元件的平面示意图。图15是依照本发明替代实施例的一种三维存储器元件的平面示意图。

77.在形成图1的垂直通道结构130之后,可进行栅极替换工艺,以将堆叠结构110中的牺牲层114替换成导体层154,如图5至图14所示。

78.首先,请参照图5,缓冲层100可包括第一区r1、第二区r2以及第三区r3。第二区r2可环绕第一区r1,且第三区r3可配置在第一区r1与第二区r2之间。在一实施例中,第一区r1可以是阵列区,第二区r2可以是隔离环区,而第三区r3可以是阶梯区。为了图面清楚起见,后续剖面图6a至图13a仅绘示出第一区r1中的a-a切线,后续剖面图6b至图13b仅绘示出第二区r2中的b-b切线,而省略了垂直通道结构130。

79.如图6a与图6b所示,在形成垂直通道结构130之后,可在第一区r1的堆叠结构100中形成第一开口10,且在第二区r2的堆叠结构100中形成第二开口20。第一开口10与第二开口20的形成方法包括:在顶盖层116上形成掩模图案118;以掩模图案118为掩模,进行等离子体蚀刻工艺以移除部分顶盖层116与部分堆叠结构110,进而暴露出停止层102的部分表面。在一实施例中,第二开口20的宽度w2大于第一开口10的宽度w1。第二开口20的宽度w2与第一开口10的宽度w1的比大于或等于2。举例来说,第一开口10的宽度w1约为100nm,而第二开口20的宽度w2约为300nm。

80.详细地说,如图5所示,第二开口20可包括沿着x方向延伸的两个第一沟道22(可称为第一狭缝)与沿着y方向延伸的两个第二沟道24(可称为第二狭缝)。第一沟道22与第二沟道24彼此分隔而不相连,从而形成未封闭的狭缝环结构。也就是说,相邻第一沟道22与第二沟道24之间具有断口23。值得注意的是,在形成第一开口10与第二开口20之后,停止层102仍可在阵列区r1之间连续延伸。具体来说,停止层102位于堆叠结构110的下方,第一开口10与第二开口20仅暴露出停止层102的部分表面,而未延伸至缓冲层100中。换言之,停止层102尚未被第一开口10以及/或第二开口20截断,因此,停止层102可在后续高深宽比的蚀刻

工艺中接地至硅基板,以避免电弧效应。另一方面,第一开口10可包括沿着x方向延伸的多个第三沟道12(可称为第三狭缝),以将多个垂直通道结构130分隔成沿着y方向排列的多个存储单元区mr。

81.虽然图5所绘示的第一沟道22以及第二沟道24为连续沟道结构或是连续狭缝结构,但本发明不以此为限。在其他实施例中,第一沟道22以及第二沟道24亦可以是不连续沟道结构或不是连续狭缝结构,如图15所示。

82.接着,请参照图7a与图7b,形成介电材料120,以填入第一开口10与第二开口20。具体来说,介电材料120包括第一材料120a与第二材料120b。第一材料120a共形覆盖第一开口10的表面且延伸覆盖顶盖层116的顶面,且第二材料120b共形覆盖第一材料120a,如图7a所示。第一材料120a亦共形覆盖第二开口20的表面且延伸覆盖顶盖层116的顶面,且第二材料120b共形覆盖第一材料120a,如图7b所示。在一实施例中,第一材料120a与牺牲层114的材料相同,而第一材料120a与第二材料120b不同。举例来说,第一材料120a与牺牲层114的材料可以是氮化硅,而第二材料120b可以是氧化硅。在本实施例中,介电材料120是以具有高侧壁阶梯覆盖的沉积方法来形成,例如化学气相沉积法(cvd)、原子层沉积法(ald)或其组合。

83.值得注意的是,在本实施例中,第一开口10的宽度w1小于第二开口20的宽度w2。因此,在形成介电材料120之后,介电材料120填满第一开口10,而未填满第二开口20。在此情况下,第二开口20上的介电材料120形成了凹部开口25。

84.请参照图7a至图8a与图7a至图8b,进行第一蚀刻工艺,移除顶盖层116(或是堆叠结构110)的顶面上与第二开口20的底面20bt上的部分介电材料120,以在第一开口10中形成第一介电层140并在第二开口20的侧壁上形成第二介电层150(可称为绝缘层)。具体来说,第一介电层140可包括第一材料层140a与第二材料层140b。第二材料层140b可贯穿顶盖层116与堆叠结构110,而第一材料层140a包覆第二材料层140b且与堆叠结构110以及停止层102接触,如图8a所示。另外,第二介电层150可包括第一材料层150a与第二材料层150b。第一材料层150a覆盖顶盖层116的侧壁与堆叠结构110的侧壁,而第二材料层150b则是配置在第一材料层150a上,如图8b所示。值得注意的是,在本实施例中,在第一介电层140密封第一开口10的同时,第二介电层150在第二开口20的底面20bt处暴露出部分停止层102。在一实施例中,第一蚀刻工艺包括全面性蚀刻工艺。在替代实施例中,第一蚀刻工艺包括干法蚀刻工艺、湿法蚀刻工艺、等向性蚀刻工艺、异向性蚀刻工艺或其组合。

85.请参照图8a至图9a与图8b至图9b,以第一介电层140与第二介电层150为掩模进行第二蚀刻工艺,以移除外露于第二开口20的底面20bt处的停止层102,进而形成空腔30。如图9b所示,空腔30横向延伸至堆叠结构110的下方,以使空腔30的宽度w3大于第二开口20的宽度w2。在一实施例中,第二蚀刻工艺包括:干法蚀刻工艺、湿法蚀刻工艺、化学干法蚀刻(cde)工艺或是氧化工艺与湿法清洗工艺的组合。举例来说,可以第一材料层140a、150a(例如氮化硅)当作蚀刻停止层进行hna系统的湿法蚀刻工艺(其包括hno3/hf/h2o2的蚀刻剂),移除第二材料层140b、150b(例如氧化硅)以及部分停止层102(例如多晶硅)。另一方面,亦可以第二材料层140b、150b(例如氧化硅)或是第一材料层140a、150a(例如氮化硅)当作蚀刻停止层来进行碱金属氢氧化物(alkali hydroxide)系统的湿法蚀刻工艺(其包括naoh或是koh的蚀刻剂),移除部分停止层102(例如多晶硅)。在此实施例中,第二材料层140b、150b

仍残留在第一开口10与第二开口20中,如图9a与图9b所示。此外,亦可使用高选择性的化学干法蚀刻(cde)工艺来移除部分停止层102。

86.值得注意的是,在进行第二蚀刻工艺之后,空腔30可连接两个第一沟道22与两个第二沟道24,以形成环状开口(或封闭环)40,如上视图9c所示。换言之,空腔30可从第一沟道22以及/或第二沟道24的端点延伸至断口23(如图5所示)处,以连接第一沟道22与第二沟道24。在此情况下,停止层102会被环状开口40截断,以使第一区r1中的停止层102与外部的停止层102电性隔离。在本实施例中,由于在形成第一开口10与第二开口20之后,没有高深宽比的蚀刻工艺需要将停止层102进行接地来避免电弧效应,因此,停止层102可在此步骤中被截断或分割,以避免相邻区域之间的相邻停止层102彼此电性连接,进而影响存储器元件的操作。此外,由于空腔30是从第一沟道22以及/或第二沟道24的端点延伸出去,因此,第一沟道22与第二沟道24的连接点26可具有弧形轮廓,如图9c所示。

87.接着,形成填充材料160。如图10a所示,填充材料160覆盖顶盖层116与第一介电层140上。另一方面,如图10b所示,填充材料160从顶盖层116的顶面上延伸至第二开口20中,且填入空腔30中。在一实施例中,填充材料160包括氧化硅、氮化硅、氮氧化硅等类似的介电材料,其用以替代被掏空的停止层102,进而支撑整个堆叠结构110。

88.请参照图10a至图11a与图10b至图11b,进行湿法蚀刻工艺,移除部分填充材料160以及第二材料层140b、150b。在此情况下,如图11a所示,第一材料层140a仍覆盖第一开口10的侧壁与底面,且第一材料层140a的外表面暴露出来。另一方面,如图11b所示,第二开口20向下延伸至填充材料160a中,且第一材料层150a的外表面与填充材料160a的外表面暴露出来。

89.请参照图11a至图12a与图11b至图12b,通过第一开口10与第二开口20进行蚀刻工艺,移除第一材料层140a、150a以及牺牲层114,以在介电层112之间形成多个空隙(未绘示)。在一实施例中,所述蚀刻工艺可以是湿法蚀刻工艺。举例来说,当第一材料层140a、150a以及牺牲层114为氮化硅时,所述蚀刻工艺可以是使用含有磷酸的蚀刻液,并将所述蚀刻液倒入第一开口10与第二开口20中,从而移除第一材料层140a、150a以及牺牲层114。由于所述蚀刻液对于第一材料层140a、150a以及牺牲层114具有高蚀刻选择性,因此,第一材料层140a、150a以及牺牲层114可被完全移除,而介电层112、停止层102以及顶盖层116未被移除或仅少量移除。

90.然后,在上述空隙中形成导体层154,由此完成了本发明的三维存储器元件。在一实施例中,导体层154的材料例如为多晶硅、非晶硅、钨(w)、钴(co)、铝(al)、硅化钨(wsi

x

)或硅化钴(cosi

x

)。此外,在形成导体层154之前,可在介电层112与导体层154之间依序形成缓冲层以及势垒层。缓冲层的材料例如为介电常数大于7的高介电常数的材料,例如氧化铝(al2o3)、氧化铪(hfo2)、氧化镧(la2o5)、过渡金属氧化物、镧系元素氧化物或其组合。势垒层的材料例如为钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)或其组合。

91.在本实施例中,三维存储器元件具有多个存储单元(未绘示)。此存储单元的数量可随着堆叠结构210中的导体层154的数量来调整,本发明不以此为限。

92.请参照图13a与图13b,在进行栅极替换工艺之后,可在第一开口10与第二开口20(或是环状开口40)中形成隔离材料170。在一实施例中,隔离材料170可与填充材料160a相同,例如是氧化硅。在此情况下,隔离材料170可与填充材料160a接触以形成隔离环结构

180,如图14与图13b所示。

93.在替代实施例中,隔离环结构180的形成方法亦可包括:形成衬层(例如氧化硅)以共形覆盖第一开口10与第二开口20(或是环状开口40)的表面;移除第一开口10与第二开口20的底面处的部分衬层;以及在第一开口10与第二开口20中形成金属层(例如w)以使金属层接触停止层102。

94.综上所述,本实施例在阵列区与隔离环区中同时形成第一开口与第二开口,以通过第一开口与第二开口来进行栅极替换工艺。第二开口可包括未封闭的狭缝环结构,以避免放电层被第二开口截断,进而防止电弧效应的产生。另外,本实施例可进行后续蚀刻工艺,移除外露于第二开口的底面处的放电层,进而形成空腔。此空腔可侧向贯穿未封闭的狭缝环结构,以形成环状开口,进而电性分隔或物理分隔阵列区的放电层与外部区的放电层。在此情况下,本实施例可在切割放电层时,同时避免了电弧效应的产生,进而改善三维存储器元件的可靠度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1