一种应用于高速数字隔离器的发送-接收电路的制作方法

1.本发明涉及数字隔离器技术领域,特别涉及一种应用于高速数字隔离器的发送-接收电路。

背景技术:

2.传统的脉冲极性调制架构,发送端中包含边沿检测电路,检测输入信号的边沿,转换成流过耦合电感初级侧的电流脉冲i

tx

,并在耦合电感次级侧产生电压脉冲v

rx

,电压脉冲v

rx

的幅值与电流脉冲i

tx

随时间的变化率成正比,即:

[0003][0004]

接收端将v

rx

转换为边沿信号,还原输入信号in。发送端边沿检测电路控制i

tx

快速上升,缓慢下降。v

rx

则表现高幅值窄脉冲信号,之后跟随一个低幅值宽反向脉冲。为避免接收端将反向脉冲误判为信号脉冲,造成解码错误,通常在接收端设值合适的门限电压,滤除反向脉冲。

[0005]

若门限电压设置过高接近信号脉冲,信号脉冲可能会无法被接收端正确识别。因此门限电压要尽可能小于信号脉冲幅值,这要求反向脉冲幅值尽可能小。然而,上述公式说明,为减小反向脉冲的幅值,必须增大i

tx

的下降时间,这会直接减小数字隔离器传输速率。

技术实现要素:

[0006]

本发明的目的在于提供一种应用于高速数字隔离器的发送-接收电路,以解决背景技术中的问题。

[0007]

为解决上述技术问题,本发明提供了一种应用于高速数字隔离器的发送-接收电路,包括发送端、片上耦合电感和接收端;其中所述片上耦合电感包括耦合电感初级侧a端、b端和耦合电感次级侧c端、d端;

[0008]

所述发送端对输入逻辑信号进行编码并产生脉冲电流驱动所述片上耦合电感的初级侧a端、b端;

[0009]

所述片上耦合电感用于信号的隔离传输,在初级侧a端、b端产生的电流脉冲可在次级侧c端、d端感应产生脉冲电压;

[0010]

所述接收端对所述片上耦合电感的次级侧c端、d端脉冲电压解码和对输入逻辑信号的恢复。

[0011]

可选的,所述发送端包括驱动电路p_drv1,p_drv2,n_drv1和n_drv2,驱动mos管mp1,mp2,mn1和mn2;所述驱动电路p_drv1,p_drv2,n_drv1和n_drv2的输入端同时接入逻辑信号in;

[0012]

所述驱动电路p_drv1的输出端与驱动pmos管mp1的栅极相连;

[0013]

所述驱动电路n_drv1的输出端与驱动nmos管mn1的栅极相连;

[0014]

所述驱动电路p_drv2的输出端与驱动pmos管mp2的栅极相连;

[0015]

所述驱动电路n_drv2的输出端与驱动nmos管mn2的栅极相连;

[0016]

驱动pmos管mp1和mp2的源极均接vdd,驱动nmos管mn1和mn2的源极均接地;pmos管mp1的漏极和nmos管mn1的漏极均接耦合电感初级侧a端;pmos管mp2的漏极和nmos管mn2的漏极均接耦合电感初级侧b端。

[0017]

可选的,所述接收端包括低噪声放大器lna1、lna2,比较器comp1、comp2和双稳态电路;

[0018]

所述低噪声放大器lna1的正相端v

in+

和所述低噪声放大器lna2的负相端均v

in-接耦合电感次级侧c端,所述低噪声放大器lna1的负相端v

in-和所述低噪声放大器lna2的正相端v

in+

均接耦合电感次级侧d端;

[0019]

所述低噪声放大器lna1的正相输出端v

o1﹢

接入所述比较器comp1的正相输入端;所述低噪声放大器lna1的负相输出端v

o1-接入所述比较器comp1的负相输入端;所述低噪声放大器lna2的正相输出端v

o2﹢

接入所述比较器comp2的正相输入端;所述低噪声放大器lna2的负相输出端v

o2-接入所述比较器comp2的负相输入端;

[0020]

所述比较器comp1和所述比较器comp2分别输出栅极控制信号v

g1

和v

g2

至所述双稳态电路。

[0021]

可选的,所述双稳态电路包括nmos管mn3和mn4、反相器inv1和inv2;其中,

[0022]

所述nmos管nm3的栅端连接栅极控制信号v

g1

,漏端接地,源端连接所述反相器inv1的输入端和所述反相器inv2的输出端;

[0023]

所述nmos管nm4的栅端连接栅极控制信号v

g2

,源端接地,漏端连接所述反相器inv2的输入端和所述反相器inv1的输出端。

[0024]

可选的,所述低噪声放大器lna1和所述低噪声放大器lna2相同,其结构均为一个电容型交叉耦合低噪声放大器,包括nmos管mn21和mn22、耦合电容c

c1

和c

c2

、源端电阻r

s1

和r

s2

、负载电阻r

l1

和r

l2

、采样电阻r

in1

和r

in2

;

[0025]

nmos管mn21的栅端通过耦合电容c

c1

与nmos管mn22的源端连接,同时所述nmos管mn21的栅端接入偏置电压va;

[0026]

nmos管mn22的栅端通过耦合电容c

c2

与nmos管mn21的源端连接,同时所述nmos管mn22的栅端接入偏置电压vb;

[0027]

源端电阻r

s1

与nmos管mn21的源端连接,同时接入输入电压v

in+

;

[0028]

源端电阻r

s2

与nmos管mn22的源端连接,同时接入输入电压v

in-;

[0029]

负载电阻r

l1

一端与nmos管mn21的漏端相连接,同时接入输出电压v

o+

,另一端接电源vcc;

[0030]

负载电阻r

l2

一端与nmos管mn22的漏端相连接,同时接入输出电压v

o-,另一端接电源vcc;

[0031]

输入采样电阻r

in1

与nmos管mn21的源端相连接,另一端与采样电阻r

in2

相连接,同时接入偏置电压vc;

[0032]

输入采样电阻r

in2

与nmos管mn22的源端相连接,另一端与采样电阻r

in1

相连接,同时接入偏置电压vc。

[0033]

在本发明提供的应用于高速数字隔离器的发送-接收电路中,包括发送端、片上耦合电感和接收端;其中所述片上耦合电感包括耦合电感初级侧a端、b端和耦合电感次级侧c

端、d端;所述发送端对输入逻辑信号进行编码并产生脉冲电流驱动所述片上耦合电感的初级侧a端、b端;所述片上耦合电感用于信号的隔离传输,在初级侧a端、b端产生的电流脉冲可在次级侧c端、d端感应产生脉冲电压;所述接收端对所述片上耦合电感的次级侧c端、d端脉冲电压解码和对输入逻辑信号的恢复。该发送-接收电路用于高速数字隔离器中,通过在接收端直接滤除幅值较大的反向脉冲,避免了延长耦合电感初级侧脉冲电流的下降时间,从而提高了数字隔离器的传输速率。

附图说明

[0034]

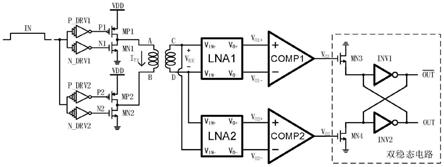

图1是本发明提供的应用于高速数字隔离器的发送-接收电路结构示意图;

[0035]

图2是本发明提供的低噪声放大器电路结构示意图;

[0036]

图3是本发明提供的应用于高速数字隔离器的发送-接收电路信号波形图。

具体实施方式

[0037]

以下结合附图和具体实施例对本发明提出的一种应用于高速数字隔离器的发送-接收电路作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0038]

本发明提供了一种应用于高速数字隔离器的发送-接收电路,其结构如图1所示,包括发送端、片上耦合电感和接收端;其中所述片上耦合电感包括耦合电感初级侧a端、b端和耦合电感次级侧c端、d端;所述发送端对输入逻辑信号进行编码并产生脉冲电流驱动所述片上耦合电感的初级侧a端、b端;所述片上耦合电感用于信号的隔离传输,在初级侧a端、b端产生的电流脉冲可在次级侧c端、d端感应产生脉冲电压;所述接收端对所述片上耦合电感的次级侧c端、d端脉冲电压解码和对输入逻辑信号的恢复。

[0039]

所述发送端包括驱动电路p_drv1,p_drv2,n_drv1和n_drv2,驱动mos管mp1,mp2,mn1和mn2;所述驱动电路p_drv1,p_drv2,n_drv1和n_drv2的输入端同时接入逻辑信号in;所述驱动电路p_drv1的输出端与驱动pmos管mp1的栅极相连;所述驱动电路n_drv1的输出端与驱动nmos管mn1的栅极相连;所述驱动电路p_drv2的输出端与驱动pmos管mp2的栅极相连;所述驱动电路n_drv2的输出端与驱动nmos管mn2的栅极相连;驱动pmos管mp1和mp2的源极均接vdd,驱动nmos管mn1和mn2的源极均接地;pmos管mp1的漏极和nmos管mn1的漏极均接耦合电感初级侧a端;pmos管mp2的漏极和nmos管mn2的漏极均接耦合电感初级侧b端。

[0040]

所述接收端包括低噪声放大器lna1、lna2,比较器comp1、comp2和双稳态电路。所述低噪声放大器lna1、lna2用于接收耦合电感次级侧c端、d端的电感电压,并输出放大的差分信号,所述比较器comp1、comp2用于比较差分信号并输出数字信号控制双稳态电路,所述双稳态电路用于输入逻辑信号的恢复。所述低噪声放大器lna1的正相端和所述低噪声放大器lna2的负相端均接耦合电感次级侧c端,所述低噪声放大器lna1的负相端和所述低噪声放大器lna2的正相端均接耦合电感次级侧d端;所述低噪声放大器lna1的正相输出端v

o1﹢

接入所述比较器comp1的正相输入端;所述低噪声放大器lna1的负相输出端v

o1-接入所述比较器comp1的负相输入端;所述低噪声放大器lna2的正相输出端v

o2﹢

接入所述比较器comp2的正相输入端;所述低噪声放大器lna2的负相输出端v

o2-接入所述比较器comp2的负相输入

端;所述比较器comp1和所述比较器comp2分别输出栅极控制信号v

g1

和v

g2

至所述双稳态电路。

[0041]

所述双稳态电路包括nmos管mn3和mn4、反相器inv1和inv2;其中,所述nmos管nm3的栅端连接栅极控制信号v

g1

,漏端接地,源端连接所述反相器inv1的输入端和所述反相器inv2的输出端;所述nmos管nm4的栅端连接栅极控制信号v

g2

,源端接地,漏端连接所述反相器inv2的输入端和所述反相器inv1的输出端。

[0042]

请继续参阅图1,在所述发送端,所述驱动电路p_drv1,p_drv2,n_drv1和n_drv2对输入的逻辑信号in进行整形,输出栅极驱动信号p1,n1,p2,n2,分别驱动所述驱动mos管mp1,mn1,mp2,mn2。当逻辑信号in由低变高时,栅极驱动信号p1,n1变低,栅极驱动信号p2,n2变高,驱动mos管mp1,mn2导通,驱动mos管mp2,mn1截止。在mos管切换瞬间,所述片上耦合电感的初级侧a端、b端电流i

tx

极性翻转,由a端流向b端,此时片上耦合电感的次级侧c端、d端产生上脉冲v

rx+

。当逻辑信号in由高变低时,驱动mos管mp1,nm2关闭,驱动mos管mn1,mp2打开,电流i

tx

极性变为由b端流向a端,片上耦合电感的次级侧c端、d端产生下脉冲v

rx-。

[0043]

所述接收端由低噪声放大器lna1,lna2,比较器comp1,comp2和双稳态电路组成,v

rx﹢

同时输入低噪声放大器lna1的正相端v

in+

和低噪声放大器lna2的负相端v

in-,v

rx-同时输入低噪声放大器lna1的负相端v

in-和低噪声放大器lna2的正相端v

in+

,低噪声放大器lna1输出差分信号v

o1﹢

和v

o1-至所述比较器comp1,经比较后得到栅极控制信号v

g1

,控制所述双稳态电路中nmos管mn3的栅极;低噪声放大器lna2输出差分信号v

o2﹢

和v

o2-至所述比较器comp2,经比较后得到栅极控制信号v

g2

,控制所述双稳态电路中nmos管mn4的栅极。

[0044]

经所述低噪声放大器lna1,低噪声放大器lna2放大和电平转换后输出差分信号v

o1﹢

和v

o1-,v

o2﹢

和v

o2-;v

o1+

和v

o1-的直流电平相差v

od

,v

o2+

和v

o2-的直流电平相差v

od

。调节v

od

小于信号脉冲幅值且大于反向脉冲幅值。即可达到滤除反向脉冲的目的。所述低噪声放大器滤除反向脉冲的原理定量分析请继续参阅图2。

[0045]

所述低噪声放大器lna1和所述低噪声放大器lna2相同,其结构均为一个电容型交叉耦合低噪声放大器,为对称结构,包括nmos管mn21和mn22、耦合电容c

c1

和c

c2

、源端电阻r

s1

和r

s2

、负载电阻r

l1

和r

l2

、采样电阻r

in1

和r

in2

;nmos管mn21的栅端通过耦合电容c

c1

与nmos管mn22的源端连接,同时所述nmos管mn21的栅端接入偏置电压va;nmos管mn22的栅端通过耦合电容c

c2

与nmos管mn21的源端连接,同时所述nmos管mn22的栅端接入偏置电压vb;源端电阻r

s1

与nmos管mn21的源端连接,同时接入输入电压v

in+

;源端电阻r

s2

与nmos管mn22的源端连接,同时接入输入电压v

in-;负载电阻r

l1

一端与nmos管mn21的漏端相连接,同时接入输出电压v

o+

,另一端接电源vcc;负载电阻r

l2

一端与nmos管mn22的漏端相连接,同时接入输出电压v

o-,另一端接电源vcc;输入采样电阻r

in1

与nmos管mn21的源端相连接,另一端与采样电阻r

in2

相连接,同时接入偏置电压vc;输入采样电阻r

in2

与nmos管mn22的源端相连接,另一端与采样电阻r

in1

相连接,同时接入偏置电压vc。

[0046]

电压vc设置输入直流电平,设计采样电阻r

in1

,r

in2

为高阻以检测输入电压v

rx+

和v

rx-。va,vb为mn21,mn22的栅极偏置电压,va,vb设置一定差值,可实现差分输出电压v

o+

,v

o-的直流电平存在一定压差v

od

,调节v

od

小于信号脉冲幅值且大于反向脉冲幅值,即可在保留信号脉冲的同时滤除反向脉冲。证明公式如下:

[0047][0048]

其中,μn为n沟道mos管的电子迁移率,c

ox

为栅氧化层电容,va为mn21栅极偏置电压,vb为mn22栅极偏置电压,vc为输入直流电平,v

thn

为nmos阈值电压,又因:

[0049]va-vb≠0

[0050]

设置:

[0051]va

>v

c-v

thn

[0052]vb

>v

c-v

thn

[0053]

即可保证:

[0054]vod

≠0

[0055]

所述双稳态电路包括nmos管mn3,mn4,反相器inv1,inv2。所述双稳态电路具有三种输出状态:状态一、当栅极控制信号v

g1

,v

g2

同时为低电平时,反相器inv1,inv2输入端同时为高阻态,输出信号out维持原状态;状态二、当栅极控制信号v

g1

为高电平,栅极控制信号v

g2

为低电平时,输出信号out置零;状态三、当栅极控制信号v

g1

为低电平,栅极控制信号v

g2

为高电平时,输出信号out置高,信号波形图如图3所示。

[0056]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1