极化码编码方法和装置、译码方法和装置、编译码系统与流程

本公开涉及编码译码,特别涉及一种极化码编码方法和装置、极化码译码方法和装置、极化码编译码系统。

背景技术:

1、相关技术提出一种极化码的基于子段独立并行的crc(cyclic redundancycheck,循环冗余校验)辅助scl(successive-cancellation list,列表连续删除)译码方法,将待译码极化码分为等长的多个子段,各子段进行独立scl译码,然后对各子段通过校验选择的译码路径(设为a比特空间)进行子段变换处理得到极化码的译码输出结果(设为v比特空间)。其中,各子段进行独立scl译码后,利用crc校验码进行子段校验,子段校验后,如果只有一条备选路径通过校验,则通过校验的备选路径为子段scl译码输出;如果多条备选路径通过校验,则选择通过校验的备选路径中出现概率最大的备选路径为子段scl译码输出;如果没有备选路径通过校验,则以出现概率最大的备选路径为子段scl译码输出,或者启动重发机制。显然,选择出现概率最大的备选路径作为子段scl译码输出,并不一定就是正确输出,仍然存在错误子段的可能。

2、经研究发现,在基于整个比特序列的crc辅助的scl译码中,按照出现概率选择译码输出是可行的。但是,在基于子段并行的crc辅助scl译码中,由于a→v子段变换具有错误比特放大作用,一旦子段选择错误,错误比特数量会被成倍数放大。

技术实现思路

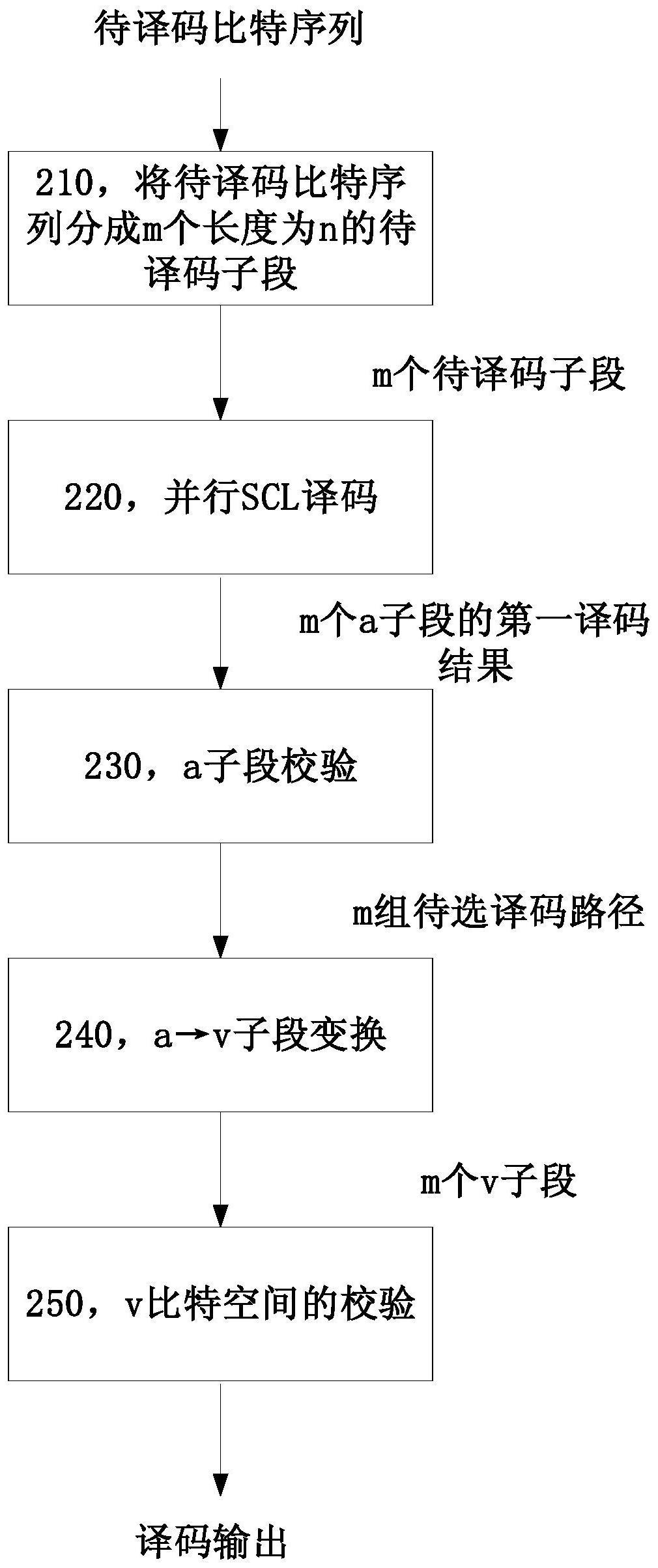

1、本公开实施例提出基于a和v比特空间双重校验辅助的scl译码方法,a比特空间执行并行子段校验辅助scl译码,在从多条待选译码路径中选择译码路径时,由v比特空间的校验码辅助选择出译码路径,避免由于选择了错误的译码路径,经子段变换的错误比特放大作用,所导致的译码性能大幅度下降,提高译码性能。

2、本公开一些实施例提出一种极化码译码方法,包括:

3、将接收的长度为n的待译码比特序列分成m个长度为n的待译码子段,n、m、n为2的整次幂;

4、对m个所述待译码子段分别独立地进行列表连续删除scl译码,得到m个a子段的第一译码结果,每个a子段的第一译码结果有l条备选路径;

5、根据a子段中的校验码,对m个a子段的l条备选路径分别进行a子段校验,筛选出m组待选译码路径,每组待选译码路径包括至少一条待选译码路径;

6、m组待选译码路径中由各组的一条待选译码路径组成的每个路径组合,分别经过a→v子段变换,分别得到m个待校验的v子段;

7、根据v比特空间的校验码,对由m个待校验的v子段组成的v比特序列进行v比特空间的校验,筛选出通过校验的v比特序列作为译码输出。

8、在一些实施例中,译码侧的a→v子段变换和编码侧的b→w子段变换具有相同的变换形式。

9、在一些实施例中,a→v子段变换通过异或运算实现子段变换。

10、在一些实施例中,根据a子段中的校验码,对m个a子段的l条备选路径分别进行a子段校验,筛选出m组待选译码路径,包括:对m个a子段的l条备选路径分别进行a子段校验,通过校验的备选路径为待选译码路径,如果a子段没有备选路径通过校验,则a子段的l条备选路径都为待选译码路径。

11、在一些实施例中,译码侧的a子段校验采用与编码侧的第一校验码生成运算相应的校验方法;译码侧的v比特空间的校验采用与编码侧的第二校验码生成运算相应的校验方法。

12、在一些实施例中,译码侧采用与编码侧相同的比特序列划分方法,将接收的长度为n的待译码比特序列分成m个长度为n的待译码子段。

13、本公开一些实施例提出一种极化码编码方法,包括:

14、将包含初始校验码的长度为n的第一待编码比特序列分成m个w比特空间的长度为n的第一w子段,n和m为2的整次幂,n=n/m;

15、对m个第一w子段进行w→b子段变换得到m个b比特空间的b子段;

16、对m个b子段进行第一校验码生成运算得到m个b子段的校验码;

17、m个b子段的校验码经过b→w子段变换后和m个第一w子段分别组合得到m个w比特空间的第二w子段,译码侧的a→v子段变换和编码侧的b→w子段变换具有相同的变换形式;

18、对m个第二w子段组成的w比特序列进行第二校验码生成运算得到w比特序列的校验码;

19、w比特序列的校验码和w比特序列合并起来得到第二待编码比特序列;

20、对所述第二待编码比特序列进行极化码编码得到编码比特序列并进行传输。

21、在一些实施例中,w→b子段变换和b→w子段变换通过异或运算实现子段变换;b→w子段变换是w→b子段变换的逆变换。

22、在一些实施例中,第一校验码生成运算或第二校验码生成运算包括循环冗余校验码生成运算,奇偶校验码生成运算,或者循环冗余校验码结合奇偶校验码生成运算。

23、在一些实施例中,初始校验码比特为0。

24、在一些实施例中,m个b子段的校验码进行b→w子段变换后和m个第一w子段分别组合得到m个w比特空间的第二w子段包括:每个b子段的校验码进行b→w子段变换后,替换所述b子段相应的第一w子段中的初始校验码,得到一个第二w子段。

25、本公开一些实施例提出一种极化码译码装置,包括:存储器;以及,耦接至所述存储器的处理器,所述处理器被配置为基于存储在所述存储器中的指令,执行极化码译码方法。

26、本公开一些实施例提出一种极化码编码装置,包括:存储器;以及,耦接至所述存储器的处理器,所述处理器被配置为基于存储在所述存储器中的指令,执行极化码编码方法。

27、本公开一些实施例提出一种极化码编译码系统,包括:极化码译码装置以及极化码编码装置。

28、本公开一些实施例提出一种非瞬时性计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现极化码译码方法或/和极化码编码方法的步骤。

技术特征:

1.一种极化码译码方法,包括:

2.根据权利要求1所述的方法,其特征在于,译码侧的a→v子段变换和编码侧的b→w子段变换具有相同的变换形式;

3.根据权利要求1所述的方法,其特征在于,根据a子段中的校验码,对m个a子段的l条备选路径分别进行a子段校验,筛选出m组待选译码路径,包括:

4.根据权利要求1所述的方法,其特征在于,

5.根据权利要求1所述的方法,其特征在于,

6.一种极化码编码方法,包括:

7.根据权利要求6所述的方法,其特征在于,

8.根据权利要求6所述的方法,其特征在于,

9.根据权利要求6所述的方法,其特征在于,初始校验码比特为0。

10.根据权利要求6所述的方法,其特征在于,m个b子段的校验码进行b→w子段变换后和m个第一w子段分别组合得到m个w比特空间的第二w子段包括:

11.一种极化码译码装置,包括:

12.一种极化码编码装置,包括:

13.一种极化码编译码系统,包括:权利要求11所述的极化码译码装置以及权利要求12所述的极化码编码装置。

14.一种非瞬时性计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现权利要求1-5中任一项所述的极化码译码方法或/和权利要求6-10中任一项所述的极化码编码方法的步骤。

技术总结

本公开提出一种极化码编码方法和装置、译码方法和装置、编译码系统,涉及编码译码领域。本公开提出基于a和v比特空间双重校验辅助的SCL译码方法,a比特空间执行并行子段校验辅助SCL译码,在从多条待选译码路径中选择译码路径时,由v比特空间的校验码辅助选择出译码路径,避免由于选择了错误的译码路径,经子段变换的错误比特放大作用所导致的译码性能大幅度下降,提高译码性能。

技术研发人员:庄永昌

受保护的技术使用者:中国电信股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!