信号输入电路、信号输入电路模块以及电路结构的制作方法

1.本实用新型涉及一种信号输入电路、信号输入电路模块以及电路结构,尤其涉及一种降低电源需求的信号输入电路、信号输入电路模块以及电路结构。

背景技术:

2.传统影像传感器(cmos image sensor)包括有两个阶段(level)的电压,一个是重置电压(vrst),一个是信号电压(vsig)。当信号电压降低而光感测强度增高时,重置电压则是保持稳定。因此影像传感器的共模电压则会随着光强度而改变。过去的技术是使用一个全差分可规划增益放大器(fully-differential pga)来解决这个问题。但是全差分可规划增益放大器则会带来噪声以及更多的电源需求。

3.因此,如何提供一种低电源需求的信号输入电路,是业界的一个重要课题。

技术实现要素:

4.本实用新型所要解决的技术问题在于,针对现有技术的不足提供一种信号输入电路,用于提供一第一信号以及一第二信号给一第一电路,所述第一电路包括一第一信号输入端以及一第二信号输入端,所述信号输入电路包括:一第一输入端,连接所述第一信号输入端,接收一重置电压;一第一电容,包括一第一端以及一第二端,所述第一电容的所述第二端电性连接所述第一输入端以及所述第一信号输入端;一第二输入端,连接所述第一电容的所述第一端,所述第二输入端接收一信号电压;一第三输入端,连接所述第一电容的所述第一端,所述第三输入端接收一共模信号电压,其中,所述信号电压与所述共模信号电压不同时提供至所述第一电容的所述第一端;一第四输入端,连接所述第一电路的第二信号输入端,接收所述信号电压;一第二电容,包括一第一端以及一第二端,所述第二电容的所述第一端连接所述第四输入端;一第五输入端,连接所述第二电容的所述第二端,所述第五输入端接收所述重置电压;以及一第六输入端,连接所述第二电容的所述第二端,所述第六输入端接收所述共模信号电压,其中,所述重置电压与所述共模信号电压不同时提供至所述第二电容的所述第二端。

5.优选地,所述第一输入端、所述第二输入端、所述第四输入端以及所述第五输入端是根据一第一频率信号而动作,所述第三输入端以及所述第六输入端是根据一第二频率信号而动作。

6.优选地,还包括:一第一开关,设置在所述第一输入端与所述第一信号输入端之间,根据所述第一频率信号开启或是关闭;一第二开关,设置在所述第二输入端与所述第一电容之间,根据所述第一频率信号开启或是关闭;一第三开关,设置在所述第三输入端与所述第一电容之间,根据所述第二频率信号开启或是关闭;一第四开关,设置在所述第四输入端与所述第二信号输入端之间,根据所述第一频率信号开启或是关闭;一第五开关,设置在所述第五输入端与所述第二电容之间,根据所述第一频率信号开启或是关闭;以及一第六开关,设置在所述第六输入端与所述第二电容之间,根据所述第二频率信号开启或是关闭。

7.优选地,所述第一电路的所述第一信号输入端是一输入信号正端,所述第一电路的所述第二信号输入端是一输入信号负端。

8.本实用新型还公开了一种信号输入电路模块,连接一第一电路,所述信号输入电路模块包括多个信号输入电路,所述多个信号输入电路以串联连接且顺序连接的方式设置,每一所述信号输入电路包括:一第一输入端,连接所述第一信号输入端,接收一重置电压;一第一电容,包括一第一端以及一第二端,所述第一电容的所述第二端电性连接所述第一输入端以及所述第一电路的所述第一信号输入端;一第二输入端,连接所述第一电容的所述第一端,所述第二输入端接收一信号电压;一第三输入端,连接所述第一电容的所述第一端,所述第三输入端接收一参考电压,其中所述信号电压与所述参考电压不同时提供至所述第一电容的所述第一端;一第四输入端,连接所述第一电路的所述第二信号输入端,接收所述信号电压;一第二电容,包括一第一端以及一第二端,所述第二电容的所述第一端连接所述第四输入端;一第五输入端,连接所述第二电容的所述第二端,所述第五输入端接收所述重置电压;一第六输入端,连接所述第二电容的所述第二端,所述第六输入端接收所述参考电压,其中所述重置电压与所述参考电压不同时提供至所述第二电容的所述第二端;一第一输出端,连接所述第一输入端以及所述第一电容的所述第二端;以及一第二输出端,连接所述第四输入端以及所述第二电容的所述第一端;其中,顺序连接的所述多个信号输入电路的其中之一的所述第一输出端连接至顺序连接的另一所述信号输入电路的所述第一输入端,顺序连接的所述多个信号输入电路的其中之一的所述第二输出端连接至顺序连接的另一所述信号输入电路的所述第四输入端。

9.优选地,所述第一输入端、所述第二输入端、所述第四输入端以及所述第五输入端是根据一第一频率信号而动作,所述第三输入端以及所述第六输入端是根据一第二频率信号而动作。

10.优选地,还包括:一第一开关,设置在所述第一输入端与所述第一信号输入端之间,根据所述第一频率信号开启或是关闭;一第二开关,设置在所述第二输入端与所述第一电容之间,根据所述第一频率信号开启或是关闭;一第三开关,设置在所述第三输入端与所述第一电容之间,根据所述第二频率信号开启或是关闭;一第四开关,设置在所述第四输入端与所述第二信号输入端之间,根据所述第一频率信号开启或是关闭;一第五开关,设置在所述第五输入端与所述第二电容之间,根据所述第一频率信号开启或是关闭;以及一第六开关,设置在所述第六输入端与所述第二电容之间,根据所述第二频率信号开启或是关闭。

11.优选地,所述第一电路的所述第一信号输入端是一输入信号正端,所述第一电路的所述第二信号输入端是一输入信号负端。

12.本实用新型还公开了一种电路结构,包括:一第一电路,包括一第一信号输入端以及一第二信号输入端;一信号输入电路,连接所述第一电路;其中,所述信号输入电路包括:一第一输入端,连接所述第一信号输入端,接收一重置电压(vrst);一第一电容,包括一第一端以及一第二端,所述第一电容的所述第二端电性连接所述第一输入端以及所述第一电路的所述第一信号输入端;一第二输入端,连接所述第一电容的所述第一端,所述第二输入端接收一信号电压;一第三输入端,连接所述第一电容的所述第一端,所述第三输入端接收一共模信号电压,其中,所述信号电压与所述共模信号电压不同时提供至所述第一电容的所述第一端;一第四输入端,连接所述第一电路的所述第二信号输入端,接收所述信号电

压;一第二电容,包括一第一端以及一第二端,所述第二电容的所述第一端连接所述第四输入端;一第五输入端,连接所述第二电容的所述第二端,所述第五输入端接收所述重置电压(vrst);以及一第六输入端,连接所述第二电容的所述第二端,所述第六输入端接收所述共模信号电压,其中,所述重置电压与所述共模信号电压不同时提供至所述第二电容的所述第二端;其中,所述信号输入电路的所述第一输入端以及所述第四输入端分别连接所述第一电路的所述第一信号输入端以及所述第二信号输入端。

13.本实用新型还提供一种电路结构,包括:一第一电路;以及一信号输入电路模块,包括多个信号输入电路,所述多个信号输入电路以串联连接且顺序连接的方式设置,每一所述信号输入电路包括:一第一输入端,连接所述第一信号输入端,接收一重置电压(vrst);一第一电容,包括一第一端以及一第二端,所述第一电容的所述第二端电性连接所述第一输入端以及所述第一电路的所述第一信号输入端;一第二输入端,连接所述第一电容的所述第一端,所述第二输入端接收一信号电压;一第三输入端,连接所述第一电容的所述第一端,所述第三输入端接收一参考电压(vref),其中,所述信号电压与所述参考电压(vref)不同时提供至所述第一电容的所述第一端;一第四输入端,连接所述第一电路的所述第二信号输入端,接收所述信号电压;一第二电容,包括一第一端以及一第二端,所述第二电容的第一端连接所述第四输入端;一第五输入端,连接所述第二电容的所述第二端,所述第五输入端接收所述重置电压(vrst);一第六输入端,连接所述第二电容的所述第二端,所述第六输入端接收所述参考电压(vref),其中所述重置电压与所述参考电压(vref)不同时提供至所述第二电容的所述第二端;一第一输出端,连接所述第一输入端以及所述第一电容的所述第二端;以及一第二输出端,连接所述第四输入端以及所述第二电容的所述第一端;其中,顺序连接的所述多个信号输入电路的其中之一的所述第一输出端连接至顺序连接的另一所述信号输入电路的所述第一输入端,顺序连接的所述多个信号输入电路的其中之一的所述第二输出端连接至顺序连接的另一所述信号输入电路的所述第四输入端。

14.本实用新型的其中一有益效果在于,本实用新型所提供的信号输入电路以及电路结构,可以利用一被动电路提供信号增益,且提供一较为稳定的共模信号,并可以有效降低电源消耗。

15.为使能更进一步了解本实用新型的特征及技术内容,请参阅以下有关本实用新型的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本实用新型加以限制。

附图说明

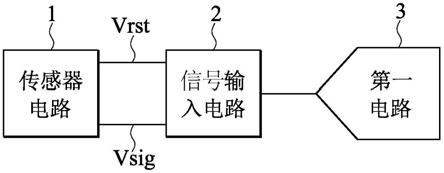

16.图1是本实用新型的电路结构与传感器电路的示意图。

17.图2是本实用新型第一实施例的电路结构的示意图。

18.图3是本实用新型第二实施例的电路结构的示意图。

19.图4是本实用新型第二实施例的电路结构的另一示意图。

具体实施方式

20.以下是通过特定的具体实施例来说明本实用新型所公开有关“电路结构与信号输入电路”的实施方式,本领域技术人员可由本说明书所公开的内容了解本实用新型的优点

与效果。本实用新型可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本实用新型的构思下进行各种修改与变更。另外,本实用新型的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本实用新型的相关技术内容,但所公开的内容并非用以限制本实用新型的保护范围。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

21.[第一实施例]

[0022]

请参阅图1、图2,图1是本实用新型的电路结构与传感器电路的示意图。图2是本实用新型第一实施例的电路结构的示意图。

[0023]

在本实用新型的电路说明中,垂直设置的两个接脚的电子组件,其上方一端为第一端,其下方一端则是第二端。水平设置的两个接脚的电子组件,其左侧一端为第一端,其右侧一端则是第二端。

[0024]

一传感器电路1包括两个输出端,分别是一第一感测输出端以及一第二感测输出端。传感器电路1的第一感测输出端以及一第二感测输出端电性连接信号输入电路2。信号输入电路2则是电性连接一第一电路3。

[0025]

请参阅图2,在本实施例中,提供了一种电路结构c1,电路结构c1包括信号输入电路2以及一第一电路3。信号输入电路2是用于提供一第一信号以及一第二信号给一第一电路3。在本实施例中,第一电路3是一放大器电路。

[0026]

第一电路3包括一第一信号输入端vip以及一第二信号输入端vin。信号输入电路2包括一第一输入端vin1、一第一电容c1、一第二输入端vin2、一第三输入端vin3、一第四输入端vin4、一第二电容c2、一第五输入端vin5、一第六输入端vin6。

[0027]

在本实施例中,信号输入电路2接收传感器电路1提供的重置电压vrst以及信号电压vsig。第一输入端vin1连接第一信号输入端vip,以接收重置电压vrst。第一电容c1包括一第一端以及一第二端。第一电容c1的第二端电性连接第一输入端vin1以及第一电路3的第一信号输入端vip。第二输入端vin2连接第一电容c1的第一端。第二输入端vin2接收一信号电压vsig。第三输入端vin3连接第一电容c1的第一端。第三输入端vin3接收一共模信号电压vcm。当信号电压vsig与共模信号电压vcm不同时提供至第一电容的第一端。第四输入端vin4连接第一电路3的第二信号输入端vin,接收信号电压vsig。第二电容c2包括一第一端以及一第二端。第二电容c2的第一端连接第四输入端vin4。第五输入端vin5连接第二电容c2的第二端。第五输入端vin5接收重置电压vrst。第六输入端vin6连接第二电容c2的第二端。第六输入端vin6接收共模信号电压vcm。当信号电压vsig与共模信号电压vcm不同时,则提供至第二电容c2的第一端。

[0028]

在本实施例中,共模信号电压vcm是重置电压vrst与信号电压vsig的总和的一半。

[0029]

其中,vip=vrst

–

vsig+vcm,vin=vsig-srst+vcm

[0030]

因此输入的共模信号vicm则会等于输入第一信号输入端vip的电压加上输入第二信号输入端vin的电压的总和的一半。

[0031]

输入第一电路3的差动模式信号电压vidm则是输入第一信号输入端vip的电压减去输入第二信号输入端vin的电压,也就是,等于两倍的重置电压vrst减去共模信号电压vsig(vrst-vsig)*2。

[0032]

第一输入端vin1、第二输入端vin2、第四输入端vin4以及第五输入端vin5是根据一第一频率信号ck1而动作。第三输入端vin3以及第六输入端vin6是根据一第二频率信号ck2而动作。在本实施例中,第一频率信号ck1是第二频率信号ck2的反相信号。

[0033]

在本实施例中,信号输入电路2还包括一第一开关sw1、第二开关sw2、第三开关sw3、第四开关sw4、第五开关sw5以及第六开关sw6。

[0034]

第一开关sw1设置在第一输入端vin1与第一信号输入端vip之间,根据第一频率信号ck1开启或是关闭。第二开关sw2设置在第二输入端vin2与第一电容c1之间,根据第一频率信号ck1开启或是关闭。第三开关sw3,设置在第三输入端vin3与第一电容c1之间,根据第二频率信号ck2开启或是关闭。第四开关sw4设置在第四输入端vin4与第二信号输入端vin之间,根据第一频率信号ck1开启或是关闭。第五开关sw5设置在第五输入端vin5与第二电容c2之间,根据第一频率信号ck1开启或是关闭。第六开关sw6,设置在第六输入端vin6与第二电容c2之间,根据第二频率信号ck2开启或是关闭。

[0035]

在本实施例中,第一电路3的第一信号输入端vip是一输入信号正端。第一电路3的第二信号输入端vin是一输入信号负端。

[0036]

[第二实施例]

[0037]

请参阅图3以及图4,图3是本实用新型第二实施例的电路结构的示意图。图4是本实用新型第二实施例的电路结构的另一示意图。

[0038]

在本实施例中,提供了一种电路结构c2(图3)以及电路结构c3(图4)。在图3中,电路结构c2的信号输入电路模块5连接一第一电路3。在图4中,电路结构c3的信号输入电路模块5也同样连接一第一电路3。在图3以及图4中的信号输入电路模块5分别包括多个信号输入电路2。多个信号输入电路2以串联连接且顺序连接的方式设置。

[0039]

图3中的电路结构c2是包括两阶的信号输入电路2。图4中的电路结构c2是包括三阶的信号输入电路2。

[0040]

每一信号输入电路2包括一第一输入端vin1、一第一电容c1、一第二输入端vin2、一第三输入端vin3、一第四输入端vin4、一第二电容c2、一第五输入端vin5、一第六输入端vin6、一第一输出端vo1以及一第二输出端vo2。

[0041]

第一输入端vin1,连接第一信号输入端vip,接收一重置电压(vrst)。

[0042]

第一电容c1包括一第一端以及一第二端。第一电容c1的第二端电性连接第一输入端以及所述第一电路的所述第一信号输入端。第二输入端vin2连接第一电容c1的第一端。第二输入端vin2接收一信号电压vsig。第三输入端vin3连接第一电容c1的第一端。第三输入端vin3接收一参考电压vref。当信号电压vsig与参考电压vref不同时提供至第一电容c1的第一端。第四输入端vin4连接第一电路3的第二信号输入端vin,接收信号电压vsig。第二电容c2包括一第一端以及一第二端。第二电容c2的第一端连接第四输入端vin4。第五输入端vin5连接第二电容c2的第二端。第五输入端vin5接收重置电压vrst。第六输入端vin6连接第二电容c2的第二端。第六输入端vin6接收参考电压vref。当信号电压vsig与参考电压vref不同时提供至第二电容c2的第一端。

[0043]

第一输出端vo1,连接所述第一输入端以及所述第一电容的所述第二端。第二输出端vo2连接第四输入端vin4以及第二电容c2的第一端。其中,顺序连接的多个信号输入电路2的其中之一的第一输出端vo1连接至顺序连接的另一个信号输入电路2的第一输入端

vin1,顺序连接的多个信号输入电路2的其中之一的第二输出端vo2连接至顺序连接的另一信号输入电路2的第四输入端vin4。

[0044]

在本实施例中,各信号输入电路2的第一输入端vin1、第二输入端vin2、第四输入端vin4以及第五输入端vin5是根据一第一频率信号ck1而动作,第三输入端vin3以及第六输入端vin6是根据一第二频率信号ck2而动作。

[0045]

在本实施例中,每一信号输入电路2,还包括一第一开关sw1、一第二开关sw2、一第三开关sw3、一第四开关sw4、一第五开关sw5以及ㄧ第六开关sw6。

[0046]

第一开关sw1,设置在第一输入端vin1与第一信号输入端vip之间,根据第一频率信号ck1开启或是关闭。第二开关sw2,设置在第二输入端vin2与第一电容c1之间,根据第一频率信号ck1开启或是关闭。第三开关sw3设置在第三输入端vin3与第一电容c1之间,根据第二频率信号ck2开启或是关闭。第四开关sw4,设置在第四输入端与第二信号输入端之间,根据所述第一频率信号开启或是关闭。第五开关sw5,设置在第五输入端vin5与第二电容c2之间,根据第一频率信号ck1开启或是关闭。第六开关sw6,设置在第六输入端vin6与第二电容c2之间,根据第二频率信号ck2开启或是关闭。

[0047]

在本实施例中,第一电路3的第一信号输入端vip是一输入信号正端。第一电路3的第二信号输入端vin是一输入信号负端。

[0048]

请参阅图3,由于图3中的电路结构c2的两阶信号输入电路2是串联设置,每一阶的第一开关sw1与第四开关sw4可以利用同一个第一开关sw1与第四开关sw4进行控制。

[0049]

在本实施例中,是利用两个信号输入电路2进行串联,其中一阶信号输入电路2的第一电容c1与第二电容c2是相同阻抗值的。另一阶的信号输入电路2的第一电容c1与第二电容c2也是相同阻抗值。然而不同阶的信号输入电路2的电容的阻抗值可以是相同或是不相同。在本实施例中,第一阶信号输入电路2的第一电容c1与第二电容的阻抗值是cx,第二阶信号输入电路2的第一电容c1与第二电容的阻抗值是cy。

[0050]

输入共模电压vicm则是等于参考电压vref乘上第一阶信号输入电路2的电容阻抗值与第二阶信号输入电路2的电容阻抗值的一比例值。也就是如下公式所示:

[0051]

vcm=vref*(cx/(cx+cy))

ꢀꢀꢀ

公式1

[0052]

而输入的差动模式信号电压vidm则是等于2*(vrst-vsig)。也就是,等于两倍的重置电压vrst减去共模信号电压vsig。

[0053]

请参阅图4,由于图4中的电路结构c3的三阶信号输入电路2是串联设置,每一阶的第一开关sw1与第四开关sw4可以利用同一个第一开关sw1与第四开关sw4进行控制。

[0054]

在本实施例中,是利用三个信号输入电路2进行串联,其中第一阶信号输入电路2的第一电容c1与第二电容c2是相同阻抗值的。第二阶的信号输入电路2的第一电容c1与第二电容c2是相同阻抗值。第三阶的信号输入电路2的第一电容c1与第二电容c2也是相同阻抗值。

[0055]

然而不同阶的信号输入电路2的电容的阻抗值可以是相同或是不相同。在本实施例中,第一阶信号输入电路2的第一电容c1与第二电容的阻抗值是cx,第二阶信号输入电路2的第一电容c1与第二电容的阻抗值是cy。第三阶信号输入电路2的第一电容c1与第二电容的阻抗值是cz。

[0056]

输入共模电压vicm则是等于参考电压vref乘上第一阶信号输入电路2的电容阻抗

值、第二阶信号输入电路2的电容阻抗值以及第三阶信号输入电路2的电容阻抗值的一比例值。也就是如下公式所示:

[0057]

vcm=vref*(cx+0.5cz)/(cx+cy+cz))

ꢀꢀꢀ

公式2

[0058]

而输入的差动模式信号电压vidm则是如下公式所示:

[0059]

vidm=2*(vrst-vsig)-(vref*c3)/(cx+cy+cz)

[0060]

[实施例的有益效果]

[0061]

本实用新型的其中一有益效果在于,本实用新型所提供的信号输入电路以及电路结构,可以利用一被动电路提供信号增益,且提供一较为稳定的共模信号,并可以有效降低电源消耗。

[0062]

以上所公开的内容仅为本实用新型的优选可行实施例,并非因此局限本实用新型的申请专利范围,所以凡是运用本实用新型说明书及图式内容所做的等效技术变化,均包含于本实用新型的申请专利范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1