集成有垂直场效应晶体管的低压闪速存储器的制作方法

本发明一般涉及半导体结构及其形成方法。更具体地说,本发明涉及一种包括与垂直场效应晶体管(vfet)集成的低压闪速存储器的半导体结构。

背景技术:

1、深度学习是一种基于由生物系统中的信息处理启发的人工神经网络的机器学习方法。在神经形态计算中,电子模拟电路被用于模拟神经系统中存在的神经生物学架构。

技术实现思路

1、根据本发明的一个实施例,提供了一种电路。该电路可以包括与垂直场效应晶体管和非易失性存储元件集成的低压闪速存储器。低压闪速存储器可以通过垂直场效应晶体管、一条或多条位线以及一条或多条字线耦合到非易失性存储元件。低压闪速存储器可以提供较低的显著(significance)电导,而非易失性存储元件可以提供较高的显著电导。低压闪速存储器可以包括源极和漏极。源极可以通过外延沟道与漏极分离。低压闪速存储器可以包括浮置栅极。浮置栅极可以通过第一电介质层与外延沟道分离。低压闪速存储器可以包括控制栅极。控制栅极可以通过第二电介质层与浮置栅极分离。可以通过向控制栅极施加相反极性的电压脉冲来对低压闪速存储器进行编程。可以通过关断垂直场效应晶体管并将编程电压施加到低压闪速存储器的控制栅极来对低压闪速存储器进行编程。可以通过导通垂直场效应晶体管并向低压闪速存储器的控制栅极施加读取电压来读取低压闪速存储器。源极、漏极和外延沟道可以用n型掺杂剂掺杂。非易失性存储器元件可以是相变存储器、电阻随机存取存储器、磁随机存取存储器或闪速存储器。

2、根据本发明的另一实施例,提供一种半导体结构。该半导体结构可以包括与垂直场效应晶体管集成的低压闪速存储器和非易失性存储元件。低压闪速存储器可以通过垂直场效应晶体管、一条或多条位线以及一条或多条字线耦合到非易失性存储元件。低压闪速存储器可以包括第一源漏极、第二源漏极、浮置栅极和控制栅极。第二源漏极可以通过外延沟道与第一源漏极分隔开。浮置栅极可以通过第一电介质层与外延沟道分离。控制栅极可以通过第二电介质层与浮置栅极分离。浮置栅极可以具有与外延沟道的掺杂类型相反的掺杂类型。第一源漏极、第二源漏极和外延沟道可以掺杂有n型掺杂剂。第一电介质可以由高k电介质材料制成。低压闪速存储器可以是垂直的,并且可以通过浅沟槽隔离与垂直场效应晶体管分离。非易失性存储器元件可以是相变存储器、电阻随机存取存储器、磁随机存取存储器或闪速存储器。

3、根据本发明的另一实施例,提供了一种方法。该方法可以包括形成与垂直场效应晶体管集成的低压闪速存储器和非易失性存储器元件。该方法可以包括在低压闪速存储器和垂直场效应晶体管之间形成浅沟槽隔离。低压闪速存储器可以通过垂直场效应晶体管耦合到非易失性存储元件。形成低压闪速存储器可以包括在衬底上生长第一源漏极,在第一源漏极上外延生长外延沟道,在外延沟道上外延生长第二源漏极,在外延沟道周围形成浮置栅极,以及在浮置栅极周围形成控制栅,控制栅极通过第一电介质层与浮置栅极分离。第一电介质层可以由高k电介质材料制成。第一源漏极、外延沟道和第二源漏极可以掺杂有n型掺杂剂。非易失性存储器元件可以是相变存储器、电阻随机存取存储器、磁随机存取存储器或闪速存储器。浮置栅极可以具有与外延沟道的掺杂类型相反的掺杂类型。

技术特征:

1.一种半导体结构,包括:

2.根据权利要求1所述的半导体结构,其中所述低压闪速存储器储器包括:

3.根据权利要求2所述的半导体结构,其中所述浮置栅极具有与所述外延沟道的掺杂类型相反的掺杂类型。

4.根据权利要求2所述的半导体结构,其中,所述第一源漏极、所述第二源漏极和所述外延沟道掺杂有n型掺杂剂。

5.根据权利要求2所述的半导体结构,其中所述第一电介质由高k电介质材料制成。

6.根据权利要求1所述的半导体结构,其中所述低压闪速存储器储器是垂直的。

7.根据权利要求1所述的半导体结构,其中所述低压闪速存储器通过浅沟槽隔离与所述垂直场效应晶体管分离。

8.根据权利要求1所述的半导体结构,其中所述非易失性存储器元件是相变存储器、电阻式随机存取存储器、磁性随机存取存储器或闪速存储器。

9.一种包括如权利要求1所述的半导体结构的电路。

10.根据权利要求9所述的电路,其中所述低压闪速存储器提供较低显著电导,并且所述非易失性存储器元件提供较高显著电导。

11.根据权利要求9所述的电路,其中所述低压快闪速存储器储器包括:

12.根据权利要求9所述的电路,其中通过向所述控制栅极施加相反极性的电压脉冲来编程所述低压闪速存储器储器。

13.根据权利要求9所述的电路,其中通过关断所述垂直场效应晶体管并将编程电压施加到所述低压闪速存储器储器的所述控制栅极来编程所述低压闪速存储器储器。

14.根据权利要求9所述的电路,其中通过接通所述垂直场效应晶体管并将读取电压施加到所述低压闪速存储器的所述控制栅极来读取所述低压闪速存储器。

15.根据权利要求9所述的电路,其中,所述源极、所述漏极和所述外延沟道掺杂有n型掺杂剂。

16.一种方法,包括:

17.根据权利要求16所述的方法,其中形成所述低压闪速存储器包括:

18.根据权利要求17所述的方法,其中所述第一电介质层由高k电介质材料制成。

19.根据权利要求17所述的方法,其中,所述第一源漏极、所述外延沟道和所述第二源漏极掺杂有n型掺杂剂。

20.根据权利要求17所述的方法,其中,所述浮置栅极具有与所述外延沟道的掺杂类型相反的掺杂类型。

21.根据权利要求16所述的方法,其中所述非易失性存储器元件是相变存储器、电阻式随机存取存储器、磁性随机存取存储器或闪速存储器。

22.根据权利要求16所述的方法,还包括:

技术总结

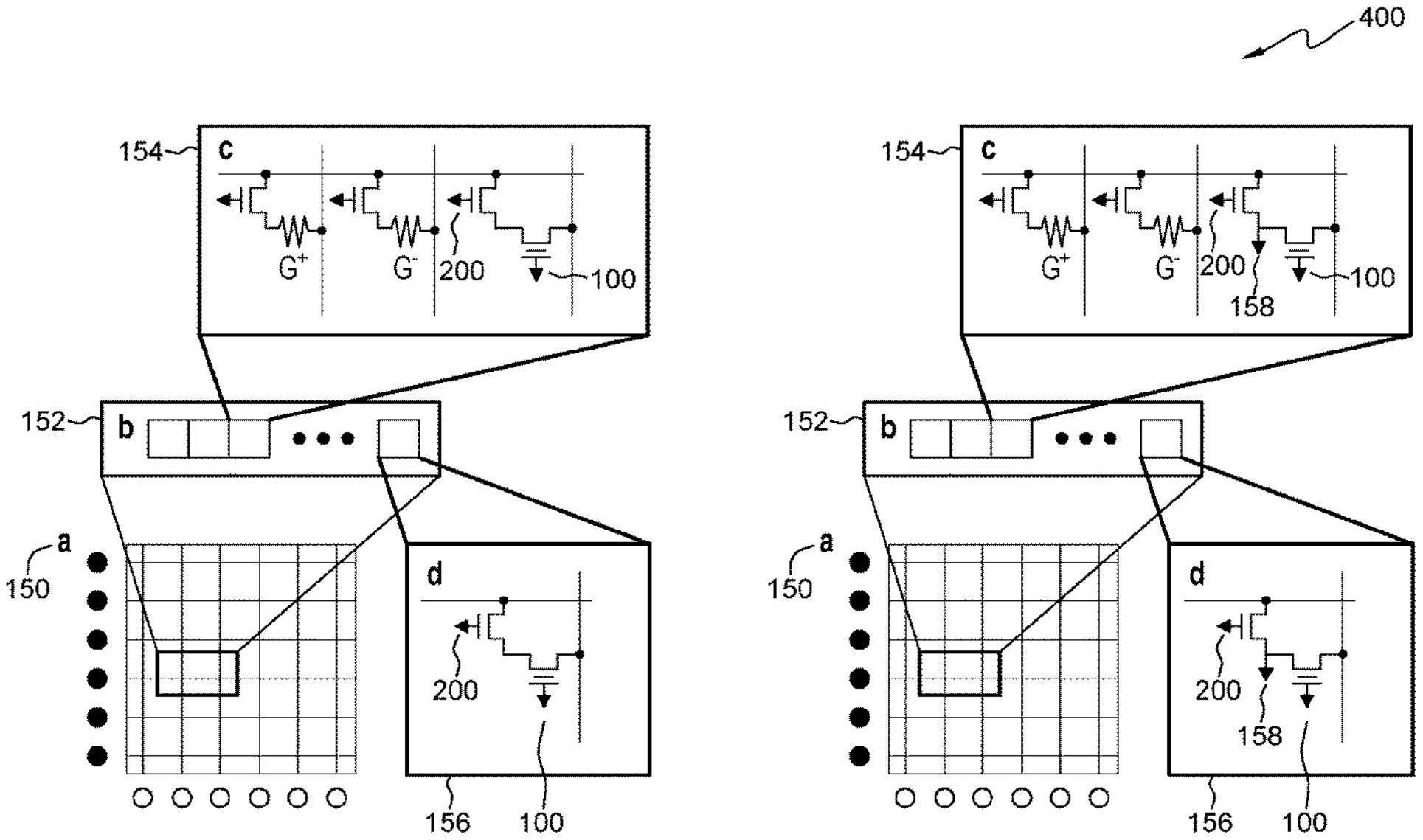

一种电路(400)包括与垂直场效应晶体管集成的低压闪速存储器(200)和非易失性存储器元件(100)。低压闪速存储器通过垂直场效应晶体管、一条或多条位线和一条或多条字线与非易失性存储器元件耦合。低压闪速存储器可以提供较低的显著电导,非易失性存储器元件可以提供较高的显著电导。低电压闪速存储器可以包括源极和漏极。源极可以通过外延通道与漏极分开。低压闪速存储器可以包括浮置栅极。浮置栅极可以通过第一电介质层与外延通道分开。低压闪速存储器可以包括控制栅极。控制栅极可以通过第二电介质层与浮置栅极分开。

技术研发人员:B·赫克马绍尔塔巴里,A·雷兹尼彻,安藤崇志,龚南博

受保护的技术使用者:国际商业机器公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!