可堆叠定时器的制作方法

背景技术:

1、片上系统(“soc”)可以包括各种各样的电子电路、子系统和其他组件以执行各种功能。为了构建soc和包含的电路、子系统和其他组件以执行各种功能,可以使用针对不同的电路、子系统和其他组件的若干不同的知识产权(“ip”)核(或ip块)。ip核指的是逻辑、单元或集成电路(有时称为“芯片”)布局和设计的可重复利用的构件,ip核之所以这样命名,是因为它可能指的是某一方的合法知识产权的信息。在本披露的上下文中,ip核将指的是与芯片或soc的设计规范相关联的逻辑和/或元数据。ip核或ip块可以是“软ip”或“硬ip”。在本披露的上下文中,作为“软ip”的ip块可以指ip块的软件实现,比如,verilog或vhdl功能模型,其可以经过ip消费者的合成和实现流程来生成物理产品。在本披露的上下文中,作为“硬ip”的ip块可以指ip块的物理硬件实现,比如,执行ip块的期望功能的晶体管组合。例如,硬ip电路块可以包括soc中的电路。

2、可以组合ip块来构建soc应用的期望功能。鉴于soc的复杂性不断增加,由单一来源为特定soc提供或开发所有必需的ip块是困难和/或低效的。因此,许多soc开发人员寻求从其他来源获得许可以使用所需的ip块。因此,ip块的市场已经发展起来,在这个市场中,开发人员提供了可获得许可的用于众多功能的各种ip块的目录。

3、一种有用的ip块是用于可用于形成定时器设备的定时器电路的ip块。定时器设备可用于许多应用,包括脉冲宽度调制、计数、触发和捕获-比较功能。捕获-比较可以指两种操作模式:捕获模式和比较模式。例如,定时器的捕获模式使定时器能够在发生特定事件(比如捕获-比较引脚上的转变)时将当前值存储到捕获-比较寄存器。例如,捕获模式使得能够测量捕获-比较引脚拾取的外部事件的时间间隔。比较模式可以不断地将捕获-比较寄存器中的值与控制值(比如当前时间值)进行比较,然后当寄存器中的值与控制值匹配时,定时器可以触发捕获-比较引脚上的中断或转变。例如,比较模式使得能够在硬件(无需软件)中生成固定的时间间隔。固定的时间间隔可用于在捕获-比较引脚上生成信号(比如脉冲宽度调制(“pwm”)信号),或者在其他外设中启动动作。

4、由于定时器设备的广泛应用,所以定时器电路的大小和功能差异很大。许多soc需要大量不同大小和能力的定时器。例如,在一个电路中,soc应用可能需要具有两个捕获-比较通道的定时器,而在soc上的另一个电路中,可能需要具有八个捕获-比较通道的定时器。为了适应这些情况,ip提供商可以提供两种定时器ip块:一种具有两个捕获-比较通道,另一种具有八个捕获-比较通道。然而,在soc上的又一个电路中,可能需要具有六个捕获-比较通道的定时器。在这种情况下,将需要使用具有八个捕获-比较通道的定时器ip块,或者许可方将需要开发又一种具有六个捕获-比较通道的ip块来满足这一需要。

5、使用大于所需通道数的定时器会使soc上的资源利用效率低下。相反,使用小于期望通道数的定时器可能会限制soc的能力。

6、此外,需要测试和验证电路系统,并且使用各种不同定时器ip块的soc可能需要测试和验证每个不同的ip块。

技术实现思路

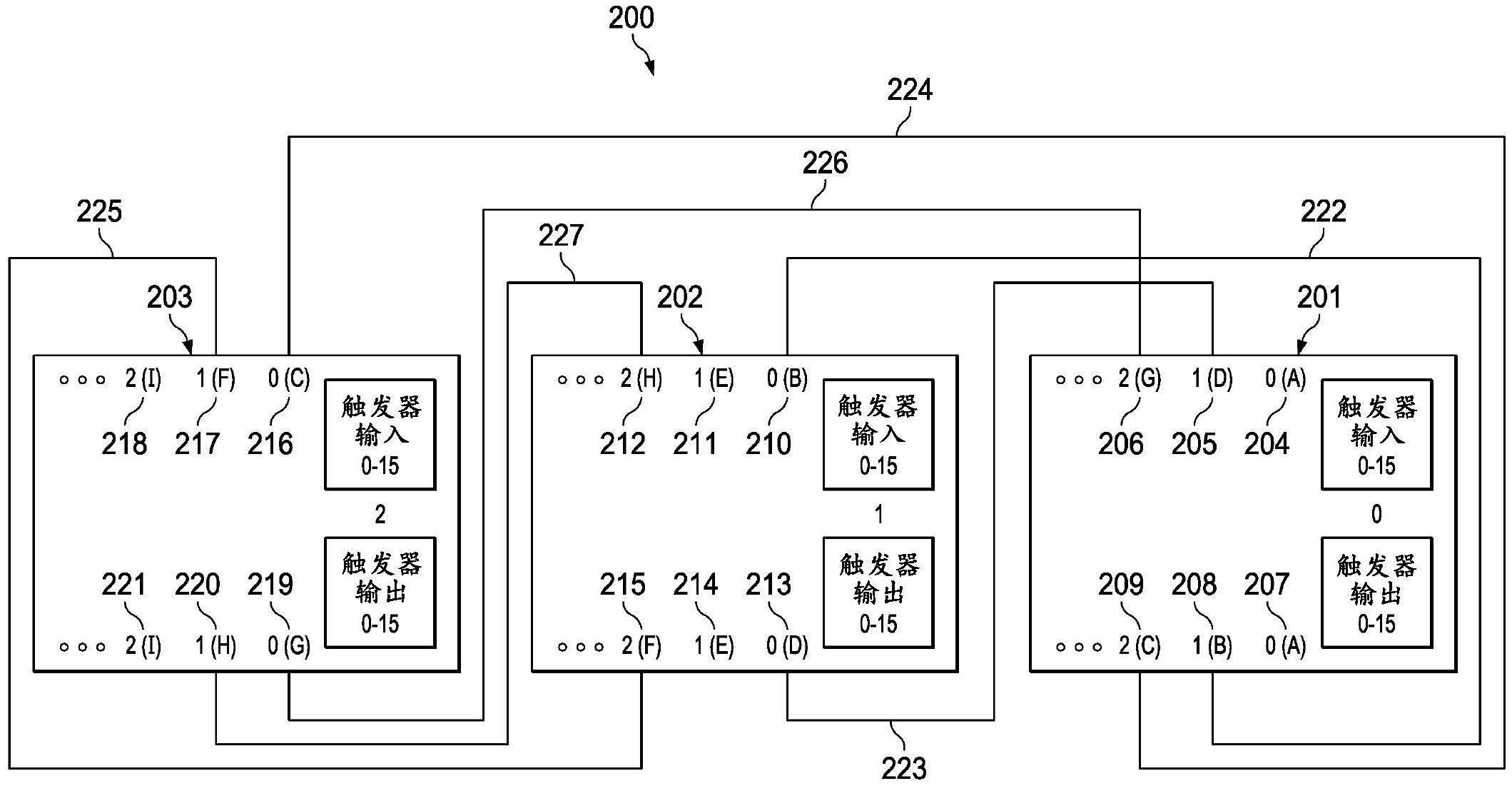

1、在一些示例中,一种soc包括可堆叠基本定时器电路(在本文中也称为定时器电路块或定时器设备),其可以与一个或多个附加可堆叠基本定时器电路组合以形成具有更多能力(例如,更多的捕获-比较通道)的定时器。可堆叠基本定时器电路的多个实例可以与可编程触发器矩阵组合以创建所需的定时器。在一些示例中,所述可堆叠基本定时器电路中的一个可以被配置为主定时器,并且通过交叉触发器矩阵耦合到所述主定时器的其他可堆叠基本定时器电路可以被配置为所述主定时器的辅定时器。在一些示例中,由主定时器接收到的设备故障信号将通过主定时器与辅定时器之间的可编程故障交叉触发器矩阵传送到辅定时器。

2、在一些示例中,soc包括处理器和多个定时器电路块,所述多个定时器电路块至少包括第一定时器电路块和第二定时器电路块。所述多个定时器电路块中的每一个定时器电路块通过第一可编程矩阵和第二可编程矩阵中的至少一个选择性地耦合。在一些示例中,所述第一可编程矩阵被配置为将所述第一定时器电路块的第二触发器输入与所述第二定时器电路块的第一触发器输出耦合。在一些示例中,所述第二可编程矩阵被配置为将所述第一定时器电路块的第二故障输入与所述第二定时器电路块的第一故障输出耦合。

3、在一些示例中,一种集成电路包括第一定时器设备,所述第一定时器设备具有第一多个触发器输入、第一多个触发器输出、第一多个故障触发器输入和第一多个故障触发器输出。所述集成电路包括第二定时器设备,所述第二定时器设备具有第二多个触发器输入、第二多个触发器输出、第二多个故障触发器输入和第二多个故障触发器输出。所述第一多个触发器输出中的触发器输出耦合到所述第二多个触发器输入中的触发器输入。所述第二多个触发器输出中的触发器输出耦合到所述第一多个触发器输入中的触发器输入。所述第一多个故障触发器输出中的故障触发器输出耦合到所述第二多个故障触发器输入中的故障触发器输入。所述第二多个故障触发器输出中的故障触发器输出耦合到所述第一多个故障触发器输入中的故障触发器输入。

4、在一些示例中,至少一种非暂态计算机可读介质包括将第一定时器电路块与第二定时器电路块堆叠在片上系统上的指令。所述指令在执行时,配置第一矩阵执行以下操作:将第一定时器电路块的多个触发器输入中的第二触发器输入与第二定时器电路块的多个触发器输出中的第一触发器输出耦合;以及将所述第二定时器电路块的多个触发器输入中的第一触发器输入与所述第一定时器电路块的多个触发器输出中的第二触发器输出耦合。所述指令在执行时,配置第二矩阵执行以下操作:将所述第一定时器电路块的多个故障输入中的第二故障输入与所述第二定时器电路块的多个故障输出中的第一故障输出耦合;以及将所述第二定时器电路块的多个故障输入中的第一故障输入与所述第一定时器电路块的故障输出中的第二故障输出耦合。

技术特征:

1.一种片上系统,包括:

2.如权利要求1所述的片上系统,其中:

3.如权利要求1所述的片上系统,其中:

4.如权利要求1所述的片上系统,其中:

5.如权利要求4所述的片上系统,其中:

6.如权利要求5所述的片上系统,其中:

7.如权利要求6所述的片上系统,其中:

8.如权利要求7所述的片上系统,其中:

9.如权利要求1所述的片上系统,其中:

10.如权利要求1所述的片上系统,其中:

11.如权利要求1所述的片上系统,其中:

12.如权利要求11所述的片上系统,其中:

13.一种集成电路,包括:

14.如权利要求13所述的集成电路,其中,所述第一定时器设备触发所述第二定时器设备。

15.如权利要求13所述的集成电路,其中,所述第一定时器设备进一步包括:

16.如权利要求13所述的集成电路,其中,所述第二定时器设备进一步包括:

17.至少一种非暂态计算机可读介质,包括将第一定时器电路块与第二定时器电路块堆叠在片上系统上的指令,所述指令在执行时:

18.如权利要求17所述的至少一种非暂态计算机可读介质,其中:

19.如权利要求17所述的至少一种非暂态计算机可读介质,其中:

20.如权利要求19所述的至少一种非暂态计算机可读介质,其中:

技术总结

多个定时器电路块(201,202,203)至少包括第一定时器电路块(201)和第二定时器电路块(202)。所述多个定时器电路块(201,202,203)中的每一个定时器电路块可以通过第一可编程矩阵和第二可编程矩阵中的至少一个选择性地耦合。在一些示例中,所述第一可编程矩阵可以被配置为将所述第一定时器电路块(201)的第二触发器输入(205)与所述第二定时器电路块(202)的第一触发器输出(213)耦合。

技术研发人员:R·哈里哈兰,S·M·马迪亚斯塔

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!