半导体封装结构及其制作方法与流程

本发明涉及一种半导体封装结构及其制作方法,且特别涉及一种可缩短传输路径并可提升工作效能的半导体封装结构及其制作方法。

背景技术:

1、目前,半导体封装结构中的存储器芯片与逻辑芯片是以水平的方式配置在线路基板上。其中,存储器芯片与逻辑芯片可先通过焊球接合至中介层(interposer),再使中介层通过焊球接合至线路基板。因此,存储器芯片与逻辑芯片之间的信号传输需要通过焊球、中介层以及线路基板。

技术实现思路

1、本发明提供一种半导体封装结构及其制作方法,其可缩短传输路径并可提升工作效能。

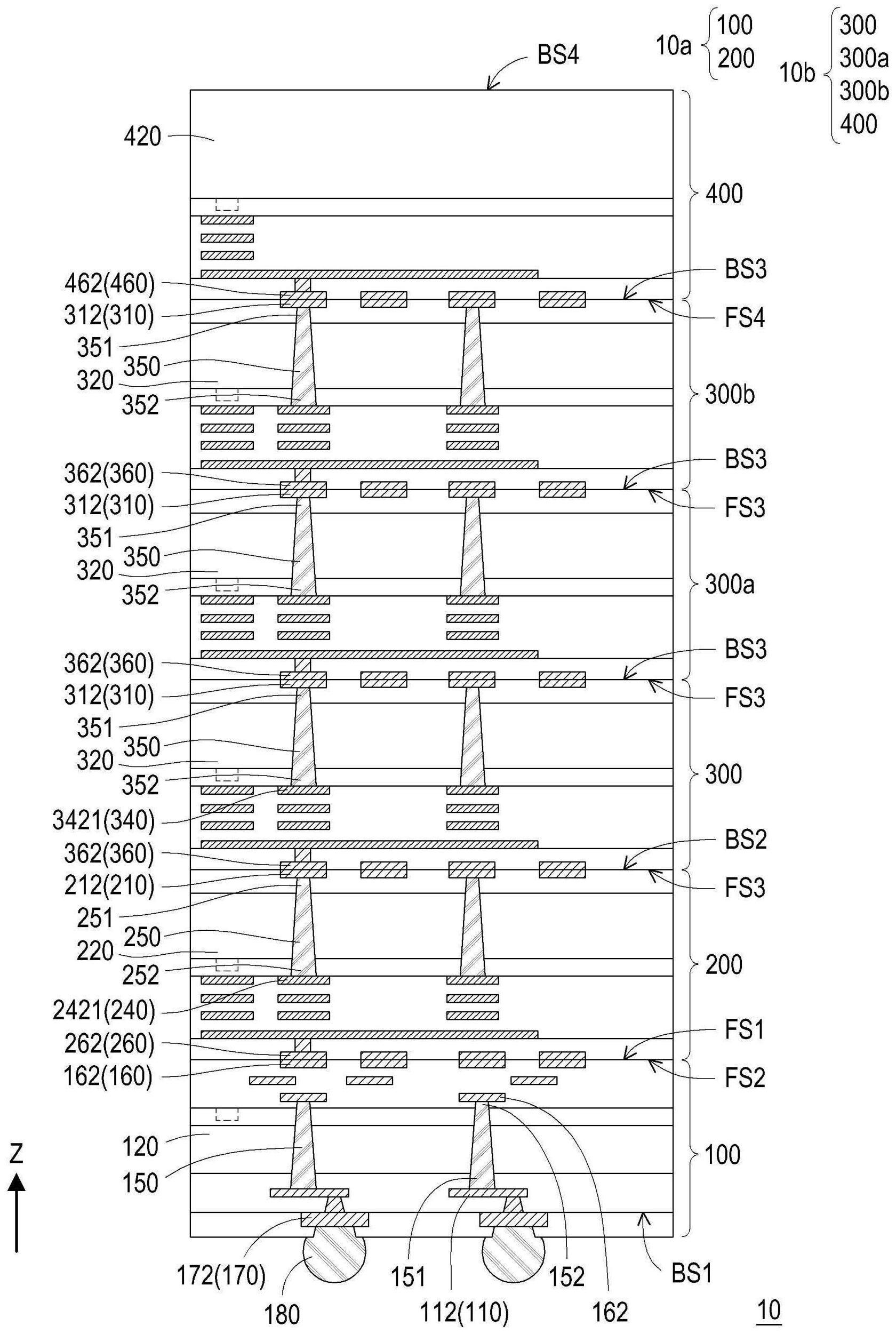

2、本发明的半导体封装结构包括控制单元与存储单元。控制单元包括垂直堆叠的第一晶片与第二晶片。存储单元设置于控制单元的第二晶片上。存储单元包括垂直堆叠的多个第三晶片与第四晶片。存储单元在半导体封装结构的法线方向上重叠于控制单元。

3、在本发明的一实施例中,上述的第一晶片包括第一接合结构、第一基底、第一硅穿孔以及第一连接结构。第一接合结构包括第一接合垫。第一基底设置于第一接合结构上。第一硅穿孔贯穿第一基底。第一连接结构设置于第一基底上且包括多层第一连接垫。第一硅穿孔的相对两端分别直接接触第一接合垫与第一连接结构中邻近第一基底的第一连接垫。

4、在本发明的一实施例中,上述的第二晶片包括第二接合结构、第二基底、第二内连线层、第二硅穿孔以及第二连接结构。第二接合结构包括第二接合垫。第二基底设置于第二接合结构上。第二内连线层设置于第二基底上且包括多层第二金属化图案。第二硅穿孔贯穿第二基底。第二连接结构设置于第二内连线层上且包括第二连接垫。第二硅穿孔的相对两端分别直接接触第二接合垫与多层第二金属化图案中的其中一层。

5、在本发明的一实施例中,上述的第一晶片中远离第一基底的第一连接垫直接接触第二晶片的第二连接垫。

6、在本发明的一实施例中,上述的第三晶片包括第三接合结构、第三基底、第三内连线层、第三硅穿孔以及第三连接结构。第三接合结构包括第三接合垫。第三基底设置于第三接合结构上。第三内连线层设置于第三基底上且包括多层第三金属化图案。第三硅穿孔贯穿第三基底。第三连接结构设置于第三内连线层上且包括第三连接垫。第三硅穿孔的相对两端分别直接接触第三接合垫与多层第三金属化图案中的其中一层。

7、在本发明的一实施例中,上述的第四晶片包括第四基底、第四内连线层以及第四连接结构。第四内连线层设置于第四基底上且包括多层第四金属化图案。第四连接结构设置于第四内连线层上且包括第四连接垫。远离控制单元的第三晶片的第三接合垫直接接触第四晶片的第四连接垫。

8、在本发明的一实施例中,上述的第二晶片的第二接合垫直接接触多个第三晶片中的其中一个第三晶片的第三连接垫。

9、在本发明的一实施例中,上述的第一晶片为系统芯片,第二晶片为逻辑芯片,且多个第三晶片与第四晶片为存储器芯片。

10、本发明的半导体封装结构的制作方法包括以下步骤:首先,形成控制单元,其中控制单元包括垂直堆叠的第一晶片与第二晶片。接着,形成存储单元,其中存储单元包括垂直堆叠的多个第三晶片与第四晶片。然后,将存储单元接合至控制单元的第二晶片上,以使存储单元在半导体封装结构的法线方向上重叠于控制单元。

11、在本发明的一实施例中,上述形成控制单元的方法包括以下步骤:将第二晶片的第二连接垫直接接合至第一晶片中远离第一基底的第一连接垫。

12、在本发明的一实施例中,上述形成存储单元的方法包括以下步骤:首先,将多个第三晶片中的其中一个第三晶片的第三接合垫直接接合至多个第三晶片中的另一个第三晶片的第三连接垫。接着,将第四晶片的第四连接垫直接接合至远离控制单元的第三晶片的第三接合垫。

13、在本发明的一实施例中,上述的多个第三晶片中的其中一个第三晶片的第三连接垫直接接合至第二晶片的第二接合垫。

14、基于上述,在本发明的实施例的半导体封装结构及其制作方法中,通过将存储单元以垂直堆叠的方式设置在控制单元,因而可缩短存储单元与控制单元之间的传输路径,进而可提升整体的工作效能。

15、为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

技术特征:

1.一种半导体封装结构,包括:

2.如权利要求1所述的半导体封装结构,其中所述第一晶片包括:

3.如权利要求2所述的半导体封装结构,其中所述第二晶片包括:

4.如权利要求3所述的半导体封装结构,其中所述第一晶片中远离所述第一基底的第一连接垫直接接触所述第二晶片的所述第二连接垫。

5.如权利要求3所述的半导体封装结构,其中所述第三晶片包括:

6.如权利要求5所述的半导体封装结构,其中所述第四晶片包括:

7.如权利要求5所述的半导体封装结构,其中所述第二晶片的所述第二接合垫直接接触所述多个第三晶片中的其中一个第三晶片的第三连接垫。

8.如权利要求1所述的半导体封装结构,其中所述第一晶片为系统芯片,所述第二晶片为逻辑芯片,且所述多个第三晶片与所述第四晶片为存储器芯片。

9.一种半导体封装结构的制作方法,包括:

10.如权利要求9所述的半导体封装结构的制作方法,其中形成所述控制单元的方法包括:

11.如权利要求9所述的半导体封装结构的制作方法,其中形成所述存储单元的方法包括:

12.如权利要求9所述的半导体封装结构的制作方法,其中所述多个第三晶片中的其中一个第三晶片的第三连接垫直接接合至所述第二晶片的第二接合垫。

技术总结

本发明公开一种半导体封装结构及其制作方法,其中该半导体封装结构包括控制单元与存储单元。控制单元包括垂直堆叠的第一晶片与第二晶片。存储单元设置于控制单元的第二晶片上。存储单元包括垂直堆叠的多个第三晶片与第四晶片。存储单元在半导体封装结构的法线方向上重叠于控制单元。

技术研发人员:吕俊麟,张守仁,陈启明

受保护的技术使用者:力晶积成电子制造股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!