多通道变频组件系统的制作方法

1.本技术属于北斗抗干扰导航系统技术领域,尤其涉及多通道变频组件系统。

背景技术:

2.卫星导航是现代战争中精确指挥、精确打击和精确兵力投送的关键。因此,最大限度地提高己方的导航能力,最大限度地遏制敌方的导航能力,对战争的进程是至关重要的。卫星导航抗干扰技术在现代战争中已广泛应用,抗干扰技术从战术上考虑可以采用两种完全不同的体制:一种是压制干扰;另一种是欺骗式干扰。

3.提高卫星导航抗干扰技术,经常使用多个阵元,来提高信号质量,相应射频部分需要使用多个通道。通道间的隔离度是影响抗干扰技术的一个重要指标。各通道间隔离度低就会干扰自身,造成通道性能下降,严重影响抗干扰性能。

技术实现要素:

4.为克服相关技术中存在的通道间隔离度低会干扰自身,造成通道性能下降,严重影响抗干扰性能的技术问题,本技术实施例提供了多通道变频组件系统。

5.本技术是通过如下技术方案实现的:第一方面,本技术实施例提供了一种多通道变频组件系统,包括:频综单元和接收预处理单元,频综单元与接收预处理单元连接。频综单元用于产生本振信号。接收预处理单元包括多组一一对应的低噪放单元和变频单元,低噪放单元用于对北斗信号进行低噪放处理,变频单元用于基于本振信号对低噪放单元处理后的信号进行变频处理。其中,各组低噪放单元和变频单元设置于不同的腔体中。

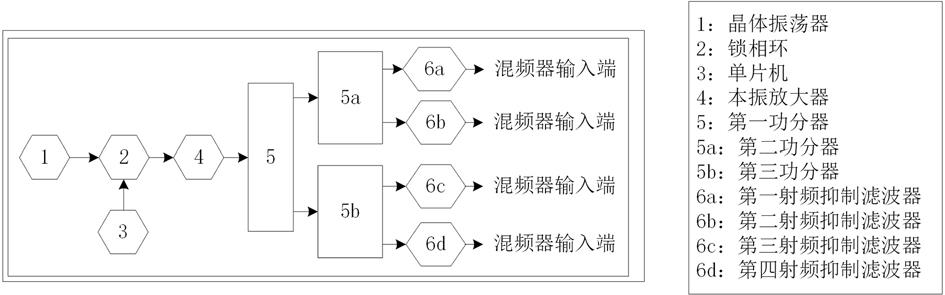

6.结合第一方面,在一些可能的实现方式中,频综单元包括:晶体振荡器、锁相环、单片机、本振放大器、第一功分器、第二功分器、第三功分器、第一射频抑制滤波器、第二射频抑制滤波器、第三射频抑制滤波器和第四射频抑制滤波器。晶体振荡器与锁相环的第一输入端连接,单片机与锁相环的第二输入端连接,本振放大器的输入端与锁相环的输出端连接,第一功分器的输入端与本振放大器的输出端连接,第一功分器的两个输出端分别与第二功分器和第三功分器连接,第二功分器的两个输出端分别与第一射频抑制滤波器和第二射频抑制滤波器连接,第三功分器的两个输出端分别与第三射频抑制滤波器和第四射频抑制滤波器连接,通过射频抑制滤波器连接输出本振信号。

7.结合第一方面,在一些可能的实现方式中,频综单元工作过程包括:晶体振荡器产生基准信号,基于单片机、锁相环和基准信号得到预输出本振信号,将预输出本振信号输入本振放大器;本振放大器对接收到的信号进行放大,得到第一放大信号;第一功分器、第二功分器和第三功分器对第一放大信号进行功分,得到四路本振信号;四路本振信号分别通过第一射频抑制滤波器、第二射频抑制滤波器、第三射频抑制滤波器和第四射频抑制滤波器输入接收预处理单元中。

8.结合第一方面,在一些可能的实现方式中,预处理单元包括:第一接收预处理单

元、第二接收预处理单元、第三接收预处理单元和第四接收预处理单元,其中,第一接收预处理单元、第二接收预处理单元、第三接收预处理单元和第四接收预处理单元的内部结构相同,第一接收预处理单元、第二接收预处理单元、第三接收预处理单元和第四接收预处理单元在不同的腔体中;第一接收预处理单元包括第一低噪放单元和第一变频单元;第二接收预处理单元包括第二低噪放单元和第二变频单元;第三接收预处理单元包括第三低噪放单元和第三变频单元;第四接收预处理单元包括第四低噪放单元和第四变频单元;第一低噪放单元、第二低噪放单元、第三低噪放单元和第四低噪放单元内部结构相同;第一变频单元、第二变频单元、第三变频单元和第四变频单元内部结构相同。

9.结合第一方面,在一些可能的实现方式中,第一低噪放单元包括:第一smp连接器、预选滤波器、限幅器、单片放大器和镜像抑制滤波器;第一smp连接器与预选滤波器连接,预选滤波器与限幅器连接,限幅器与单片放大器连接,单片放大器与镜像抑制滤波器连接。

10.结合第一方面,在一些可能的实现方式中,低噪放单元工作过程包括:射频信号通过第一smp连接器输入低噪放单元。预选滤波器抑制射频信号中的带外干扰、限幅器限制射频信号中强信号的输入,得到第一信号;单片放大器放大第一信号,得到第二信号;镜像抑制滤波器滤除第二信号中的镜像干扰,得到第三信号,将第三信号送入变频单元。

11.结合第一方面,在一些可能的实现方式中,第一变频单元包括混频器、低通滤波器、中频放大器、带通滤波器和第二smp连接器。混频器与镜像抑制滤波器连接,混频器与低通滤波器连接,低通滤波器与中频放大器连接,中频放大器与带通滤波器连接,带通滤波器与第二smp连接器连接;混频器还与射频抑制滤波器连接。

12.结合第一方面,在一些可能的实现方式中,变频单元工作过程包括:混频器根据第三信号和本振信号,混频出第一中频信号;低通滤波器滤去第一中频信号中的高频信号,得到第一低通信号;中频放大器放大第一低通信号,得到中频放大信号;带通滤波器对中频放大信号进行3db带宽限制,滤除带宽以外的信号,得到输出信号,通过第二smp连接器输出上述输出信号。

13.结合第一方面,在一些可能的实现方式中,多通道变频组件系统的盒体采用硬铝材质制造,每个独立腔体都有独立的盖板,盖板与盒体之间通过螺钉固定。

14.结合第一方面,在一些可能的实现方式中,螺钉之间间隔的距离小于等于10mm。

15.本技术实施例与现有技术相比存在的有益效果是:本技术实施例,接收预处理单元采用独立分腔设计,可以防止射频信号通过空间辐射到其他通道腔体内,提高了射频通道间高隔离度,从而提高射频通道间的抗干扰能力。

16.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本说明书。

附图说明

17.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

18.图1是本技术一实施例提供的多通道变频组件系统的示意图;

图2是本技术一实施例提供的频综单元示意图;图3是本技术一实施例提供的接收预处理单元示意图;图4是本技术一实施例提供的第一接收预处理单元示意图;图5是本技术一实施例提供的射频抑制滤波器400mhz带宽内频谱图;图6是本技术一实施例提供的低噪放单元电路图;图7是本技术一实施例提供的变频单元电路图;图8是本技术一实施例提供的频综单元电路图。

具体实施方式

19.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本技术实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本技术。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本技术的描述。

20.应当理解,当在本技术说明书和所附权利要求书中使用时,术语“包括”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

21.还应当理解,在本技术说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

22.如在本技术说明书和所附权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当...时”或“一旦”或“响应于确定”或“响应于检测到”。类似地,短语“如果确定”或“如果检测到[所描述条件或事件]”可以依据上下文被解释为意指“一旦确定”或“响应于确定”或“一旦检测到[所描述条件或事件]”或“响应于检测到[所描述条件或事件]”。

[0023]

另外,在本技术说明书和所附权利要求书的描述中,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0024]

在本技术说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本技术的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。

[0025]

卫星导航是现代战争中精确指挥、精确打击和精确兵力投送的关键。因此,最大限度地提高己方的导航能力,最大限度地遏制敌方的导航能力,对战争的进程是至关重要的。卫星导航抗干扰技术在现代战争中已广泛应用,抗干扰技术从战术上考虑可以采用两种完全不同的体制:一种是压制干扰;另一种是欺骗式干扰。

[0026]

提高卫星导航抗干扰技术,经常使用多个阵元,来提高信号质量,射频部分需要使用多个通道。通道间的隔离度是影响抗干扰技术的一个重要指标。各通道间隔离度低就会干扰自身,造成通道性能下降,严重影响抗干扰性能。

[0027]

基于上述问题,本技术实施例中的多通道变频组件系统,接收预处理单元采用独立分腔设计,可以防止射频信号通过空间辐射到其他通道腔体内,提高了射频通道间高隔

离度,从而提高射频通道间的抗干扰能力。

[0028]

图1是本技术一实施例提供的多通道变频组件系统示意图,参照图1,对该多通道变频组件系统的详述如下:多通道变频组件系统,包括:频综单元1001,用于产生本振信号,本振信号输入接收预处理单元2001;独立分腔的接收预处理单元2001,用于对北斗信号进行接收预处理操作,接收预处理单元2001包括低噪放单元和变频单元。

[0029]

上述多通道变频组件系统,接收预处理单元采用独立分腔设计,可以防止射频信号通过空间辐射到其他通道腔体内,提高了射频通道间高隔离度,从而提高射频通道间的抗干扰能力。

[0030]

图2是本技术一实施例提供的频综单元1001示意图,参照图2,对频综单元1001的详述如下:示例性的,频综单元1001包括:晶体振荡器1、锁相环2、单片机3、本振放大器4、第一功分器5、第二功分器5a、第三功分器5b、第一射频抑制滤波器6a、第二射频抑制滤波器6b、第三射频抑制滤波器6c和第四射频抑制滤波器6d。晶体振荡器1与锁相环2的第一输入端连接,单片机3与锁相环2的第二输入端连接,本振放大器4的输入端与锁相环2的输出端连接,第一功分器5的输入端与本振放大器4的输出端连接,第一功分器5的两个输出端分别与第二功分器5a和第三功分器5b连接,第二功分器5a的两个输出端分别与第一射频抑制滤波器6a和第二射频抑制滤波器6b连接,第三功分器5b的两个输出端分别与第三射频抑制滤波器6c和第四射频抑制滤波器6d连接,通过射频抑制滤波器连接输出本振信号。

[0031]

示例性的,频综单元1001工作过程包括:晶体振荡器1产生基准信号,基于单片机3、锁相环2和基准信号得到预输出本振信号,将预输出本振信号输入本振放大器4;本振放大器4对接收到的信号进行放大,得到第一放大信号;第一功分器5、第二功分器5a和第三功分器5b对第一放大信号进行功分,得到四路本振信号。四路本振信号分别通过第一射频抑制滤波器6a、第二射频抑制滤波器6b、第三射频抑制滤波器6c和第四射频抑制滤波器6d输入接收预处理单元中。

[0032]

图3是本技术一实施例提供的接收预处理单元2001示意图,参照图3,对接收预处理单元2001的详述如下:预处理单元2001包括:第一接收预处理单元a1、第二接收预处理单元a2、第三接收预处理单元a3和第四接收预处理单元a4,其中,第一接收预处理单元a1、第二接收预处理单元a2、第三接收预处理单元a3和第四接收预处理单元a4的内部结构相同,第一接收预处理单元a1、第二接收预处理单元a2、第三接收预处理单元a3和第四接收预处理单元a4在不同的腔体中。

[0033]

第一接收预处理单元a1包括第一低噪放单元101和第一变频单元102;第二接收预处理单元a2包括第二低噪放单元103和第二变频单元104;第三接收预处理单元a3包括第三低噪放单元105和第三变频单元106;第四接收预处理单元a4包括第四低噪放单元107和第四变频单元108。第一低噪放单元101、第二低噪放单元103、第三低噪放单元105和第四低噪放单元107内部结构相同;第一变频单元102、第二变频单元104、第三变频单元106和第四变频单元108内部结构相同。举例说明,图4是本技术一实施例提供的第一接收预处理单元a1示意图,参照图4,对第一接收预处理单元a1的详述如下:

示例性的,第一低噪放单元101包括:依次连接的第一smp连接器7、预选滤波器8、限幅器9、单片放大器10和镜像抑制滤波器11。

[0034]

因为第一低噪放单元101、第二低噪放单元103、第三低噪放单元105和第四低噪放单元107内部结构相同,所以第一低噪放单元101、第二低噪放单元103、第三低噪放单元105和第四低噪放单元107的工作过程也相同。

[0035]

示例性的,以第一低噪放单元101为例,低噪放单元的工作过程包括:射频信号通过第一smp连接器7输入低噪放单元;预选滤波器8抑制射频信号中的带外干扰、限幅器9限制射频信号中强信号的输入,得到第一信号;单片放大器10放大第一信号,得到第二信号;镜像抑制滤波器11滤除第二信号中的镜像干扰,得到第三信号,将第三信号送入第一变频单元102。

[0036]

示例性的,第一变频单元102包括:依次连接的混频器12、低通滤波器13、中频放大器14、带通滤波器15和第二smp连接器16。带通滤波器15与第一变频单元104中的第二smp连接器连接;混频器12还与频综单元1001的任一射频抑制滤波器连接,射频抑制滤波器输出的本振信号进入混频器12。

[0037]

因为第一变频单元102、第二变频单元104、第三变频单元106和第四变频单元108内部结构相同,所以第一变频单元102、第二变频单元104、第三变频单元106和第四变频单元108的工作过程也相同。

[0038]

示例性的,以第一变频单元102为例,变频单元的工作过程包括:混频器12根据第三信号和本振信号,混频出第一中频信号;低通滤波器13滤去第一中频信号中的高频信号,得到第一低通信号;中频放大器14放大第一低通信号,得到中频放大信号;带通滤波器15对中频放大信号进行3db带宽限制,滤除带宽以外的信号,得到输出信号,通过第二smp连接器16输出上述输出信号。

[0039]

示例性的,接收预处理单元2001采用独立分腔的设计和频综单元1001中加入射频抑制滤波器的设计,可以防止射频信号通过空间辐射到其他通道腔体内,提高了射频通道间高隔离度,从而提高射频通道间的抗干扰能力。

[0040]

示例性的,多通道变频组件系统的盒体采用硬铝材质制造,每个独立腔体都有独立的盖板,盖板与盒体之间通过螺钉固定。

[0041]

示例性的,螺钉之间间隔的距离小于等于10mm。

[0042]

示例性的,图5是本技术一实施例提供的射频抑制滤波器400mhz带宽内频谱图,从图中可以明显发现对射频信号1268mhz的抑制为33db,有效抑制通道间的射频输入信号,提高通道间隔离度。

[0043]

在一些实施例中,输入射频信号1268.52mhz,功率为-40dbm,中频输出信号为0dbm,通道总增益为40dbm。经低噪放输出为-20dbm。进入混频器后,混频器射频与本振信号隔离为20db,射频信号1268.52mhz进入频综单元(1222mhz)的功率为-40dbm,经过射频抑制滤波器30db的抑制即为-70dbm,再经过其他通道频综单元射频抑制滤波器,到达2通道混频器的射频信号功率为-100dbm,隔离度为80db,能够满足抗干扰整机系统应用。若不加射频抑制滤波器,在相同上述条件下,到达2通道混频器-40dbm,隔离度为20db,在实际应用中会严重影响抗干扰性能。

[0044]

示例性的,如图6所示,低噪放单元电路可以包括第一输入端g2、第一芯片x1(限幅

器gib1002)、第二芯片u2(滤波器qf242)、第三芯片u5(单片放大器fw1103)、第一馈电端g1、第四芯片u1(镜像抑制滤波器ta0862a)、第五芯片u3(单片放大器b5043)、第六芯片u4(镜像抑制滤波器ta0862a)和第一输出端g3。

[0045]

第一输入端g2的第一接口1连接电阻r5的第一端,第一输入端g2的第一接口1还与电感l3的第一端连接,第一输入端g2的第一接口1还与第一芯片x1的第一接口1连接,电阻r5的第二端接地,电感l3的第二端接地。

[0046]

第一芯片x1的第二接口2接地,第一芯片x1的第三接口3与电阻r6的第一端连接,第一芯片x1的第三接口3还与第二芯片u2的第二接口2连接,电阻r6的第二端接地。第二芯片u2的第一接口1、第三接口3、第四接口4和第六接口6接地,第二芯片u2的第五接口5与电容c6的第一端连接,第二芯片u2的第五接口5还与电容c10的第一端连接,电容c10的第二端接地,电容c6的第二端与第三芯片u5的第二接口2连接。

[0047]

第三芯片u5的第三接口3和第八接口8悬空,第三芯片u5的第四接口4、第五接口5、第六接口6和第九接口9接地,第三芯片u5的第一接口1与电感lra1的第一端连接。电感lar1的第二端与第一馈电端g1的第一接口1连接,电感lar1的第二端还与电容c3的第一端连接,电感lar1的第二端还与电阻ra1连接,电容c3的第二端接地,电阻ra1的第二端与电容ca1的第一端连接,电阻ra1的第二端还与电感l1的第一端连接,电容ca1第二端接地,电感l1的第二端与第三芯片u5的第七接口7连接,第三芯片u5的第七接口7还与电容c7的第一端连接,电容c7的第二端与电阻r8的第一端连接,电容c7的第二端还与第四芯片u1的第二接口2连接,电阻r8的第二端接地。

[0048]

第四芯片u1的第一接口1、第三接口3、第四接口4和第六接口6接地,第四芯片u1的第五接口5与电阻r7的第一端连接,电阻r7的第二端接地,第四芯片u1的第五接口5还与电容c8的第一端连接,电容c8的第二端与第五芯片u3的第三接口3连接,第五芯片u3的第二接口2和第四接口4接地,第五芯片u3的第一接口1与电容c9的第一端连接,第五芯片u3的第一接口1还与电感l2的第一端连接,电容c9的第二端与第六芯片u4的第二接口2连接,电感l2的第二端与电阻r1的第一端连接,电容c4和电容c5并联的第一端接地,电容c4和电容c5并联的第二端与电感l2的第二端连接,电阻r1的第二端与第一馈电端g1的第一接口1连接,电容c1和电容c2并联的第一端接地,电容c1和电容c2并联的第二端与第一馈电端g1的第一接口1连接,电阻r2和电阻r3并联的第一端接地,电阻r2和电阻r3并联的第二端与第一馈电端g1的第一接口1连接。

[0049]

第六芯片u4的第一接口1、第三接口3、第四接口4和第六接口6接地,第六芯片u4的第五接口5与电阻r4的第一端连接,第六芯片u4的第五接口5还与电阻r9的第一端连接,电阻r9的第二端接地,电阻r4的第二端与第一输出端g3的第一接口1连接,电阻r4的第二端还与电阻r10的第一端连接,电阻r10的第二端接地。

[0050]

示例性的,如图7所示,变频单元电路可以包括第二输出端g5、第七芯片u6(中频放大器pnw511)、第八芯片u7(混频器adl5350)、第一本振输入端lo1和第一射频输入端g4。

[0051]

第二输出端g5的第一接口1与电容cc2的第一端连接,电容cc2的第二端与电容cm6的第一端连接,电容cm6的第二端接地,电容cc2的第二端还与电感l11的第一端连接,电感l11的第二端与电容c24的第一端连接,电感l11的第二端还与电容cm7的第一端连接,电容cm7的第二端接地,电容c24的第二端与电感l12和电容c25并联的第一端连接,电容c24的第

二端还与电感lm1和电容cm1并联的第一端连接,电感lm1和电容cm1并联的第二端接地,电感l12和电容c25并联的第二端与电感lm2和电容cm4并联的第一端连接,电感lm2和电容cm4并联的第二端接地,电感l12和电容c25并联的第二端还与电感l9和电容c27并联的第一端连接,电感l9和电容c27并联的第二端与电感lm3和电容cm2并联的第一端连接,电感lm3和电容cm2并联的第二端接地,电感l9和电容c27并联的第二端还与电感l10和电容c26并联的第一端连接,电感l10和电容c26并联的第二端与电感lm4和电容cm3并联的第一端连接,电感lm4和电容cm3并联的第二端接地,电感l10和电容c26并联的第二端还与电容c23和电感l13并联的第一端连接,电容c23和电感l13并联的第二端与电感lm5和cm5并联的第一端连接,电感lm5和cm5并联的第二端接地,电容c23和电感l13并联的第二端还与电容c22的第一端连接,电容c22的第二端与电感l8的第一端连接,电容c22的第二端还与电容cm8的第一端连接,电容cm8的第二端接地,电感l8的第二端与电容c19的第一端连接,电感l8的第二端还与电容cm9的第一端连接,电容cm9的第二端接地,电容c19的第二端与第七芯片u6的第六接口6连接,电容c19的第二端还与电容cc1的第一端连接,电容cc1的第二端接地,电容c19的另一端还与电感l4的第一端连接,电感l4的第二端与电容c13和电容c14并联的第一端连接,电容c13和电容c14并联的第二端接地,电感l4的第二端还与电阻r11和电阻r12并联的第一端连接,电阻r11和电阻r12并联的第二端与电容c15的第一端连接,电容c15的第二端接地,电阻r11和电阻r12并联的第二端还与电容c11和电容c12并联的第一端连接,电容c11和电容c12并联的第二端接地,电容c15的第一端还与电感le3的第一端连接,电感le3的第二端与第八芯片u7的第六接口6连接,电感le3的第一端还与电容ce3的第一端连接,电容ce3的第二端接地。

[0052]

第七芯片u6的第一接口1、第二接口2、第四接口4和第五接口5接地,第七芯片u6的第三接口3与电容c18的第一端连接,电容c18的第二端与电阻r13的第一端连接,电容c18的第二端还与电阻r15的第一端连接,电阻r15的第二端接地,电阻r13的第二端与电阻r14的第一端连接,电阻r13的第二端还与电容c16的第一端连接,电容c16的第二端接地,电阻r14的第二端接地,电阻r13的第二端还与电感l6的第一端连接,电感l6的第二端与电感l5的第一端连接,电感l6的第二端还与电容c21的第一端连接,电容c21的第二端接地,电感l5的第二端与电容c17的第一端连接,电感l5的第二端还与电容c20第一端连接,电容c20的第二端接地,电容c17的第二端与电感le1和电容ce2并联的第一端连接,电感le1和电容ce2并联的第二端与第八芯片u7的第八接口8连接。

[0053]

第八芯片u7的第二接口2、第四接口4和第五接口5接地,第八芯片u7的第七接口7悬空,第八芯片u7的第一接口1与电容ce1的第一端连接,电容ce1的第二端与电感le2的第一端连接,电感le2的第二端与电阻r16的第一端连接,电阻r16的第二端与第一射频输入端g4的第一接口1连接,电感le2的第二端还与电阻rc1的第一端连接,电阻rc1的第二端接地,电阻ra2的第一端与第一射频输入端g4的第一接口1连接,电阻ra2的第二端接地。

[0054]

第八芯片u7的第三接口3与电感l7的第一端连接,电感l7的第二端与电阻r17的第一端连接,电阻r17的第二端与第一本振输入端lo1的第一接口1连接。

[0055]

示例性的,如图8所示,频综单元电路可以包括第九芯片u19(功分器scn-2-15+)、第十芯片u20(射频抑制滤波器ta0490a)、第三输出端j2、第十一芯片u18(射频抑制滤波器ta0490a)、第四输出端lo3、第十二芯片u16(功分器scn-3-16)、第五输出端g7、第十三芯片

u10(功分器scn-2-15+)、第十四芯片u12(射频抑制滤波器ta0490a)、第六输出端j1、第十五芯片u9(射频抑制滤波器ta0490a)、第七输出端lo2、第十六芯片u17(本振放大器sbb5089z)、第二馈电端g6、第十七芯片u15(射频抑制滤波器ta0490a)、第十八芯片u14(锁相环si4133-d-gt)、第十九芯片u22(单片机pic10f202-i/ot)、第八输出端g8、第二十芯片u13(时钟驱动sn74lvc1g04dbvr)、第二十一芯片u11(晶振e7009lf)、第二十二芯片u8(稳压器tps79333dbv)、第二十三芯片u21(时钟驱动sn74lvc1g04dbvr)和第九输出端g9。

[0056]

第九芯片u19的第一接口1、第三接口3和第五接口5接地,第九芯片u19的第四接口4与电阻r46的第一端连接,电阻r46的第二端与第九芯片u19的第六接口6连接,第九芯片u19的第四接口4还与电阻r47的第一端连接,电阻r47的第一端还与电阻r52的第一端连接,电阻r52的第二端接地,电阻r47的第二端与电容c50的第一端连接,电容c50的第二端与第十芯片u20的第二接口2连接,电阻r47的第二端还与电阻r53的第一端连接,电阻r53的第二端接地,第十芯片u20的第一接口1、第三接口3、第四接口4和第六接口6接地,第十芯片u20的第五接口5与第三输出端j2的第一接口1连接。

[0057]

第九芯片u19的第六接口6还与电阻r44的第一端连接,电阻r44的第一端还与电阻r39的第一端连接,电阻r39的第二端接地,电阻r44的第二端与电容c47的第一端连接,电容c47的第二端与第十一芯片u18的第二接口2连接,电阻r44的第二端还与电阻r40的第一端连接,电阻r40的第二端接地,第十一芯片u18的第一接口1、第三接口3、第四接口4和第六接口6接地,第十一芯片u18的第五接口5与第四输出端lo3的第一接口1连接。

[0058]

第九芯片u19的第二接口2与第十二芯片u16的第四接口4连接,第十二芯片u16的第一接口1和第三接口3接地,第十二芯片u16的第四接口4还与电阻r32的第一端连接,电阻r32的第二端与第十二芯片u16的的第六接口6连接,第十二芯片u16的第五接口5与第五输出端g7的第一接口1连接,第十二芯片u16的第五接口5还与电阻r36的第一端连接,电阻r36的第二端与第十二芯片u16的第四接口4连接,第十二芯片u16的第五接口5还与电阻r30的第一端连接,电阻r30的第二端与第十二芯片u16的第六接口6连接,第十二芯片u16的第六接口6还与第十三芯片u10的第二接口2连接。

[0059]

第十三芯片u10的第一接口1、第三接口3和第五接口5接地,第十三芯片u10的第四接口4与电阻r24的第一端连接,电阻r24的第二端与第十三芯片u10的第六接口6连接。

[0060]

第十三芯片u10的第四接口4还与电阻r26的第一端连接,电阻r26的第一端还与电阻r27的第一端连接,电阻r27的第二端接地,电阻r26的第二端与电容c33的第一端连接,电容c33的第二端与第十四芯片u12的第二接口2连接,电阻r26的第二端还与电阻r28的第一端连接,电阻r28的第二端接地,第十四芯片u12的第一接口1、第三接口3、第四接口4和第六接口6接地,第十四芯片u12的第五接口5与第六输出端j1的第一接口1连接。

[0061]

第十三芯片u10的第六接口6还与电阻r20的第一端连接,电阻r20的第一端还与电阻r18的第一端连接,电阻r18的第二端接地,电阻r20的第二端与电容c29的第一端连接,电容c29的第二端与第十五芯片u9的第二接口2连接,电阻r20的第二端还与电阻r19的第一端连接,电阻r19的第二端接地,第十五芯片u9的第一接口1、第三接口3、第四接口4和第六接口6接地,第十五芯片u9的第五接口5与第七输出端lo2的第一接口1连接。

[0062]

第十二芯片u16的第二接口2与电容c44的第一端连接,电容c44的第二端与第十六芯片u17的第三接口3连接,电容c44的第二端还与电感l14的第一端连接,电感l14的第二端

与第二馈电端g6的第一接口1连接,电感l14的第二端还与电容c32和电容c34并联的第一端连接,电容c32和电容c34并联的第二端接地,电感l14的第二端还与电阻r23的第一端连接,电阻r23的第二端接地,电感l14的第二端还与电容c31和电容c30并联的第一端连接,电容c31和电容c30并联的第二端接地,电感l14的第二端还与电容cc3和电容cc4并联的第一端连接,电容cc3和电容cc4并联的第二端接地。

[0063]

第十六芯片u17的第二接口2和第四接口4接地,第十六芯片u17的第一接口1与电容c43的第一端连接,电容c43的第二端与第十七芯片u15的第二接口2连接。

[0064]

第十七芯片u15的第一接口1、第三接口3、第四接口4和第六接口6接地,第十七芯片u15的第五接口5与电阻r31的第一端连接,第十七芯片u15的第五接口5还与电阻r42的第一端连接,电阻r42的第二端接地,电阻r31的第二端与电容c42的第一端连接,电阻r31的第二端还与电阻r41的第一端连接,电阻r41的第二端接地,电容c42的第二端与第十八芯片u14的第十一接口11连接。

[0065]

第十八芯片u14的第一接口1与第十九芯片u22的第一接口1连接,第十八芯片u14的第二接口2与第十九芯片u22的第三接口3连接,第十九芯片u22的第二接口2接地,第十八芯片u14的第三接口3、第六接口6、第九接口9、第十接口10、第十六接口16、第十八接口18和第二十一接口21接地,第十八芯片u14的第四接口4和第五接口5悬空,第十八芯片u14的第七接口7和第十八芯片u14的第八接口8连接,第十八芯片u14的第十二接口12与电容c39的第一端连接,电容c39的第二端与第十八芯片u14的第十四接口14连接,第十八芯片u14的第十二接口12还与电容c35的第一端连接,电容c35的第二端接地,第十八芯片u14的第十二接口12还与第二十二芯片u8的第五接口5连接,第十八芯片u14的第十二接口12还与电容cc6和电容cc5并联的第一端连接,电容cc6和电容cc5并联的第二端接地,第十八芯片u14的第十二接口12还与第二十一芯片u11的第四接口4连接,第十八芯片u14的第十二接口12还与第十八芯片u14的第十七接口17连接,第十八芯片u14的第十二接口12还与第十八芯片u14的第二十三接口23连接,第十八芯片u14的第十二接口12还与第十九芯片u22的第五接口5连接,第十八芯片u14的第十二接口12还与电容c38的第一端连接,电容c38的第二端与电容c41的第一端连接,电容c41的第二端与第十八芯片u14的第十四接口14连接,第十八芯片u14的第十三接口与第十九芯片u22的第六接口6连接。

[0066]

第十八芯片u14的第十五接口15与电容c45的第一端连接,电容c45的第二端与电阻r35的第一端连接,电阻r35的第二端与电阻r34的第一端连接,电阻r35的第二端还与电阻r43的第一端连接,电阻r43的第二端与第八输出端g8的第一接口1连接,电阻r34的第二端与电阻r33的第一端连接,电阻r33的第二端与第二十芯片u13的第四接口4连接,第二十芯片u13的第三接口3接地,第二十芯片u13的第五接口5与第二十二芯片u8的第五接口5连接,第二十芯片u13的第五接口5还与电容c36和电容c37并联的第一端连接,电容c36和电容c37并联的第二端接地,第二十芯片u13的第五接口5还与电阻r29的第一端连接,电阻r29的第二端与第二十芯片u13的第一接口1和第二接口2连接,第二十芯片u13的第一接口1和第二接口2连接,第二十芯片u13的第一接口1和第二接口2还与电容c40的第一端连接,电容c40的第二端与第二十一芯片u11的第三接口3连接,第二十芯片u13的第一接口1和第二接口2还与电阻r38的第一端连接,电阻r38的第二端接地。

[0067]

第二十一芯片u11的第二接口2接地,第二十一芯片u11的第一接口1与电阻r21的

第一端连接,电阻r21的第二端与第二十一芯片u11的第四接口4连接,第二十一芯片u11的第一接口1还与电阻r22的第一端连接,电阻r22的第二端与电阻r25的第一端连接,电阻r25的第二端接地,第二十一芯片u11的第三接口3还与电阻r37的第一端连接,电阻r37的第二端接地。

[0068]

第十八芯片u14的第十七接口17还与电容c46的第一端连接,电容c46的第二端接地。

[0069]

第十八芯片u14的第十九接口19与电阻r45的第一端连接,电容r45的第二端与第十八芯片u14的第二十接口20连接。

[0070]

第十八芯片u14的第二十二接口22与电感l16的第一端连接,电感l16的第二端与电容c48的第一端连接,电容c48的第二端与电阻r51的第一端连接,电阻r51的第二端与第二十三芯片u21的第一接口1和第二接口2连接,第二十三芯片u21的第一接口1和第二接口2还与电阻r54的第一端连接,电阻r54的第二端与第二十三芯片u21的第五接口5连接,第二十三芯片u21的第五接口5还与电容c55和电容c56并联的第一端连接,电容c55和电容c56并联的第二端接地,第二十三芯片u21的第四接口4与电阻r50的第一端连接,电阻r50的第二端与电阻r49的第一端连接,电阻r50的第二端还与电容c53的第一端连接,电容c53的第二端接地,电阻r49的第二端与电阻r48的第一端连接,电阻r49的第二端还与电容ca3的第一端连接,电容ca3的第二端接地,电阻r48的第二端与电容c52的第一端连接,电阻r48的第二端还与电容ca2的第一端连接,电容ca2的第二端接地,电容c52的第二端与电容c51的第一端连接,电容c51的第二端与第九输出端g9的第一接口1连接,第二十三芯片u21的第三接口3接地。

[0071]

第十八芯片u14第二十三接口23还与电容c49和c54并联的一端连接,电容c49和电容c54并联的第二端接地,第十八芯片u14第二十三接口23还与第二十三芯片u21的第五接口5连接。

[0072]

第十八芯片u14第二十四接口24与第十九芯片u22的第四接口4连接。

[0073]

第二十二芯片u8的第一接口1和第三接口3与第二馈电端g6的第一接口1连接,第二十二芯片u8的第二接口2接地,第二十二芯片u8的第四接口4与电容c28的第一端连接,电容c28的第二端接地。

[0074]

示例性的,本技术的主要技术指标如下:通道隔离度:≥75db;通道增益:40db

±

1db线性度:输入-40dbm频率间隔1mhz的双频信号,谐波抑制≥70dbc;噪声系数:≤1.5db。

[0075]

应理解,上述实施例中各步骤的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

[0076]

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述或记载的部分,可以参见其它实施例的相关描述。

[0077]

本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、或者计算机软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本技术的范围。

[0078]

在本技术所提供的实施例中,应该理解到,所揭露的装置/网络设备和方法,可以通过其它的方式实现。例如,以上所描述的装置/网络设备实施例仅仅是示意性的,例如,所述模块或单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通讯连接可以是通过一些接口,装置或单元的间接耦合或通讯连接,可以是电性,机械或其它的形式。

[0079]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0080]

以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1