一种相噪抵消高带宽单点调制小数锁相环架构

1.本发明属于数模混合电路领域,尤其涉及一种相噪抵消高带宽单点调制小数锁相环架构。

背景技术:

2.随着通信技术的发展,对降低芯片功耗以及减小芯片面积要求越来越高,传统的射频发射机是线性结构发射机,对电路的线性度要求较高,而且对i,q两路正交信号的质量要求也较高,电路模块功耗也较大。此外对于宽带信号,由于传统发射机的带宽受限,不适用于现在的高调制速率要求。因此以vco为调制源进行单点直接调制的需求也在逐渐加强,传统锁相环考虑到稳定性和滤除调制器量化噪声将带宽设置在100khz左右,而信号码率一般在远大于此截止频率,使传统锁相环在单点调制的应用受到了极大限制。

技术实现要素:

3.本发明目的在于提供一种相噪抵消高带宽单点调制小数锁相环架构,以解决传统小数锁相环结构中δ∑调制器输出的dsm控制码抖动引起的量化噪声(quantization noise)输出到锁相环f

out

、限制了锁相环环路带宽的的技术问题。

4.为解决上述技术问题,本发明的具体技术方案如下:

5.一种相噪抵消高带宽单点调制小数锁相环架构,包括鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器、δ∑调制器、数字时间转换器、数字时间转换器数字码计算模块;

6.所述的鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、分频器、数字时间转换器依次连接;

7.晶振信号f

ref

作为锁相环输入,压控振荡器输出振荡频率f

out

作为锁相环输出;振荡频率f

out

输入至分频器,分频器产生分频信号f

div

,分频信号f

div

输出到数字时间转换器时钟信号输入端与δ∑调制器时钟信号输入端;δ∑调制器输出控制码dsm到分频器的分频信号控制端和数字时间转换器数字码计算模块,数字时间转换器数字码计算模块输出量化控制码dtc_code到数字时间转换器的控制端;目标小数分频比n.frac输入数字时间转换器数字码计算模块与δ∑调制器的控制端。

8.进一步的,所述的环路滤波器为二阶无源低通滤波器。

9.进一步的,所述的δ∑调制器(18)为三阶级联噪声整型结构。

10.一种相噪抵消高带宽单点调制小数锁相环架构的工作方法,δ∑调制器的输出控制码dsm和预设的目标小数分频比n.frac输入数字时间转换器数字码计算模块,量化为量化控制码dtc_code输入到数字时间转换器,控制数字时间转换器对分频信号f

div

延时延迟δt产生输出信号f

del

,得到抵消δ∑调制器的抖动。

11.进一步的,所述的数字时间转换器将分频器的输出分频信号f

div

根据控制码dsm和目标小数分频比n.frac做差量化得到的量化控制码dtc_code延迟δt产生输出信号f

del

,具

体关系如下:

12.δt=(offset-∑(dsm-n.frac))/f

vco

13.其中,offset为延迟偏移量,f

vco

为控振荡器当前频率。

14.本发明的一种相噪抵消高带宽单点调制小数锁相环架构,具有以下优点:

15.本发明通过在分频器(divider)后增加一级数字时间转化器(digital time convertor,dtc),数字时间转化器将分频器的输出分频信号f

div

根据控制码dsm和目标小数分频比n.frac做差量化得到的量化控制码dtc_code延迟δt产生输出信号f

del

,有效抵消控制码dsm跳变产生的量化噪声,即消除对锁相环带宽的限制,使此锁相环架构可以应用于以vco为调制源的单点调制。

附图说明

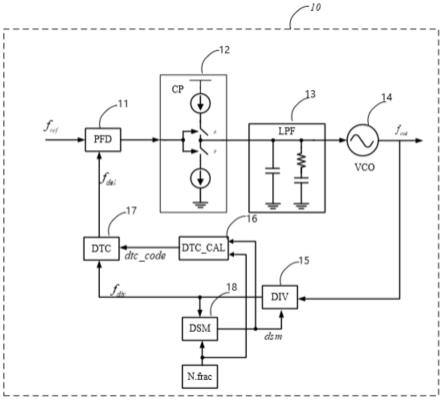

16.图1为本发明中带有相位噪声抵消技术的高带宽小数锁相环架构示意图;

17.图2为本发明的dtc数字码计算模块结构示意图;

18.图3(a)为传统锁相环锁定过程中vtune(vco调谐电压)的波形图(1mhz带宽);

19.图3(b)为本发明的频率综合器锁定过程中vtune(vco调谐电压)的波形图(1mhz带宽);

20.图4(a)为本发明以1mhz码率直接调制分频比情况下vtune的锁定情况;

21.图4(b)为本发明输入的调制信号波形;

22.图中标记说明:10、高带宽小数锁相环;11、鉴频鉴相器;12、电荷泵;13、环路滤波器;14、压控振荡器;15、分频器;16、dtc数字码计算模块;17、数字时间转换器;18、δ∑调制器;161、加法器;162、累加器;163、加法器;164、乘法器。

具体实施方式

23.为了更好地了解本发明的目的、结构及功能,下面结合附图,对本发明一种相噪抵消高带宽单点调制小数锁相环架构做进一步详细的描述。

24.本实例提供一种带有相位噪声抵消技术的高带宽小数锁相环10,其结构如图1所示,包括鉴频鉴相器11(phase frequency detector,pfd)、电荷泵12(charge pump,cp)、环路滤波器13(low pass filter,lpf)、压控振荡器14(voltage controlled oscillator,vco)、分频器15(div)、δ∑调制器18(delta_sigma modulator,dsm)、数字时间转换器17(digital time convertor,dtc)、数字时间转换器数字码计算模块16(dtc_cal);晶振信号f

ref

作为锁相环输入鉴频鉴相器11,鉴频鉴相器11输出相位差信号连接到电荷泵12的输入端转化为电流信号,电荷泵12输出电流信号连接到环路滤波器13转换为电压信号,控制压控振荡器14的振荡频率f

out

,振荡频率f

out

输入至分频器15,分频器15产生的分频信号f

div

,输出到数字时间转换器17时钟信号输入端与δ∑调制器18时钟信号输入端;δ∑调制器18输出控制码dsm到分频器15的分频信号控制端和数字时间转换器数字码计算模块16,数字时间转换器数字码计算模块16输出量化控制码dtc_code到数字时间转换器17的控制端;目标小数分频比n.frac输入数字时间转换器数字码计算模块16与δ∑调制器18的控制端。

25.所述环路滤波器13为二阶无源低通滤波器。所述的δ∑调制器18为三阶mash(级联噪声整形结构)结构。

26.在上述高带宽锁相环结构中,根据控制码dsm和目标小数分频比n.frac做差量化得到的量化控制码dtc_code,控制数字时间转换器17将分频器15的输出分频信号f

div

延迟某一时间间隔δt产生输出信号f

del

,有效抵消乃至消除控制码dsm跳变产生的量化噪声。

27.在锁相环稳定的情况下,控振荡器14当前频率f

vco

基本稳定在目标频带,但在传统小数锁相环中,因控制码dsm不断跳变,分频信号f

div

与晶振信号f

ref

始终无法严格对齐,δ∑调制器18产生的量化噪声将输出到压控振荡器14输出,恶化锁相环的相噪。

28.而所述的数字时间转换器17将分频器15的输出分频信号f

div

根据控制码dsm和目标分频比n.frac做差量化得到的量化控制码dtc_code延迟δt产生输出信号f

del

,具体关系如下:

29.δt=(offset-∑(dsm-n.frac))/f

vco

30.其中,offset为延迟偏移量,因三阶δ∑调制器18的输出范围是[-3,4],本架构offset取3;

[0031]fvco

为控振荡器14当前频率;

[0032]

基于此,相较于传统小数锁相环,加入数字时间转换器17将抑制控制码dsm跳变产生的量化噪声,进而达到拓宽锁相环带宽的设计目标。

[0033]

如图2所示,为数字时间转换器数字码计算模块16结构图,控制码dsm与目标分频比n.frac输入加法器161的加法端和减法端,加法器161输出到累加器162,累加器162输出到加法器163与目标小数分频比和当前分频比的差值offset做差,输出差值再输入到乘法器164得到δt,量化后控制数字时间转换器17对分频信号f

div

延迟。

[0034]

对本实例中带有相位噪声抵消技术的高带宽小数锁相环与传统小数锁相环锁定过程进行对比,结果如图三所示:其中,传统小数锁相环与本实例中带有相位噪声抵消技术的高带宽小数锁相环使用完全相同的模块,区别在于使数字时间转换器17对分频信号f

div

固定延时10ps,固定延时不影响锁相环的锁定,退化为传统的小数锁相环;由图3(b)可知,本实例中带有相位噪声抵消技术的高带宽小数锁相环锁定调谐电压vtune的纹波幅值为2mv,而传统小数锁相环在1mhz带宽的情况下(图3(a)),调谐电压vtune的纹波幅值为50mv,可见数字时间转换器17有效抵消控制码dsm跳变产生的量化噪声,与理论分析相符。

[0035]

如图(4)所示,本实例中相位噪声抵消技术的高带宽小数锁相环可以应用于以压控振荡器14为调制源的单点调制,以1mhz码率直接调制目标分频比,图4(b)为随机产生的分频比(含有小数分频比),图4(a)为对应的调谐电压vtune的输出波形,能够跟随分频比的变化而变化,锁定到对应的频带,可以得到结论,此锁相环可以应用于以vco为调制源的单点调制。

[0036]

可以理解,本发明是通过一些实施例进行描述的,本领域技术人员知悉的,在不脱离本发明的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效替换。另外,在本发明的教导下,可以对这些特征和实施例进行修改以适应具体的情况及材料而不会脱离本发明的精神和范围。因此,本发明不受此处所公开的具体实施例的限制,所有落入本技术的权利要求范围内的实施例都属于本发明所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1