一种振荡器加速电路、芯片及电子装置的制作方法

1.本创作是有关一种应用于振荡器的电路,尤指一种振荡器加速电路、芯片及电子装置。

背景技术:

2.电路系统中通常需要晶振来提供精准的时钟,晶振时钟相比较其他时钟振荡电路,比如rc张弛振荡器,拥有卓越的时钟稳定性以及低时钟抖动等性能,它通常用来作为倍频时钟或者频率合成的时钟源头。但是晶体振荡器起振时间比较长,比如mhz级别的晶体振荡器,其起振时间通常是毫秒量级,而khz级别的起振时间通常是秒量级,因此在某些需要快速唤醒晶振的情景下,比如用于蓝牙中,需要额外地加入快速启动电路用于加速晶体振荡器的起振过程。

技术实现要素:

3.本创作提供一种振荡器加速电路,用于加速晶体振荡器起振过程的加速电路。

4.本创作提供一种振荡器加速电路,用来加速振荡器的起振。所述振荡器具有输入端与输出端,所述电振荡器加速电路路包括反向放大器、反馈电阻器及加速电路。反向放大器具有输入端及输出端对应地耦接所述振荡器的所述输入端所述输出端,反馈电阻器耦接在所述振荡器的所述输入端及所述输出端之间。加速电路耦接在所述振荡器的所述输入端及所述输出端之间,其中所述加速电路用來提供系统函数,所述系统函数和并联连接之电阻器及电容器所提供的系统函数相同,其中所述电阻器的电阻值小于零。

5.在一些实施例中,所述加速电路包括第一n型晶体管、第二n型晶体管、第一电容器、第二电容器及第三电容器;所述第一n型晶体管的漏极耦接第一参考电压,所述第一n型晶体管的源极耦接第二参考电压,其中所述第一参考电压高于所述第二参考电压。所述第二n型晶体管的漏极耦接所述第一参考电压,所述第二n型晶体管的源极耦接所述第二参考电压,所述第二n型晶体管之栅极耦接于所述第一n型晶体管之漏极,所述第一n型晶体管之栅极耦接于所述第二n型晶体管之漏极。第一电容器耦接于所述第一n型晶体管之漏极和所述振荡器的所述输入端之间;第二电容器耦接于所述第二n型晶体管之漏极和所述振荡器的所述输出端之间。第三电容器耦接于所述第一n型晶体管之源极和所述第二n型晶体管之源极之间。

6.在一些实施例中,所述加速电路更包括第一电流源及一第二电流源;第一电流源耦接于所述第一n型晶体管的漏极和所述第一参考电压之间,第二电流源耦接于所述第二n型晶体管的漏级和所述第一参考电压之间。

7.在一些实施例中,所述第一电流源提供的电流值等于所述第二电流源提供的电流值。

8.在一些实施例中,所述加速电路更包括第三n型晶体管、第四n型晶体管及第五n型晶体管及第三电流源;所述第三n型晶体管的漏极耦接于自身的栅极,所述第三n型晶体管

的源极耦接所述第二参考电压。所述第四n型晶体管的栅极耦接所述第三n型晶体管的栅极,所述第四n型晶体管的漏极耦接所述第一n型晶体管的源极,所述第四n型晶体管的源极耦接所述第二参考电压。所述第五n型晶体管的栅极耦接所述第三n型晶体管的栅极,所述第五n型晶体管的漏极耦接所述第二n型晶体管的源极,所述第五n型晶体管的源极耦接所述第二参考电压。第三电流源耦接于所述第三n型晶体管的漏极和所述第一参考电压之间。

9.在一些实施例中,所述加速电路更包括第四电流源及第五电流源;所述第四电流源耦接于所述第一n型晶体管的源极和所述第二参考电压之间,第五电流源耦接于所述第二n型晶体管的源极和所述第二参考电压之间。

10.在一些实施例中,所述加速电路更包括第一电阻器及第二电阻器,第一电阻器耦接于所述第一n型晶体管的漏极和所述第一参考电压之间,第二电阻器耦接于所述第二n型晶体管的漏级和所述第一参考电压之间。

11.在一些实施例中,所述第一电阻器的电阻值等于所述第二电阻器的电阻值。

12.在一些实施例中,所述加速电路更包括第三n型晶体管、第四n型晶体管及第五n型晶体管及定电流源;所述第三n型晶体管的漏极耦接于自身的栅极,所述第三n型晶体管的源极耦接所述第二参考电压。所述第四n型晶体管的栅极耦接所述第三n型晶体管的栅极,所述第四n型晶体管的漏极耦接所述第一n型晶体管的源极,所述第四n型晶体管的源极耦接所述第二参考电压。所述第五n型晶体管的栅极耦接所述第三n型晶体管的栅极,所述第五n型晶体管的漏极耦接所述第二n型晶体管的源极,所述第五n型晶体管的源极耦接所述第二参考电压。所述定电流源耦接于所述第三n型晶体管的漏极和所述第一参考电压之间。

13.在一些实施例中,所述加速电路更包括第四电流源及第五电流源;所述第四电流源耦接在所述第一n型晶体管的源极和所述第二参考电压之间,所述第五电流源耦接在所述第二n型晶体管的源极和所述第二参考电压之间。

14.在一些实施例中,所述加速电路包括第一p型晶体管、第二p型晶体管、第一电容器、第二电容器及第三电容器;所述第一p型晶体管的源极耦接第一参考电压,所述第一p型晶体管的漏极耦接第二参考电压,其中所述第一参考电压高于所述第二参考电压。所述第二p型晶体管的源极耦接所述第一参考电压,所述第一p型晶体管的漏极耦接所述第二参考电压,所述第二p型晶体管之栅极耦接于所述第一p型晶体管之漏极,所述第一p型晶体管之一栅极耦接于所述第二p型晶体管之漏极。所述第一电容器耦接于所述第一p型晶体管之漏极和所述振荡器的所述输入端之间,所述第二电容器耦接于所述第二p型晶体管之漏极和所述振荡器的所述输出端之间,所述第三电容器耦接于所述第一p型晶体管之源极和所述第二p型晶体管之源极之间。

15.在一些实施例中,所述加速电路更包括第一电流源及第二电流源;所述第一电流源耦接于所述第一p型晶体管的漏极和所述第二参考电压之间,所述第二电流源耦接于所述第二p型晶体管的漏级和所述第二参考电压之间。

16.在一些实施例中,所述第一电流源提供的电流值等于所述第二电流源提供的电流值。

17.在一些实施例中,所述加速电路更包括第三p型晶体管、第四p型晶体管及第五p型晶体管及第三电流源;所述第三p型晶体管的源极耦接自身的栅极,所述第三n型晶体管的漏极耦接所述第二参考电压。所述第四p型晶体管的栅极耦接所述第三p型晶体管的栅极,

所述第四p型晶体管的漏极耦接所第一p型晶体管的源极,所述第四p型晶体管的源极耦接所述第一参考电压。所述第五p型晶体管的栅极耦接所述第三p型晶体管的栅极,所述第五p型晶体管的漏极耦接所述第二p型晶体管的源极,所述第五p型晶体管的源极耦接所述第一参考电压。第三电流源耦接于第三n型晶体管的漏极和所述第二参考电压之间。

18.在一些实施例中,所述加速电路更包括第四电流源及第五电流源;所述第四电流源耦接于所述第一p型晶体管的源极和所述第一参考电压之间,所述第五电流源耦接于所述第二p型晶体管的源极和所述第一参考电压之间。

19.在一些实施例中,所述加速电路更包括第一电阻器及第二电阻器,第一电阻器耦接于所述第一p型晶体管的漏极和所述第二参考电压之间,第二电阻器耦接于所述第二p型晶体管的漏级和所述第二参考电压之间。

20.在一些实施例中,所述第一电阻器的电阻值等于所述第二电阻器的电阻值。

21.在一些实施例中,所述加速电路更包括第三p型晶体管、第四p型晶体管、第五p型晶体管及定电流源;所述第三p型晶体管的漏极耦接于自身的栅极,所述第三p型晶体管的源极耦接所述第一参考电压。所述第四p型晶体管的栅极耦接所述第三p型晶体管的栅极,所述第四p型晶体管的漏极耦接所述第一p型晶体管的源极,所述第四p型晶体管的源极耦接所述第一参考电压。所述第五p型晶体管的栅极耦接所述第三p型晶体管的栅极,所述第五p型晶体管的漏极耦接所述第二p型晶体管的源极,所述第五p型晶体管的源极耦接所述第一参考电压。所述定电流源耦接于所述第三p型晶体管的漏极和所述第二参考电压之间。

22.在一些实施例中所述,加速电路更包括第四电流源及第五电流源,所述第四电流源耦接在所述第一参考电压和所述第一p型晶体管的源极之间,所述第五电流源耦接在所述第一参考电压和所述第二p型晶体管的源极之间。

23.在一些实施例中,当所述振荡器操作在低频时,所述电容器的电容值大于零,当所述振荡器操作在中频时,所述电容器的电容值小于零。

24.在一些实施例中,振荡器加速电路更包括计数器,耦接于所述振荡器的所述输出端及所述加速电路之间,所述计数器根据所述振荡器产生的振荡信号控制所述加速电路。本发明另提供一种芯片,包含前述的振荡器加速电路。

25.本创作提供一种电子装置,包含前述的芯片及耦接到所述芯片的所述振荡器。

26.本创作的振荡器加速电路,可以有效地让晶振快速地建立并达到稳定,从而缩短晶振的起振时间。

附图说明

27.下文实施方式将参照随附图式,以下将简单说明随附图式。

28.图1为本揭露的振荡信号产生电路的实施例的电路图。

29.图2为图1的振荡器的等效电路图。

30.图3为图1的振荡信号产生电路中的加速电路的第一实施例的电路图。

31.图4a为图3所示的第一n型晶体管、第二n型晶体管、第四n型晶体管、第五n型晶体管及第三电容器的阻抗分析图。

32.图4b为图3所示的第一n型晶体管、第二n型晶体管、第四n型晶体管第五n型晶体管、第一电容器、第二电容器及第三电容器的等效电路。

33.图4c为图4b的等效电路。

34.图5为图1的振荡信号产生电路中的加速电路的第二实施例的电路图。

35.图6为图1的振荡信号产生电路中的加速电路的第三实施例的电路图。

36.图7为图1的振荡信号产生电路中的加速电路的第四实施例的电路图。

37.图8为图1的振荡信号产生电路中的加速电路的第五实施例的电路图。

38.图9为图1的振荡信号产生电路中的加速电路的第六实施例的电路图。

39.图10为图1的振荡信号产生电路中的加速电路的第七实施例的电路图。

40.图11为图1的振荡信号产生电路中的加速电路的第八实施例的电路图。

具体实施方式

41.本揭露提供了数个不同的实施方法或实施例,可用于实现本发明的不同特征。为简化说明起见,本揭露也同时描述了特定零组件与布置的范例。请注意提供这些特定范例的目的仅在于示范,而非予以任何限制。举例而言,在以下说明第一特征如何在第二特征上或上方的叙述中,可能会包括某些实施例,其中第一特征与第二特征为直接接触,而叙述中也可能包括其他不同实施例,其中第一特征与第二特征中间另有其他特征,以致于第一特征与第二特征并不直接接触。此外,本揭露中的各种范例可能使用重复的参考数字和/或文字注记,以使文件更加简单化和明确,这些重复的参考数字与注记不代表不同的实施例与/或配置之间的关联性。再者,在以下描述中,「耦接」不仅表示组件直接彼此耦接,而且表示组件彼此耦接且另一组件插入在其间。

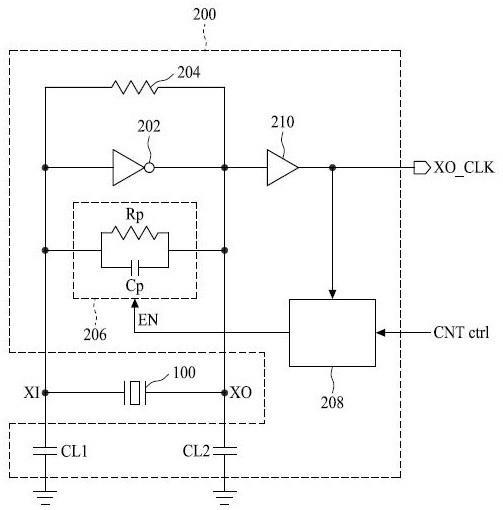

42.图1绘示本揭露振荡信号产生电路的实施例的电路图。请参照图1,振荡信号产生电路10包括振荡器100及振荡器加速电路200;振荡器100具有输入端xi和输出端xo,振荡器加速电路200耦接在振荡器100的输入端xi和输出端xo之间,用于让晶振快速地建立并达到稳定,从而缩短晶振的起振时间。在一些实施例中,振荡器100可以石英晶体实现。图2绘示本发明振荡器的等效电路图。请参照图2,振荡器100可包括电容器cm和cshunt、电感器lm和电阻器rm;电感器lm、电阻器rm和电容器cm串联连接后再与电容器cshunt并联连接,且电感器lm与电容器cshunt耦接的一端作为振荡器100的输入端xi,电容器cm和cshunt耦接的一端作为振荡器100的输出端xo。

43.复参照图1,振荡信号产生电路200包括反向放大器202、反馈电阻器204及加速电路206。反向放大器202的输入端耦接于振荡器100的输入端xi,反向放大器202的输出端耦接于振荡器100的输出端xo,用于为晶体起振提供能量;反向放大器202的增益的为负值,且反向放大器202的增益的绝对值大于1,可让振荡器100生成之信号放大。由主信号输出端xo_clk输出振荡信号作为例如外部电路所使用的时钟信号(clock pluse);在一些实施例中,振荡器100可生成正弦波。反馈电阻器204耦接在振荡器100的输入端xi和输出端xo之间。加速电路206耦接在振荡器100的输入端xi及输出端xo之间;换言之,加速电路206并联在反向放大器402两端。加速电路206用來提供系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。加速电路206能够为振荡器100提供额外的驱动能力,用以加快起振过程。

44.振荡器加速电路200更包括计数器208和缓冲器210;缓冲器210耦接在反向放大器202的输出端和主信号输出端xo_clk之间。计数器208耦接在缓冲器210的输出端;计数器

208通过对传递至主信号输出端xo_clk的振荡信号的数量进行周期计数,并在判定振荡器100进入稳定状态时关闭加速电路200;藉此,可以避免加速电路200带来的额外损耗以及负电容引起振荡器100的振荡频率发生偏移。缓冲器210可例如为方波缓冲器的脉冲波产生器。其中当振荡器100输出的正弦波的电平大于缓冲器210的阈值时,方波可具有一第一状态(高电平状态);当振荡器100提供的正弦波的电平小于缓冲器210的阈值时,方波可以具有第二状态(低电平状态)。在一些实施例中,缓冲器210产生的脉冲波可以是具有等于50%的占空比的矩形波,例如方波。在一些实施例中,由缓冲器210产生的脉冲波可以是占空比不是50%的矩形波。

45.振荡器加速电路200还可以包括第一负载电容器cl1和第二负载电容器cl2;第一负载电容器cl1耦接振荡器100的输入端xi,第二负载电容器cl2耦接振荡器100的输出端xo。调节第一负载电容器cl1和第二负载电容器cl2可用于减小图2所示并联谐振电路中的电容器cshunt以及走线电容对谐振频率的影响,提高振荡频率的精确度。图3为图1的振荡信号产生电路10中的加速电路206的第一实施例的电路图。如前所述,图3的加速电路用來提供所述系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。请参照图3,加速电路206可包括第一n型晶体管mn1、第二n型晶体管mn2、第一电容器c1、第二电容器c2及第三电容器cx。第一n型晶体管mn1、第二n型晶体管mn2形成交互耦合对,并与第三电容器cx配合提供加速电路206所需的负阻抗(negative impedance),以缩短振荡器100的起振时间;在一些实施例中,第一n型晶体管mn1和第二n型晶体管mn2具有相同几何尺寸(沟道宽度、沟道长度)和电气特性。更具体言之,第一n型晶体管mn1的漏极耦接第一参考电压vdd,源极耦接第二参考电压gnd,其中第一参考电压vdd高于第二参考电压gnd。第二n型晶体管mn2的漏极耦接第一参考电压vdd,源极耦接于第二参考电压gnd;第二n型晶体管mn2的栅极耦接于第一n型晶体管mn1的漏极,且第二n型晶体管mn2的漏极耦接于第一n型晶体管mn1的栅极。第三电容器cx耦接于第一n型晶体管mn1的源极和第二n型晶体管mn2的源极之间。

46.第一电容器c1耦接于第一n型晶体管mn1之漏极和振荡器100(如图1所示)的输入端x1之间,第二电容器c2耦接于第二n型晶体管mn2的漏极和振荡器100的输出端xo(如图1所示)之间;在一些实施例中,第一电容器c1和第二电容器c2具备相同的电容值。第一电容器c1和第二电容器c2的电容值分别小于第一负载电容器cl1和第二负载电容器cl2的电容值。第一电容器c1和第二电容器c2具备隔离直流电的功能,以避免对其他电路的直流偏置点造成影响。

47.加速电路206还可包括第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5、第一电流源i1、第二电流源i2及第三电流源i3。第三n型晶体管mn3、第四n型晶体管mn4和第五n型晶体管mn5和第三电流源i3构成电流镜,且第四n型晶体管mn4和第五n型晶体管mn5具有相同的几何尺寸(沟道宽度、沟道长度)和电气参数。第三n型晶体管mn3的漏极除了耦接于自身的栅极,还通过第三电流源i3耦接于第一参考电压vdd;第三n型晶体管mn3的源极接地。第四n型晶体管mn4的漏极耦接于第一n型晶体管mn1的源极,第四n型晶体管mn4的栅极耦接于第三n型晶体管mn3的栅极;第四n型晶体管mn4的源极接地。第五n型晶体管mn5的漏极耦接于第二n型晶体管mn2的源极,第五n型晶体管mn5的栅极耦接于第三n型晶体管mn3的栅极;第五n型晶体管mn5的源极接地。第一电流源i1跨接在第一参考电压vdd和第一n

型晶体管mn1的漏极之间,第二电流源i2跨接在第一参考电压vdd和第二n型晶体管mn2的漏极之间。在一些实施例中,第一电流源i1所提供的电流值等于第二电流源i2提供的电流值,以降低电路设计复杂度。在一些实施例中,第一电流源i1与第三电流源i3的电流比值等于第四n型晶体管mn4与第三n型晶体管mn3的几何尺寸(沟道宽度、沟道长度)比值;类似地,第二电流源i2与第三电流源i3的电流比值等于第五n型晶体管mn5与第三n型晶体管mn3的几何尺寸(沟道宽度、沟道长度)比值。

48.图4a为图3所示的第一n型晶体管mn1、第二n型晶体管mn2、第四n型晶体管mn4、第五n型晶体管mn5及第三电容器cx的阻抗分析图,图4b为图3所示的第一n型晶体管mn1、第二n型晶体管mn2、第四n型晶体管mn4、第五n型晶体管mn5、第一电容器、第二电容器及第三电容器cx的等效电路,图4c为图4b的等效电路。请参照图3及图4a至图4c;如前所述地,第一n型晶体管mn1和第二n型晶体管mn2具有相同几何尺寸和电气特性,第四n型晶体管mn4和第五n型晶体管mn5具有相同的几何尺寸和电气参数,以及第一电流源i1所提供的电流值等于第二电流源i2提供的电流值,这使得第一电流i1通过的路径相同于第二电流i2通过的路径,因此,以下关于第一n型晶体管mn1、第二n型晶体管mn2、第四n型晶体管mn4及第五n型晶体管mn5的阻抗特性分析只考虑一条电流支路(例如第一电流i1支路)上阻抗,因此图4a仅绘示第四n型晶体管mn4的漏极耦接于第一n型晶体管mn1的源极,且第三电容器cx调整为电容器2cx,电容器2cx的一端耦接于第四n型晶体管mn4的漏极和第一n型晶体管mn1的源极。图4a所示节点vo1对地的阻抗z1可表示如下:可表示如下:其中z为图4a所示之第四n型晶体管mn4的输出电阻器ro4与电容器2cx的并联阻抗,gm1为第一n型晶体管mn1的转导(transconductance),ro1为第一n型晶体管mn1的输出电阻器,且,第一电流源i1的输出阻抗无穷大,可以忽略,因此节点vo1的阻抗为。

49.振荡器100的主要工作频率处于中低频(即振荡频率为几万赫兹至几千万赫兹);当工作频率处于低频时,第三电容器cx的阻抗相远大于第四n型晶体管mn4的输出电阻器ro4和第五n型晶体管mn5的输出电阻器ro5,故阻抗z1可以下式表示之:因此,节点vo1和vo2间的等效阻抗可表示为:

当然,节点vo1和vo2间的等效阻抗可表示为:因此,振荡器100的输入端xi和输出端xo之间的等效阻抗为:因此,振荡器100的输入端xi和输出端xo之间的等效阻抗为:为必要条件。

50.或者,振荡器100的输入端xi和输出端xo之间的等效阻抗为:或者,振荡器100的输入端xi和输出端xo之间的等效阻抗为:为必要条件,gm2为第二n型晶体管mn2的转导。

51.当工作频率处于中频(比如1m~48m频段内)时,第三电容器cx的阻抗远小于第四n型晶体管mn4的输出电阻器ro4和第五n型晶体管mn5的输出电阻器ro5的电阻值,因此阻抗z1可以下式表示之:,,f为振荡频率则节点v01和v02之间的等效阻抗可表示为:或可表示为:从而振荡器100的输入端xi和输出端xo之间的等效阻抗为:从而振荡器100的输入端xi和输出端xo之间的等效阻抗为:从而振荡器100的输入端xi和输出端xo之间的等效阻抗为:

振荡器100的输入端xi和输出端xo之间的等效阻抗也表示为:振荡器100的输入端xi和输出端xo之间的等效阻抗也表示为:振荡器100的输入端xi和输出端xo之间的等效阻抗也表示为:由此可知,通过调节图3所示之第一电容器c1和第二电容器c2的大小,可以放大加速电路206的负电容值(negative capacitance),甚至起到电容值倍增的目的,最大程度的降低负载电容值。当以集成电路实现加速电路206时,因第一电容器c1和第二电容器c2提供之电容倍增效果允许采用电容值较小的第三电容器cx,从而降低芯片占用面积。

52.将cs、rs串联支路转换为并联支路,便可得到图1中的加速电路206的型态,即并联的rp、cp,其中的rp、cp,其中其中,ω为角频率(2πf);鉴于晶振的工作频率通常在中低频,有,所以有总言之,当晶振工作在低频下,加速电路206能提供一个负电阻以及一个正电容。负电阻能为振荡器100的起振提供更大的驱动能力,而正电容则会加大振荡器100的负载,因此在此应用场景中需要尽可能降低第一电容器c1和第二电容器c2的电容值,避免影响起振速度。在一些实施例中,第一电容器c1和第二电容器c2的电容值是pf级别。当振荡器100工作在中频段,加速电路206则提供一个负电阻值以及一个负电容值,降低振荡器100两端的负载电容值,从而进一步缩短起振时间。

53.应注意的是,本技术的加速电路206仅为示意用途,实际上可以对加速电路206进行变化,并得到实质相同的效果。举例来说,在某些实施例中,可以改变加速电路206中的晶体管的极性,并对应地调整电路;在某些实施例中,可以改变加速电路206的电流源的配置方式。以下列举三个不同的实施例做为说明之用。

54.图5为图1的振荡信号产生电路中的加速电路的第二实施例的电路图。请参阅图3

及图5;如前所述,图5的加速电路用來提供所述系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。在图3中,加速电路206以第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5及第三电流源i3构成电流镜以提供在第一n型晶体管mn1源极的电流i4及第二n型晶体管mn2源极的电流i5。为了有效地缩减电路体积及降低成本,可直接于第一n型晶体管mn1源极和第二n型晶体管mn2的源极分别设置第四电流源ia和第五电流源ib提供电流i4和i5。图6为图1的振荡信号产生电路中的加速电路的第三实施例的电路图。如前所述,图6的加速电路用來提供所述系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。请参照图5,加速电路206可包括第一p型晶体管mp1、第二p型晶体管mp2、第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5、第一电容器c1、第二电容器c2、第三电容器cx、第一电流源i1及第二电流源i2。第一p型晶体管mp1、第二p型晶体管mp2形成交互耦合对,并与第三电容器cx配合提供加速电路206所需的负阻抗。详言之,第一p型晶体管mp1的漏极通过第一电流源i1耦接第二参考电压gnd,栅极通过第二电流源i2耦接第二参考电压gnd。第二p型晶体管mp2的漏极耦接于第一p型晶体管mp1的栅极,且第二p型晶体管mp2的栅极耦接于第一p型晶体管mp1的漏极。在一些实施例中,第一p型晶体管mp1和第二p型晶体管mp2具有相同几何尺寸(沟道宽度、沟道长度)和电气特性,并且第一参考电压vdd高于第二参考电压gnd。第三电容器cx耦接于第一p型晶体管mp1的源极和第二p型晶体管mp2的源极之间。

55.第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5和第三电流源i3构成电流镜;其中,第四p型晶体管mp4和第五p型晶体管mp5具有相同的几何尺寸和电气参数。以下详细说明第三至第五p型晶体管mp3-mp5的耦接方式。第三p型晶体管mp3、第四p型晶体管mp4和第五p型晶体管mp5的源极分别耦接至第一参考电压vdd;第三p型晶体管mp3的栅极耦接至其漏极,漏极则通过第三电流源i3耦接于第二参考电压gnd。第四p型晶体管mp4的栅极耦接于第三p型晶体管mp3的栅极,第四p型晶体管mp4漏极耦接于第一p型晶体管mp1的源极。第五p型晶体管mp5的栅极耦接于第三p型晶体管mp3的栅极,第五p型晶体管mp5的漏极耦接于第二p型晶体管mp2的源极。由第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5和第三电流源i3构成电流镜可改由配置在第一p型晶体管mp1源极的第四电流源ia和配置在第二p型晶体管mp2源极的第五电流源ib实现之,如图7所示。

56.复参阅图6,第一电容器c1耦接于第一p型晶体管mp1之漏极和振荡器100(如图1所示)的输入端x1之间,第二电容器c2耦接于第二p型晶体管mp2的漏极和振荡器100的输出端xo(如图1所示)之间;在一些实施例中,第一电容器c1和第二电容器c2具备相同的电容值。第一电容器c1和第二电容器c2除了具备隔离直流电的功能,还能进一步地放大加速电路206的负电容值。

57.图8为图1的振荡信号产生电路中的加速电路的第五实施例的电路图。如前所述,图8的加速电路用來提供所述系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。请参照图8,加速电路206可包括第一n型晶体管mn1、第二n型晶体管mn2、第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5、第一电容器c1、第二电容器c2、第三电容器cx、定电流源i、第一电阻器r1和第二电阻器r2。第一n型晶体管mn1的漏极通过第一电阻器r1耦接第一参考电压vdd,栅极通过第二

电阻器r2耦接第一参考电压vdd;其中,第一参考电压vdd高于第二参考电压gnd。第二n型晶体管mn2的漏极耦接于第一n型晶体管mn1的栅极,第二n型晶体管mn2的栅极耦接于第一n型晶体管mn1的漏极。第一电阻器r1和第二电阻器r2具有相同的电阻值。在一些实施例中,第一n型晶体管mn1和第二n型晶体管mn2具有相同几何尺寸(沟道宽度、沟道长度)和电气特性。第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5和定电流源i构成电流镜。更具体言之,第三n型晶体管mn3的漏极除了耦接于自身的栅极,还通过定电流源i耦接至第一参考电压vdd;第三n型晶体管mn3、第四n型晶体管mn4和第五n型晶体管mn5的源级分别耦接至第二参考电压gnd。第四n型晶体管mn4和第五n型晶体管mn5的栅极分别耦接于第三n型晶体管mn3的栅极,第四n型晶体管mn4漏极耦接于第一n型晶体管mn1的源极,第五n型晶体管mn5的漏极耦接于第二n型晶体管mn2的源极;其中,第四n型晶体管mn4和第五n型晶体管mn5可具有相同的几何尺寸和电气参数。简言之,加速电路206以第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5及定电流源i构成电流镜以提供在第一n型晶体管mn1源极的电流i4及第二n型晶体管mn2源极的电流i5。请参照图3及图8,图8所示内容以第一电阻器r1和第二电阻器r2取代图3中的第一电流源i1和第二电流源i2,可摆脱第二电流源i2的电流值须等于第一电流源i1的电流值,以及电流i4和i5同时等于第一电流源i1的电流值的约束,在阻值的选取上会更灵活。在理想情况下,第一电流源i1和第二电流源i2的内阻为无穷大;因此,以第一电阻器r1和第二电阻器r2取代第一电流源i1和第二电流源i2虽然能够有效地降低电路配置成本,但会减小等效的负阻抗,从而使得加速电路206对加速晶振起振的效果没那么显着。

58.此外,由第三n型晶体管mn3、第四n型晶体管mn4、第五n型晶体管mn5和定电流源i构成电流镜可改由配置在第一n型晶体管mn1源极的第四电流源ia和配置在第二n型晶体管mn2源极的第五电流源ib实现之,如图9所示。

59.复参阅图8,第一电容器c1耦接于第一n型晶体管mn1之漏极和振荡器100(如图1所示)的输入端x1之间,第二电容器c2耦接于第二n型晶体管mn2的漏极和振荡器100的输出端xo(如图1所示)之间;在一些实施例中,第一电容器c1和第二电容器c2具备相同的电容值。第一电容器c1和第二电容器c2除了具备隔离直流电的功能,还能进一步地放大加速电路206的负电容值。第三电容器cx耦接于第一n型晶体管mn1的源极和第二n型晶体管mn2的源极之间,并与第一n型晶体管mn1、第二n型晶体管mn2共同形成之交互耦合对配合提供加速电路206所需的负阻抗。

60.图10为图1的振荡信号产生电路中的加速电路的第七实施例的电路图。如前所述,图10的加速电路用來提供所述系统函数,所述系统函数和并联连接之电阻器rp及电容器cp所提供的系统函数相同;其中,电阻器rp的电阻值小于零。请参照图10,加速电路206耦接在一第一参考电压vdd和第二参考电压gnd之间,并可包括第一p型晶体管mp1、第二p型晶体管mp2、第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5、第一电容器c1、第二电容器c2、第三电容器cx、电流源i、第一电阻器r1及第二电阻器r2。如图7所示,第一p型晶体管mp1的漏极通过第一电阻器r1连接至第二参考电压gnd,第一p型晶体管mp1的栅极通过第二电阻器r2连接至第二参考电压gnd;其中,第一参考电压vdd高于第二参考电压gnd。第二p型晶体管mp2的栅极耦接于第一p型晶体管mp1的漏极,第二p型晶体管mp2的漏极耦接于第一p型晶体管mp1的栅极;第一电阻器r1的电阻值等于第二电阻器r2的电阻值。在一些实施例

中,第一p型晶体管mp1和第二p型晶体管mp2具有相同几何尺寸(沟道宽度、沟道长度)和电气特性。

61.第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5和定电流源3构成电流镜。更具体言之,第三p型晶体管mp3的漏极除了耦接于自身的栅极外,还通过定电流源i耦接至第二参考电压gnd;第三p型晶体管mp3、第四p型晶体管mp4和第五p型晶体管mp5的源级分别耦接至第一参考电压vdd。第四p型晶体管mp4和第五p型晶体管mp5的栅极分别耦接于第三p型晶体管mp3的栅极,第四p型晶体管mp4漏极耦接于第一p型晶体管mp1的源极,第五p型晶体管mp5的漏极耦接于第二p型晶体管mp2的源极;其中,第四p型晶体管mp4和第五p型晶体管mp5可具有相同的几何尺寸和电气参数。由第三p型晶体管mp3、第四p型晶体管mp4、第五p型晶体管mp5和定电流源i构成电流镜可改由配置在第一p型晶体管mp1源极的第四电流源ia和配置在第二p型晶体管mp2源极的第五电流源ib实现之,如图11所示。

62.复参阅图10,第一电容器c1耦接于第一p型晶体管mp1之漏极和振荡器100(如图1所示)的输入端x1之间,第二电容器c2耦接于第二p型晶体管mp2的漏极和振荡器100的输出端xo(如图1所示)之间;在一些实施例中,第一电容器c1和第二电容器c2具备相同的电容值。第三电容器cx耦接于第一p型晶体管mp1的源极和第二p型晶体管mp2的源极之间,并与第一p型晶体管mp1、第二p型晶体管mp2共同形成之交互耦合对配合提供加速电路206所需的负阻抗;第一电容器c1和第二电容器c2除了具备隔离直流电的功能,还能进一步地放大加速电路206的负电容值。

63.上文的叙述简要地提出了本发明某些实施例的特征,而使得本发明所属技术领域具有通常知识者能够更全面地理解本揭示内容的多种态样。本发明所属技术领域具有通常知识者当可明了,其可轻易地利用本揭示内容为基础,来设计或更动其他制程与结构,以实现与此处所述的实施方式相同的目的和/或达到相同的优点。本发明所属技术领域具有通常知识者应当明白,这些均等的实施方式仍属于揭示内容的精神与范围,且其可进行各种变更、替代与更动,而不会悖离揭示内容的精神与范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1