三维AND快闪存储器元件及其制造方法与流程

本发明是有关于一种半导体元件及其制造方法,且特别是有关于一种快闪存储器元件及其制造方法。

背景技术:

1、非易失性存储器具有可使得存入的数据在断电后也不会消失的优点,因此广泛采用于个人计算机和其他电子设备中。目前业界较常使用的三维存储器包括或非门(nor)存储器以及与非门(nand)存储器。此外,另一种三维存储器为与门(and)存储器,其可应用在多维度的存储器阵列中而具有高集成度与高面积利用率,且具有操作速度快的优点。因此,三维存储器元件的发展已逐渐成为目前的趋势。然而,仍存在许多与三维存储器元件相关的挑战。

技术实现思路

1、本发明提出一种三维and快闪存储器元件可以使得避免读取错误。

2、本发明提出一种三维and快闪存储器元件的制造方法可以与现有工艺整合而在存储单元阵列中形成做为开关的晶体管,以避免错误读取。

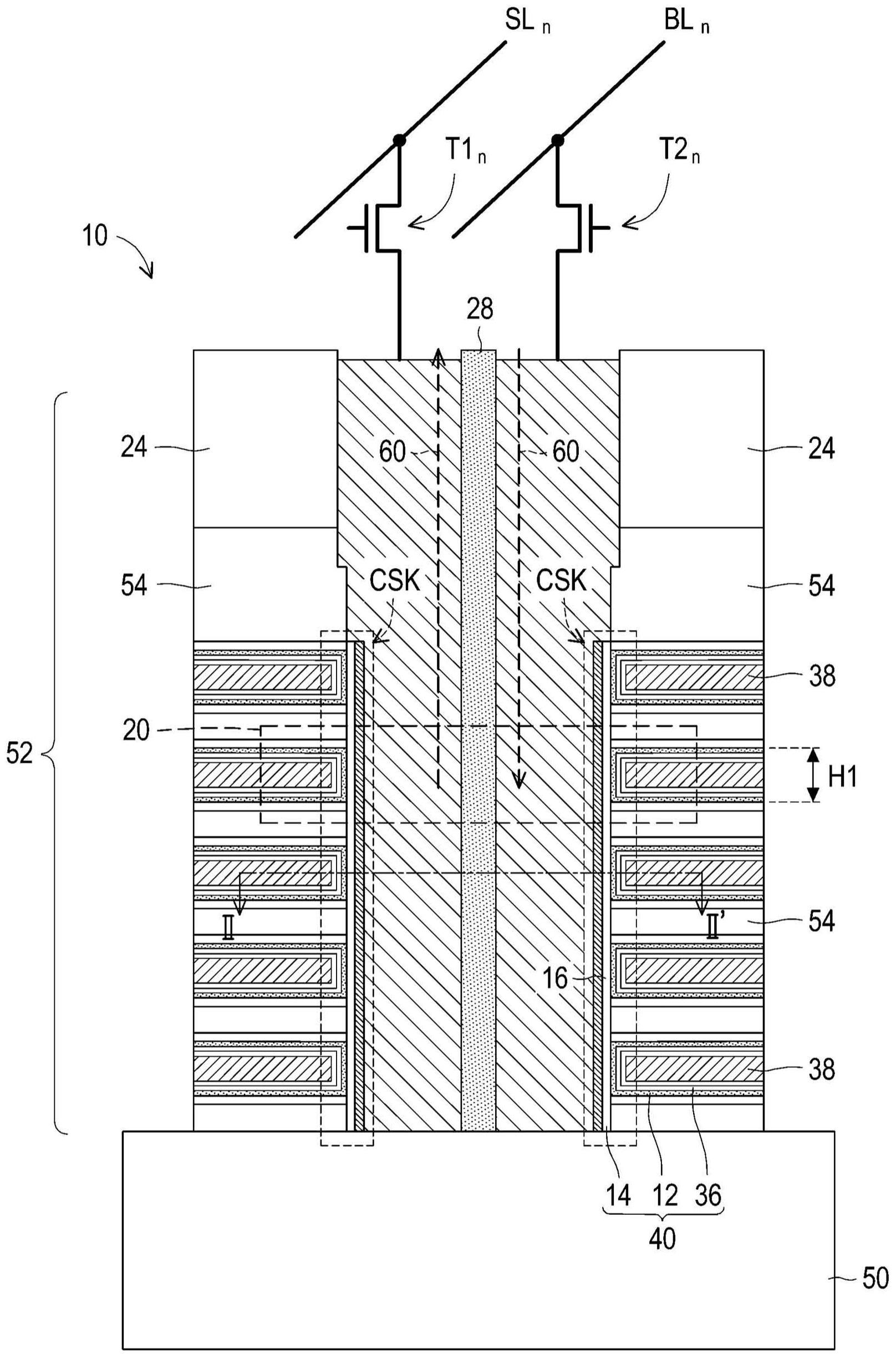

3、依据本发明实施例的一种三维and快闪存储器元件,包括栅极堆叠结构、通道柱、源极柱与漏极柱、电荷储存结构、第一晶体管与第二晶体管。所述栅极堆叠结构位于介电基底上,其中所述栅极堆叠结构包括彼此交替堆叠的多个栅极层与多个绝缘层。所述通道柱延伸穿过所述栅极堆叠结构。源极柱与漏极柱,位于所述通道柱内,且与所述通道柱电性连接。所述电荷储存结构,位于所述多个栅极层与所述通道柱之间。所述第一晶体管位于所述栅极堆叠结构上方,电性连接所述漏极柱。所述第二晶体管位于所述栅极堆叠结构上方,电性连接所述源极柱。

4、依据本发明实施例的一种三维and快闪存储器元件,包括:第一区块、第二区块、位线与源极线。所述第一区块包括多个第一存储单元、第一晶体管与第二晶体管。所述多个第一存储单元,彼此并联成第一存储器串。所述第一晶体管,与所述第一存储器串的漏极柱串连。所述第二晶体管,与所述第一存储器串的源极柱串连。所述第二区块包括多个第二存储单元、第三晶体管与第四晶体管。所述多个第二存储单元,彼此并联成第二存储器串。所述第三晶体管与所述第二存储器串的漏极柱串连。所述第四晶体管与所述第二存储器串的源极柱串连。所述位线连接所述第一区块的所述第一晶体管的漏极区与所述第二区块的所述第三晶体管的漏极区。所述源极线连接所述第一区块的所述第二晶体管的源极区与所述第二区块的所述第四晶体管的源极区。

5、依据本发明实施例的一种三维and快闪存储器元件的制造方法,包括:形成第一堆叠结构于介电基底上,其中所述第一堆叠结构包括彼此交替堆叠的多个第一中间层与多个第二绝缘层。形成通道柱延伸穿过所述第一堆叠结构。在所述通道柱内形成与所述通道柱电性连接的源极柱与漏极柱。形成第二堆叠结构于所述第一堆叠结构上,其中所述第二堆叠结构包括彼此交替堆叠的多个第二绝缘层与至少一第二中间层。形成第一通道插塞与第二通道插塞伸穿过所述第二堆叠结构,其中所述第一通道插塞着陆在且电性连接所述漏极柱,所述第二通道插塞着陆在且电性连接所述源极柱。局部地移除所述多个第一中间层与所述至少一第二中间层,以形成多个第一水平开口以及至少一第二水平开口。形成栅极介电层于所述至少一第二水平开口中。形成多个第一栅极层于所述多个第一水平开口中,并形成至少一第二栅极层于所述至少一第二水平开口剩余的空间中。形成多个电荷储存结构,位于所述多个第一栅极层与所述通道柱之间。形成第一掺杂区于所述第一通道插塞中,并形成第二掺杂区于所述第二通道插塞中。

6、本发明实施例的三维and快闪存储器元件的制造方法可以与现有工艺整合而在存储单元阵列形成多个晶体管。这些晶体管可以做为开关的,以避免错误读取。

技术特征:

1.一种三维and快闪存储器元件,包括:

2.根据权利要求1所述的三维and快闪存储器元件,其中所述第一晶体管与所述第二晶体管分别为垂直晶体管。

3.根据权利要求1所述的三维and快闪存储器元件,其中所述第一晶体管与所述第二晶体管分别为第一全环绕式晶体管与第二全环绕式晶体管。

4.根据权利要求3所述的三维and快闪存储器元件,其中

5.根据权利要求4所述的三维and快闪存储器元件,其中所述第一栅极介电层与所述电荷储存结构彼此分离;所述第二栅极介电层与所述电荷储存结构彼此分离。

6.根据权利要求1所述的三维and快闪存储器元件,其中所述第一晶体管的所述第一通道插塞为未掺杂的半导体或具有掺质且导电型不同于所述第一源极区的掺质的导电型的半导体。

7.根据权利要求6所述的三维and快闪存储器元件,其中所述第二晶体管的所述第二通道插塞为未掺杂的半导体、具有掺质且导电型不同于所述第二源极区的掺质的导电型的半导体或具有掺质且导电型相同于所述第二源极区的掺质的导电型的半导体。

8.根据权利要求1所述的三维and快闪存储器元件,其中所述第一晶体管与所述第二晶体管分别为具有多个全环绕式栅极的垂直晶体管。

9.一种三维and快闪存储器元件,包括:

10.一种三维and快闪存储器元件的制造方法,包括:

11.根据权利要求10所述的三维and快闪存储器元件的制造方法,还包括:

技术总结

本发明提供了一种三维AND快闪存储器元件,包括栅极堆叠结构、通道柱、源极柱与漏极柱、电荷储存结构、第一晶体管与第二晶体管。所述栅极堆叠结构位于介电基底上,其中所述栅极堆叠结构包括彼此交替堆叠的多个栅极层与多个绝缘层。所述通道柱延伸穿过所述栅极堆叠结构。源极柱与漏极柱,位于所述通道柱内,且与所述通道柱电性连接。所述电荷储存结构,位于所述多个栅极层与所述通道柱之间。所述第一晶体管位于所述栅极堆叠结构上方,电性连接所述漏极柱。所述第二晶体管位于所述栅极堆叠结构上方,电性连接所述源极柱。

技术研发人员:胡志玮,叶腾豪

受保护的技术使用者:旺宏电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!