一种基于SAW和BAW并列叠放的滤波器芯片及其制造工艺的制作方法

一种基于saw和baw并列叠放的滤波器芯片及其制造工艺

技术领域

1.本发明属于mems芯片制造技术领域,尤其涉及一种基于saw和baw并列叠放的滤波器芯片及其制造工艺。

背景技术:

2.随着当今集成电路的迅速发展,大规模集成电路已逐渐的出现在人们的视野当中,同时随着科技时代的进步,手机和自动汽车等电子技术设备也逐一亮相,5g信号也相应的被设计出来。其5g信号相对原有的4g信号的优势在于它的频段会更大更宽且信号传输运行的速度更快,带宽外频段的抑制能力更强。

3.目前滤波器芯片的分类可分为saw类型和baw类型。saw,即表面声谐振器(surface acoustic wave),利用声表面波来处理和传播信号的无源器件;baw,即薄膜体声谐振器(bulk acoustic wave),以纵波或横波在固体内部传递的形式来处理声波信号。

4.saw和baw两种滤波器芯片分别适配不同低中高频段,只在相应的频段中有优势,并且芯片的楼层搭建越多工艺上的难度越大。因此,现有技术并未针对处理不同频段的声波和芯片工艺的难易程度之间给出一个综合的解决方案。

技术实现要素:

5.本发明实施例的目的在于提供一种基于saw和baw并列叠放的滤波器芯片,旨在同时使滤波器芯片处理多频段声波并且使得工艺难度降低。

6.本发明实施例是这样实现的,一种基于saw和baw并列叠放的滤波器芯片,所述基于saw和baw并列叠放的滤波器芯片包括衬底、saw谐振层、baw谐振层和高阻片;

7.所述衬底上设置有腔体或槽体,所述衬底通过支撑柱与所述高阻片连接,所述支撑柱与所述高阻片之间设置有所述saw谐振层和所述baw谐振层;

8.所述saw谐振层和所述baw谐振层通过第一导线连接,且所述baw谐振层设置在所述槽体或所述腔体上;

9.所述衬底上或所述高阻片上设置有引脚,所述引脚通过第二导线分别与所述saw谐振层和所述baw谐振层连接。

10.本发明实施例的另一目的在于一种基于saw和baw并列叠放的滤波器芯片制造工艺,所述基于saw和baw并列叠放的滤波器芯片制造工艺包括:

11.在衬底和baw谐振层之间设置牺牲层;

12.在所述衬底上设置saw谐振层,并通过第一导线连接所述baw谐振层和所述saw谐振层;

13.在所述衬底上设置支撑柱,在所述支撑柱上设置高阻片;

14.利用减薄工艺削减所述衬底和所述高阻片的厚度,并使得所述衬底上的所述牺牲层成为腔体或槽体;

15.在所述衬底上或所述高阻片上设置引脚,通过第二导线将所述引脚分别与所述

saw谐振层、所述baw谐振层连接。

16.本发明实施例提供的一种基于saw和baw并列叠放的滤波器芯片,设置了一种包含saw谐振层和baw谐振层的混合结构滤波器芯片,并将saw谐振层和baw谐振层并列设置在衬底上,减小芯片搭楼层的高度,使得混合滤波器芯片不仅能处理不同频段的声波,还能降低工艺设计的难度。

附图说明

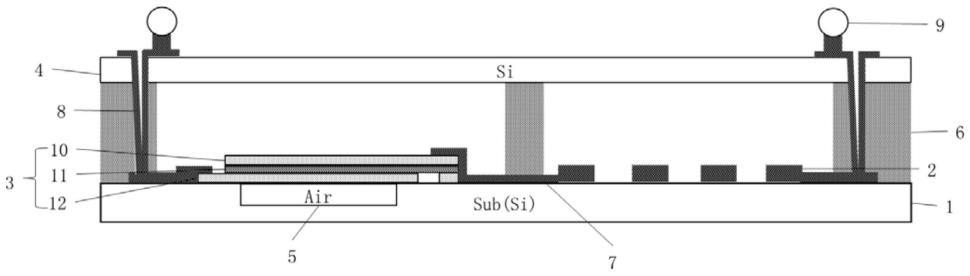

17.图1为一个实施例中提供的一种基于saw和baw并列叠放的滤波器芯片;

18.图2为一个实施例中提供的另一种基于saw和baw并列叠放的滤波器芯片;

19.图3为一个实施例中提供的基于saw和baw并列叠放的滤波器芯片制造工艺的流程图;

20.图4为一个实施例中提供的设置baw谐振层的结构图;

21.图5为一个实施例中提供的设置saw谐振层的结构图;

22.图6为一个实施例中提供的设置支撑柱的结构图;

23.图7为一个实施例中提供的设置高阻片的结构图;

24.图8为一个实施例中提供的一种削减高阻片和衬底的结构图;

25.图9为一个实施例中提供的另一种削减高阻片和衬底的结构图;

26.附图标记:

27.1、衬底;2、saw谐振层;3、baw谐振层;4、高阻片;5、腔体;6、支撑柱;7、第一导线;8、第二导线;9、引脚;10、第一电极层;11、介质层;12、第二电极层;13、电极层子块;14、槽体。

具体实施方式

28.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

29.可以理解,本技术所使用的术语“第一”、“第二”等可在本文中用于描述各种元件,但除非特别说明,这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。举例来说,在不脱离本技术的范围的情况下,可以将第一xx脚本称为第二xx脚本,且类似地,可将第二xx脚本称为第一xx脚本。

30.如图1或图2所示,在一个实施例中提供了一种基于saw和baw并列叠放的滤波器芯片,所述基于saw和baw并列叠放的滤波器芯片包括衬底1、saw谐振层2、baw谐振层3和高阻片4;

31.所述衬底1上设置有腔体5或槽体14,所述衬底1通过支撑柱6与所述高阻片4连接,所述支撑柱6与所述高阻片4之间设置有所述saw谐振层2和所述baw谐振层3;

32.所述saw谐振层2和所述baw谐振层3通过第一导线7连接,且所述baw谐振层2设置在所述腔体5或所述槽体14上;

33.所述衬底1上或所述高阻片4上设置有引脚9,所述引脚9通过第二导线8分别与所述saw谐振层2和所述baw谐振层3连接。

34.具体的,衬底1一般为硅基板或者玻璃板,作为滤波器芯片的基底。saw谐振层2为

表面声谐振器(saw,surface acoustic wave)中的功能部分,设置在衬底1的上方,为音叉状,用于声表面波处理。baw谐振层3为薄膜体声谐振器(bulk acoustic wave)中的功能部分,为多层金属和介质构成的多层结构,以纵波或横波在固体内部传递的形式来处理声波信号。高阻片4由硅制成。

35.saw谐振层2和baw谐振层3均设置在衬底1的表面上,并且在saw谐振层2的下方,也就是衬底上设置有腔体5或槽体14。对于腔体5或槽体14,以及引脚9的设置,本实施例提供了4种可选的方案:

36.第一种,衬底上设置有封闭的腔体,衬底上设置有引脚;

37.第二种,如图1所示,衬底1上设置有封闭的腔体5,高阻片4上设置有引脚9;衬底1上的腔体5为封闭状态的内腔,整体的结构耐压性强,更加稳定;

38.第三种,衬底上设置有开放的槽体,高阻片上设置有引脚;

39.第四种,如图2所示,衬底1上设置有开放的槽体14,衬底1上设置有引脚9;衬底1上的槽体14开口向下,处于开放的状态。一般来说,在衬底1的底部设置槽体14的具有两面性:优势在于纵向尺寸会相对减少,变得更薄,但外界环境会对baw的工作区存在寿命缩短的风险,比如水汽的影响。而第四种结构的优点在于通过减少si衬底1的厚度,减小器件尺寸的同时,也可以不缩短器件使用寿命,因为引脚9与衬底1的底部位于同一侧。在后段封装的过程中,pcb基板与衬底的下方熔接,基板的表面可以用作器件的保护层,隔绝水汽,从而保证芯片寿命。

40.本实施例提供了四种结构不同的芯片,在实际生产中可以根据不同的需要来选择不同的芯片,提高芯片生产以及封装集成的选择自由度。

41.在本实施例中,所述baw谐振层3包括第一电极层10、介质层11和第二电极层12;

42.所述第一电极层10设置在所述腔体5或所述槽体14上,所述介质层11设置在所述第一电极层10上,所述第二电极层12设置在所述介质层11上;

43.所述第一电极层10上设置有电极层子块13;

44.所述第一电极层10通过所述第二导线8与所述引脚9连接,所述第一导线7将所述第二电极层12、所述介质层11、所述电极层子块13和所述saw谐振层2串联起来。

45.具体的,baw的工作区主要是依靠“三明治”状的baw谐振层(金属-介质-金属),也就是由第一电极层10、介质层11和第二电极层12组成的三膜层结构。“三明治”状的膜层结构仅仅是一种实施例,具体可设置的膜层不限于三层,可以是多层。第一电极层10和第二电极层12所用的材料为mo(钼),介质层11为氮化铝(aln)或掺钪氮化铝(scaln),所形成的“三明治”膜层为mo-aln-mo或mo-scaln-mo。此外,通过刻蚀工艺在第一电极层10上分离出的电极层子块13,可防止器件在运行的过程中导致短路,提高滤波器芯片运行的稳定性。

46.在本实施例中,所述saw谐振层2和所述baw谐振层3设置在由所述衬底1、所述高阻片4和所述支撑柱6构成的封闭空间中,其中所述saw谐振层2和所述baw谐振层3被所述支撑柱6分隔开。

47.众所周知,芯片的楼层搭建越多工艺上的难度越大。本实施例提供的四种结构都可视为单楼层结构,在工艺技术难度小且芯片尺寸纵向高度明显减小。此外,本实施例的芯片包括saw和baw,构成一种hybrid filter(混合结构滤波器)叠层模块结构,不仅能适应不同频段的声波滤除需求,还拥有较高的q值设计,在满足终端产品的性能需求的同时,也可

以与终端产品的高集成小尺寸的要求有更高适配度。

48.如图3所示,在一个实施例中,提供了一种基于saw和baw并列叠放的滤波器芯片制造工艺,包括步骤s202~s210:

49.步骤s202,在衬底1和baw谐振层3之间设置牺牲层。

50.在本实施例中,步骤s202具体包括步骤s302~s314:

51.步骤s302,利用光刻刻蚀工艺在所述衬底1上设置凹槽;

52.步骤s304,在所述凹槽中填充牺牲层材料;

53.步骤s306,利用cmp抛光工艺对所述衬底1表面进行抛光处理;

54.步骤s308,在所述凹槽上设置第一电极层10,利用光刻刻蚀工艺从所述第一电极层10中分离出电极层子块13;

55.步骤s310,在所述第一电极层10上设置介质层11;

56.步骤s312,在所述介质层11上设置第二电极层12;

57.步骤s314,利用湿法腐蚀工艺去除所述凹槽中的牺牲层材料,得到所述牺牲层。

58.由步骤s302~s314得到的中间产品的结构如图4所示,第一电极层10设置在衬底1上。在衬底1上,位于第一电极层10的下方设置有一个牺牲层,牺牲层用于后续的腔体5或槽体14的加工。在设置第一电极层10和第二电极层12时,都是设置一层金属膜mo,在设置介质层11时设置一层scaln/aln介质膜层,在经过光刻刻蚀工艺除去多余的区域,保留工作区域。

59.步骤s204,在所述衬底1上设置saw谐振层2,并通过第一导线7连接所述baw谐振层3和所述saw谐振层2。

60.在本实施例中,步骤s204具体包括步骤s402~s404:

61.步骤s402,利用pvd工艺在所述衬底1上形成种籽层;

62.步骤s404,通过电镀工艺在所述种籽层上形成第一导线7以及所述saw谐振层2,并使得所述saw谐振层2与所述baw谐振层3连接。

63.由步骤s402~s404得到的中间产品的结构如图5所示,saw谐振层2与baw谐振层3之间间隔,并列设置在衬底1上,后续可将两者分隔开。

64.步骤s206,在所述衬底1上设置支撑柱6,在所述支撑柱6上设置高阻片4。

65.在本实施例中,步骤s206具体包括步骤s502~s508:

66.步骤s502,在所述衬底1上设置绝缘层;

67.步骤s504,利用干法工艺和湿法工艺去除所述绝缘层中间部分的材料,使所述saw谐振层2与所述baw谐振层3裸露出来,并得到所述支撑柱6;

68.步骤s506,利用cmp抛光工艺对所述支撑柱6进行抛光处理;

69.步骤s508,利用键合工艺在所述支撑柱6上设置所述高阻片4,使所述衬底1和所述高阻片4之间形成封闭空间。

70.由步骤s502~s508得到的中间产品的结构如图6及图7所示,支撑柱6将saw谐振层2与baw谐振层3隔开,高阻片4在顶部封住芯片,使得saw谐振层2与baw谐振层3各自设置在密闭空间中。

71.步骤s208,利用减薄工艺削减所述衬底1和所述高阻片4的厚度,并使得所述衬底1上的所述牺牲层成为腔体5或槽体14。

72.由步骤s208得到的中间产品的结构如图8或图9所示,图8和图9的区别在于衬底1减薄的厚度,形成槽体14削减的厚度大,形成腔体5削减的厚度小。

73.步骤s210,在所述衬底1上或所述高阻片4上设置引脚9,通过第二导线8将所述引脚9分别与所述saw谐振层2、所述baw谐振层3连接。

74.在本实施例中,步骤s210具体包括步骤s602~s608:

75.步骤s602,利用tsv工艺在所述衬底1上或所述高阻片4上开设通孔;

76.步骤s604,利用pvd工艺在通孔上设置种籽层;

77.步骤s606,利用电镀铜工艺在通孔形成所述第二导线8;

78.步骤s608,利用高温回流工艺在所述衬底1上或所述高阻片4上设置所述引脚9,使得所述引脚9通过第二导线8分别连接所述saw谐振层2和所述baw谐振层3。

79.由步骤s602~s608得到的结构如图1或图2所示,经过步骤s208和步骤210的工艺处理,本实施能得到四种混合滤波器芯片。四种基于saw和baw并列叠放的滤波器芯片已经在上述做了详细描述,此处不再赘述。

80.此外,引脚9包括铜柱和锡银球体。利用电镀工艺在高阻片4上或衬底上设置所述铜柱,使所述铜柱连接所述第二导线8,再在铜柱上设置锡银层,利用高温回流工艺将锡银层回流成球体,得到所述锡银球体;设置该引脚有利于后续的pcb板熔接。

81.本实施例提供的单楼层的基于saw和baw并列叠放的滤波器芯片结构,构成混合结构滤波器叠层模块结构,在工艺技术难度小且芯片尺寸纵向高度明显减小,不仅能适应不同频段的声波滤除需求,还拥有较高的q值设计。

82.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

83.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

84.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1