一种滤波器模组的埋入结构及制造方法与流程

1.本发明涉及半导体射频技术领域,具体涉及一种信号接收端滤波器模组 集成器件。

背景技术:

2.当前封装结构:

3.第一种:pip(package in package)模组器件内封滤波器塑封器件

4.常见外形有lga(land grid array)栅格阵列封装,内部平面结构是在基板 (元器件载体)之上贴装所有元件,排布元件包括:多个滤波器封装体,一个倒 装开关芯片,多个电感被动元件等。滤波器封装体与模组基板用锡焊料连接, 元器件缝隙用环氧树脂填充,起到电路隔离和保护作用。

5.滤波器封装体常用结构是基板上倒装一颗滤波器芯片,芯片上方贴覆一 层隔离膜,使滤波器芯片表面idt谐振器处于空腔环境,保障idt谐振器功 能正常运作。隔离膜上方填充环氧树脂,填充缝隙并使表面平整。

6.优点:开关芯片与基板之间使用环氧树脂填充后没有空腔应力释放和电 路保护效果好,电感被动元件两极之间使用环氧树脂填充后没有空腔导致电 路短路问题。

7.缺点:滤波器封装体面积大,器件密集度高,器件间距(空隙)小,塑封过 程极易造成环氧树脂填充不充分,形成模组器件内部空洞,容易造成不同线 路元件之间短路,密闭性不佳造成开裂,空洞吸水汽化使器件内部爆裂等问 题。作为平衡将会极限缩小滤波器封装体体积,会使滤波器封装体内滤波器 芯片到封装体边缘距离变小,从而降低了滤波器覆膜阻挡水汽浸入能力,会 进一步衍生可靠性次生问题。

8.第二种:平面集成贴装,常见外形有lga(land gridarray)栅格阵列封装。

9.内部平面结构主要是平面排布于基板(元器件载体)之上,也有少部分芯片 与芯片堆叠形式。排布元件包括:多个滤波器芯片,一个倒装开关芯片,多 个电感被动元件等。

10.内部纵面结构是在基板上表面贴装所有元件。所有元件上贴覆一层隔离 膜,使滤波器芯片表面idt谐振器处于空腔环境,保障idt谐振器功能正常 运作。隔离膜上方填充环氧树脂,填充缝隙并使表面平整。

11.优点:相较pip结构,滤波器芯片比滤波器封装体的面积和体积都小, 可以适当腾挪表面贴装空间。

12.缺点:器件密集度高,器件间距(空隙)小,塑封过程极易造成环氧树脂填 充不充分,形成模组器件内部空洞,密闭性不佳会造成开裂,空洞吸水汽化 使器件内部爆裂等问题。并且整体覆膜会使被动原件两极间形成空腔,会有 锡料短路高风险。也会使倒装开关芯片与基板之间形成空腔,会有锡料短路 风险。同时,倒装开关芯片与基板之间没有环氧树脂有效填充,模组器件在 不同环境下应力不均衡极易致使铜柱与基板,铜柱与锡料,铜柱与芯片等连 接处断裂,造成电路失效。

13.如附图6、图7所示,都包含电感被动元件10,并且开关芯片8都置于 基板外部。

技术实现要素:

14.为解决现有技术中存在的问题,本方案将滤波器模组内全器件封装改为 部分封装加部分基板内埋,解决了滤波器空腔覆膜与倒装开关芯片铜柱空隙 充分填充的冲突问题,解决了电感被动元件两极间空隙填充问题,解决了滤 波器封装体极致缩小体积造成可靠性隐患问题,解决了全器件封装多种不同 材质内应力不均衡导致产品变形和失效隐患,解决了元器件密集缝隙小环氧 树脂填充不充分问题。同时,可以选择滤波器不同封装方案,可以有效降低 使用高成本特殊覆膜材料方案的成本控制。

15.所采用的必要技术手段为提供一种滤波器模组的埋入结构,具有基板, 开关芯片内埋于基板内部并位于基板内部线路之间;基板的底面为间隔设置 的底层线路,底层线路之间的间隔通过基板油墨封住,滤波器芯片通过锡球 直接或间接与基板正面电连接。

16.优选地,具有滤波器封装体,所述滤波器封装体由含金柱的滤波器芯片、 钝化粘结层、滤波器基板、谐振器以及塑封材料组成,滤波器芯片置于滤波 器基板上面,金柱与滤波器芯片下端连接,金柱与滤波器基板表面镀金层相 结合,锡球凸出于滤波器基板下底面,

17.滤波器封装体内的滤波器芯片通过锡球间接与模组基板电连接,滤波器 封装体与基板之间用模组塑封层封装。

18.更优选地,所述滤波器芯片的下底面与滤波器基板上表面之间具有空腔, 谐振器设于滤波器芯片的下底面并在空腔内,除底面外,滤波器芯片的四周 用钝化粘结层覆膜,钝化粘结层外侧用塑封材料封装,滤波器基板与塑封材 料之间用钝化粘结层隔开。

19.进一步,锡球设于滤波器封装体底部,滤波器芯片通过底部锡球直接与 模组基板正面电连接。

20.另一种优选地方案,滤波器芯片通过钝化粘结层覆膜后用模组塑封层封 装在基板上,滤波器芯片的下底面与基板顶面之间具有空腔,谐振器设于滤 波器芯片的下底面并在空腔内。

21.进一步,具有锡球为4-6个数量不等锡球,根据滤波器模组功能逻辑,部 分锡球通过基板线路层焊盘与开关芯片的上端连接,另一部分锡球与模组基 板其它功能线路相连接。

22.优选地,还包括置于基板内部的电感被动元件。

23.优选地,滤波器芯片厚度200-250um,钝化粘结层厚度20-50um,滤波器 基板为两层或多层线路叠加,厚度110-200um,滤波器芯片与滤波器基板1-5 互联层为10-15um金柱,滤波器封装体的总厚度为450-550um。

24.本发明还提供了一种滤波器模组的埋入结构的制造方法,其特征在于, 包括步骤:

25.1)基板设计:

26.基板为四层板结构,基板总厚度300-400um,其中基板油墨厚度25-30um, 非芯片层铜柱厚度30-40um,芯片层铜柱高度125-150um,线路层厚度 20-25um,基板线路宽度15um以上,线路间距15um以上,基板线路和铜柱为 铜材质,线路间有机填充为半固化树脂,芯片和电感元件周围压合abf有机 材料填充固化,基板线路使用化镀工艺,基板表面处理正面焊盘沉积0.1-0.3um 防氧化膜osp,基板背面焊盘化镀镍钯金,镍层厚度3-8um,钯层厚度

0.1um 以上,金层厚度0.7um以上;

27.2)基板制作:

28.发料

29.使用双层线路叠加法工艺的掺有玻璃纤维的环氧树脂核心材料或者用单 层线路递增法工艺的不带掺有玻璃纤维的环氧树脂核心材料的面板;

30.芯片和元件埋入前基板内层结构制作

31.3um基铜去污活化,黄光室压干膜,曝光非铜柱区域干膜,蚀刻未曝光 区域,电镀200um高度铜柱,去曝光干膜,压半固化材料,烘烤固化,减薄 半固化材料露出铜柱,此时铜柱高度约175um,二次贴干膜,曝光非埋入芯 片和元件区域铜柱和有机成飞区域,蚀刻埋入芯片和元件区域干膜,去除曝 光干膜,埋入芯片和元件区域铜柱完全去除并预留贴装空腔,

32.芯片和元件埋入

33.在板级材料表面压合一层5um后双面胶膜,胶膜外表面粘结在载板台钢 板上,胶膜内表面完全粘结在基板表面,贴装空腔处胶膜保持粘性状态悬浮 空腔上方,拆除发料时基板载板,露出贴装空腔和铜柱底层截面和已固化有 机填充区域,完成转板过程,用pick&place形式将编带中100um厚度芯片线 路和焊盘面贴于粘性胶膜上,同时将100um高度超薄元件导电位置贴于粘性 胶膜上,完成芯片和元件埋入,以真空方式用200um厚度非导电abf有机材 料压合在贴有芯片和元件的空腔内,确保填充完整;空腔内和基板表面都将 处于abf压合并完全覆盖状态,烘烤固化abf,减薄abf控制露出铜柱并确 保芯片和元件不露出,此时铜柱高度125-150um;

34.减薄abf面镀铜

35.减薄abf面铜柱,空腔abf,已固化铜柱间有机填充处于水平状态,进 行化学沉积3um厚度种子铜层,再进行电镀铜层厚度达到30um;

36.芯片线路面和元件导电位置扇出重布线

37.拆分芯片线路面基板与载板,撕除芯片线路面双面胶膜,露出芯片表面 及导电焊盘,元件导电位置,基板铜柱,以及abf和已固化填充的有机材料, 此时芯片表面除70um焊盘开窗其它区域均有1-2um绝缘保护层覆盖,化学沉 积3um厚度铜种子层,压干膜并曝光非线路区域,蚀刻非线路区域干膜露出 线路区,电镀20um厚度线路层,去曝光区域干膜和底部非线路区域种子层3um 铜材料,压合半固化有机材料并烘烤固化,

38.芯片背面外露基板铜线线路成型

39.翻板对芯片背面基板外露30um厚度铜层除污活化,厚度减薄至20um,压 干膜,曝光,蚀刻非线路区域干膜,蚀刻非线路区域20um厚铜,去曝光干膜, 露出线路,压合半固化有机材料并烘烤固化,芯片和元件完成内埋,芯片正 背面基板已完成线路成型;

40.基板外层线路成型

41.基板正背面固化后有机材料,通过对位确认以镭射钻盲孔形式对有机材 料开孔处理,镭射钻孔后露出基板内层线路焊盘,除污活化焊盘,化学沉积 3um种子层铜材质,基板正背面及镭射孔壁孔盘处于铜材质全覆盖状态;压 干膜曝光非线路区域,蚀刻非曝光区域干膜,蚀刻非线路区域种子铜材质, 去除曝光区域干膜,电镀铜材质使3um厚度种子铜厚度增至20um,完成正背 面填孔和线路;正面线路设计时,滤波器与滤波器之间距需要满足

100um以 上,确保后工序覆隔离膜有效贴覆,以及塑封时有效性填充;

42.基板覆油墨

43.基板覆盖油墨黄光室基板正背面涂覆油墨,预烘烤油墨半固化,曝光非 焊盘开窗区域,蚀刻开窗区域露出基板正背面焊盘;

44.基板面板拆分单条基板和表面处理

45.将基板面板冲压拆分为封装可制造单条尺寸,除污活化,选择基板正背 面焊盘表面处理方式,用lga方案,基板背面焊盘化镀镍钯金材料,镍厚度 3-8um,钯厚度0.1um,金厚度0.07um以上,基板正面沉积osp防氧化有机材 料,完成基板焊盘表面处理。

46.3)基板测试包装出货;

47.基板上每个单元进行电路测试分选良品次品,系统标记次品位置,基板 外观再次确认良品次品,系统再次记录次品位置,实物次品镭射标记,系统 生成e-mapping,统计良品数量后包装出货到封装工厂

48.4)模组产品封装

49.5)测试包装出货

50.切单颗成型并检验外观,外观检验区分良次品,进行外观检验,挑出次 品后将良品进行电性能测试;测试分选良品和不同电性能次品,良品进行包 装,贴好标签出货到应用端;对不良品进行分析验证,为后续新产品做改进 准备。

51.优选地一种方案,所述步骤4)模组产品封装过程为使用单体滤波器封装 体二次封装:

52.根据设计结构对应频段需求贴装滤波器封装体,滤波器可以是单频段制 式,也可以是双频段制式,双频段制式为b1+b3、b8+b26、b2+b66、b20+b28、 b34+b39、b39+b41中的任意一种,

53.滤波器封装体结构为滤波器芯片线路焊盘面通过超声焊方式实现金柱与 芯片,金柱与滤波器基板相结合,金柱高度为10-15um,芯片倒扣在基板上, 芯片和基板外路面覆一层20-50um厚半固化膜形成滤波器线路面与基板间空 腔,实现谐振器空腔结构正常工作,半固化隔离膜外进行塑封再固化,起到 内部元件有效保护和表面平整标准结构,

54.滤波器封装体基板上外露焊盘和模组对位焊盘设计为圆形结构,

55.滤波器模组封装过程:

56.滤波器封装体贴片

57.模组基板上钢网印刷锡膏在滤波器焊盘对位点,钢网厚度80um;根据设 计图纸对应不同位置贴装不同滤波器封装体,此过程一次贴装完成,贴装后 进行回流焊,将印刷锡膏液化再固化实现滤波器封装体端子与模组基板焊盘 电路连接,此时滤波器封装体由多个端子上圆柱形锡柱支撑在模组基板上, 锡柱间形成廊道间隙,滤波器封装体与模组基板垂直间距在40-60um,

58.滤波器模组塑封

59.回流烘烤去水汽后进行环氧树脂塑封,塑封材料选用最大20um直径的二 氧化硅或氮化铝陶瓷圆球作为填料,被塑封元器件最小间隙大于两倍填料直 径时塑封填充可实现完整有效填充,塑封后进行175℃8-12小时恒温烘烤固 化,确保交联反应完全,

60.塑封后工序加工

61.烘烤后进行镭射打标,将基板每颗元件塑封体上做标记,将基板切割分 离成单颗模组元件成品进行检验。

62.另一种优选方案,所述步骤4)模组产品封装过程为使用带锡球滤波器芯 片封装:

63.根据设计结构对应频段需求贴装滤波器芯片,滤波器可以是单频段制式, 也可以是双频段制式,双频段制式为b1+b3、b8+b26、b2+b66、b20+b28、 b34+b39、b39+b41中的任意一种,

64.准备植锡球滤波器芯片,使用4寸或6寸滤波器晶圆进行先进封装植锡球 加工,4寸滤波器晶圆厚度250um,6寸滤波器晶圆厚度350um,滤波器晶圆上 芯片焊盘开口80um,植球后锡球直径80um,锡球高度50um;

65.滤波器晶圆中测,对完成植锡球晶圆上每颗芯片测试,系统中产生良品 和次品电子分布图,

66.滤波器模组封装过程:

67.滤波器晶圆研磨划片

68.4寸晶圆不需要研磨减薄,6寸晶圆需要减薄厚度到200-250um以内,方便 后工序隔离膜覆盖和模组整体厚度控制,划片后单颗滤波器芯片呈分离状态。

69.滤波器芯片良品编带

70.根据良次品电子分布图将分离状态滤波器良品芯片放到编带载带并盖 好,此过程每一种滤波器芯片放在一个编带内,不同滤波器芯片区分在不同 编带内,并做好标签处理,

71.贴装滤波器芯片

72.贴装前需要根据滤波器对应模组基板焊盘设计印刷锡膏钢网,完成锡膏 印刷后贴装所有已选型滤波器,此过程将模组中所需多型号滤波器一次性贴 装在埋入元件基板对应位置,完成贴装后进行锡球回流焊接,此时滤波器芯 片与模组基板完成电性能信号线路连接,滤波器芯片线路表面与模组基板表 面间距在20-30um,

73.覆隔离膜

74.真空贴覆隔离膜,贴膜后在130℃恒温下的真空烤箱内烘烤2-4小时,确 保隔离膜与滤波器芯片及模组基板有效结合,此过程完成后,每个滤波器芯 片线路面与模组基板之间形成空腔结构,

75.模组基板塑封

76.模组基板塑封在模压成型塑封设备上完成,单模腔塑封设备合模压力控 制在2.3-2.8ton,双模腔塑封设备合模压力控制在5-6ton,塑封后在175℃恒 温烤箱内烘烤再固化。

77.滤波器模组后工序加工

78.对模组基板每颗器件塑封料上镭射印制标签字符,切割模组基板分离每 颗模组器件检验测试。

79.优选地,还包括在步骤2)中在基板内埋入电感被动元件。

80.优选地,还包括在步骤2)中基板设计阶段以基板线路绕环方式实现代替 电感被动元。根据不同滤波器规格在输入和输出端对应匹配电感值设计基板 绕线,基板绕线实现电感功能说明如下。

81.导线电感换算公式:

[0082][0083]

参照图8所示,l为电感值,l为基板走线长度,w为基板走线宽度,h为基 板走线厚度。注意基板走线电感与敷铜厚度无关。

[0084]

从以上公式看出,若基板走线长度减少一半,择电感值也减少一半。但 走线宽度增加10倍才能减少一半的电感值。

[0085]

本发明具有的有益效果:

[0086]

去除开关芯片空腔结构提升可靠性,去除开关芯片上铜柱加工节省成本。 滤波器模组器件内不需要空腔作用的内置开关倒装芯片节省掉铜柱再加工工 序,裸芯片埋入基板内,摒弃倒装开关结构中铜柱间锡桥接和铜柱结构断裂 高风险问题。内埋芯片表面与外界隔离防止空气中杂质对芯片电路腐蚀造成 电气性能下降,保护芯片表面以及连接引线等,使芯片在电气或热物理等方 面免受外力损害及外部环境的影响。

[0087]

通过基板内环氧树脂完整填充,使芯片的热膨胀系数与基板的热膨胀系 数相匹配,有效缓解热等外部环境的变化而产生的应力以及由于芯片发热而 产生的内部应力,可防止芯片损坏或铜柱和锡球断裂失效。同时,也便于安 装和运输。

[0088]

完整有效填充,可为芯片1和其他部件提供牢固可靠的机械支撑,并能适 应各种工作环境和条件的变化,器件长期工作时将聚集的热量散出,保证系 统在使用温度要求的范围内正常工作,对于封装用户、电路板厂家、半导体 厂家都很方便,而且便于标准化

[0089]

本方案将滤波器模组内全器件封装改为部分封装加部分基板内埋,解决 了滤波器空腔覆膜与倒装开关芯片铜柱空隙充分填充的冲突问题,解决了电 感被动元件两极间空隙填充问题,解决了滤波器封装体极致缩小体积造成可 靠性隐患问题,解决了全器件封装多种不同材质内应力不均衡导致产品变形 和失效隐患,解决了元器件密集缝隙小环氧树脂填充不充分问题。同时,可 以选择滤波器不同封装方案,可以有效降低使用高成本特殊覆膜材料方案的 成本控制。

[0090]

从结构上,本方案从模组设计和结构搭建做了有效强化。

[0091]

一是,电感器件优化。方法一将电感被动元件置于基板内部使用abf有 机材料包覆并加以保护。方法二通过设计前期电仿真和实验室匹配调试,将 电感被动元件功能以基板绕线方式实现,去除电感被动元件。滤波器封装体 pip封装和滤波器芯片封装可任意选择性结构保护。

[0092]

二是,倒装开关芯片改为基板内埋。将开关芯片置于基板内部使用abf 有机材料包覆并加以保护。射频模组基板埋入开关芯片结构保护,滤波器贴 片空间不受限制,可定制化缩小模组在终端pcb面积。

[0093]

三是,单体滤波器单面封装。方法一将滤波器封装体通过焊锡贴装于基 板正面,将滤波器封装体与基板间缝隙用环氧树脂有效填充保护。方法二将 植锡球滤波器芯片贴装于基板正面,贴覆隔离膜再进行环氧树脂有效填充。 此强化方式既能起到有效物理保护,又能降低材料使用成本。

附图说明

[0094]

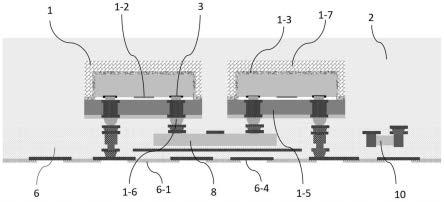

图1是本发实施例1滤波器模组的结构示意图;

[0095]

图2是滤波器封装体的结构示意图;

[0096]

图3是本发实施例2滤波器模组的结构示意图;

[0097]

图4是本发明滤波器芯片的结构示意图;

[0098]

图5是开关芯片的结构示意图;

[0099]

图6、图7为现有产品的结构示意图;

[0100]

图8为电感值、为基板走线长度、为基板走线宽度的原理示意图。

具体实施方式

[0101]

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下 列描述和申请专利范围,本发明的优点和特征将更清楚。需说明的是,附图 均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说 明本发明实施例的目的。

[0102]

请参阅图1,本发明实施例1的一种滤波器模组,具有基板6,基板6正面 为pip结构,多颗封装后滤波器封装体1贴于基板6正面并用模组塑封层2封装, 将开关芯片8和电感被动元件10置于基板内部。滤波器封装体1为单独的,互 不直接连接。基板6为四层板结构,如附图1和附图2,基板总厚度300-400um, 其中基板油墨6-1厚度25-30um,非芯片层铜柱厚度30-40um,芯片层铜柱4-2 高度125-150um,线路层厚度20-25um,基板线路宽度15um以上,线路间距 15um以上。

[0103]

滤波器封装体1的结构如附图2和图4所示,由含金柱1-4的滤波器芯片1-1、 钝化粘结层1-3、滤波器基板1-5、谐振器1-2以及塑封材料1-7组成。滤波器芯 片1-1置于滤波器基板1-5上面,金柱1-4与滤波器芯片1-1下端连接,金柱1-4 插入滤波器基板1-5内,金柱1-4下端有锡球1-6,锡球1-6凸出于滤波器基板1-5 下底面。滤波器芯片1-1的下底面与滤波器基板1-5上侧面之间具有空腔1-8, 谐振器1-2设于滤波器芯片1-1的下底面并在空腔1-8内。除底面外,滤波器芯 片1-1的四周用钝化粘结层1-3覆膜,钝化粘结层1-3外侧用塑封材料1-7封装。 滤波器基板1-5与塑封材料1-7之间用钝化粘结层1-3隔开。滤波器芯片厚度 200-250um,钝化粘结层1-3厚度20-50um,滤波器基板1-5为两层或多层线路 叠加,厚度110-200um,滤波器芯片1-1与滤波器基板1-5互联层主要为10-15um 金柱1-4,滤波器封装体1的总厚度为450-550um。

[0104]

滤波器芯片1-1到塑封材料1-7最外侧边缘需大于50um,75um或以上更 佳,间距越大防止吸水的可靠性越强,本实施例为80um。

[0105]

继续参考图1,基板6的底面为间隔设置的底层线路6-4,底层线路6-4之间 的间隔通过基板油墨6-1封住,所以底层线路6-4和基板油墨6-1在基板6的底部 是间隔设置的。

[0106]

参考图3,为本发明2实施例的滤波器模组,基板6与实施例1的相同,滤 波器芯片1-1通过钝化粘结层1-3覆膜后用模组塑封层2封装在基板上。滤波器 芯片1-1的下底面与滤波器基板6顶面之间具有空腔1-8,谐振器1-2设于滤波器 芯片1-1的下底面并在空腔1-8内。除底面外,滤波器芯片1-1的四周用钝化粘 结层1-3覆膜,钝化粘结层1-3外侧用模组塑封层2封装。基板6内设有多层线路, 包括三层线路6-5、底层线路6-4和二层线路6-7,开关芯片8置于多层线路之间。

[0107]

本发明滤波器模组制造方法:

[0108]

1、材料准备:

[0109]

开关芯片8:

[0110]

本方法以合理成本控制和面积有效性上使用不带铜柱的开关芯片,开关 芯片功能开口焊盘开窗70um,焊盘间距130um,通过基板铜柱与芯片功能开 口焊盘相结合。晶圆先进行电性能测试筛选出达标芯片,厚度从750um减薄 到100um,切成单颗晶粒开关芯片,将电测性能达标的开关芯片包装好为埋 入基板做好准备。如图5所示,开关芯片焊盘上端连接有铜柱8-1,铜柱8-1上 端设有锡帽8-2。

[0111]

基板6:

[0112]

基板6为四层板结构,如附图1-附图3,基板总厚度300-400um,其中基板 油墨厚度25-30um,非芯片层铜柱厚度30-40um,芯片层铜柱高度125-150um, 线路层厚度20-25um,基板线路宽度15um以上,线路间距15um以上。

[0113]

基板材质:基板线路和铜柱为铜材质,线路间有机填充为半固化树脂, 芯片和电感元件周围压合abf有机材料填充固话,能有效防止内应力导致形 变断路等问题。

[0114]

3、基板制作工艺:基板线路使用化镀工艺,不需要外拉电镀线,有效利 用产品面积。基板表面处理正面焊盘沉积0.1-0.3um防氧化膜osp,基板背面 焊盘化镀镍钯金,镍层厚度3-8um,钯层厚度0.1um以上,金层厚度0.7um以上。

[0115]

面板排布:设计基板面板排布和基板实物信息刻印内容,确保加工过程 不会混料并具备生产管理和追溯性。

[0116]

3.1发料:

[0117]

使用双层线路叠加法工艺的掺有玻璃纤维的环氧树脂核心材料,亦可使 用单层线路递增法工艺的不带掺有玻璃纤维的环氧树脂核心材料的面板。本 发明实施例选用单层线路递增法工艺材料做工艺制作说明。

[0118]

3.2芯片和元件埋入前基板内层结构制作:

[0119]

3um基铜去污活化,黄光室压干膜,曝光非铜柱区域干膜,蚀刻未曝光 区域,电镀200um高度铜柱,去曝光干膜,压半固化材料,烘烤固化,减薄 半固化材料露出铜柱,此时铜柱高度约175um。二次贴干膜,曝光非埋入芯 片和元件区域铜柱和有机成飞区域,蚀刻埋入芯片和元件区域干膜,去除曝 光干膜。此时,埋入芯片和元件区域铜柱已完全去除并预留贴装空腔。

[0120]

3.3芯片和元件埋入:

[0121]

在板级材料表面压合一层5um后双面胶膜,胶膜外表面粘结在载板台钢 板上,胶膜内表面完全粘结在基板表面,贴装空腔处胶膜保持粘性状态悬浮 空腔上方。拆除发料时基板载板,露出贴装空腔和铜柱底层截面和已固化有 机填充区域,完成转板过程。用pick&place形式将编带中100um厚度芯片线 路和焊盘面贴于粘性胶膜上,同时将100um高度超薄元件导电位置贴于粘性 胶膜上,完成芯片和元件埋入。以真空方式用200um厚度非导电abf有机材 料压合在贴有芯片和元件的空腔内,确保填充完整。此时,空腔内和基板表 面都将处于abf压合并完全覆盖状态。烘烤固话abf,减薄abf控制露出铜 柱并确保芯片和元件不露出,此时铜柱高度约125-150um。

[0122]

3.4减薄abf面镀铜

[0123]

减薄abf面铜柱,空腔abf,已固化铜柱间有机填充处于水平状态,进 行化学沉积3um厚度种子铜层,再进行电镀铜层厚度达到30um。

[0124]

3.5芯片线路面和元件导电位置扇出重布线。

[0125]

拆分芯片线路面基板与载板,撕除芯片线路面双面胶膜,露出芯片表面 及导电焊盘,元件导电位置,基板铜柱,以及abf和已固化填充的有机材料。 此时芯片表面除70um焊盘开窗其它区域均有1-2um绝缘保护层覆盖。化学沉 积3um厚度铜种子层,压干膜并曝光非线路区域,蚀刻非线路区域干膜露出 线路区,电镀20um厚度线路层,去曝光区域干膜和底部非线路区域种子层3um 铜材料,压合半固化有机材料并烘烤固化。

[0126]

3.6芯片背面外露基板铜线线路成型。

[0127]

翻板对芯片背面基板外露30um厚度铜层除污活化,厚度减薄至20um,压 干膜,曝光,蚀刻非线路区域干膜,蚀刻非线路区域20um厚铜,去曝光干膜, 露出线路。压合半固化有机材料并烘烤固化。此时,芯片和元件已完成内埋, 芯片正背面基板已完成线路成型。

[0128]

3.7基板外层线路成型。

[0129]

模组基板设计相对复杂,需要增加线路层到4层或以上可以支持全信号和 性能布局,特别是将电感元件以基板线路绕线圈方式实现功能和降本目的, 需要增加在外层线路上实现。具体实现方式如下:基板正背面固化后有机材 料,通过对位确认以镭射钻盲孔形式对有机材料开孔处理,镭射钻孔后露出 基板内层线路焊盘,除污活化焊盘,化学沉积3um种子层铜材质,此时基板 正背面及镭射孔壁孔盘处于铜材质全覆盖状态。压干膜曝光非线路区域,蚀 刻非曝光区域干膜,蚀刻非线路区域种子铜材质,去除曝光区域干膜,电镀 铜材质使3um厚度种子铜厚度增至20um,完成正背面填孔和线路。此过程基 板正面外层线路比业界方案空间更加足够,可以根据封装后制程贴装滤波器 封装体或滤波器倒装芯片不同方案对基板设计加工。正面线路设计时,滤波 器与滤波器之间距需要满足100um以上,确保后工序覆隔离膜有效贴覆,以 及塑封时有效性填充。

[0130]

3.8基板覆油墨。

[0131]

基板覆盖油墨黄光室基板正背面涂覆油墨,预烘烤油墨半固化,曝光非 焊盘开窗区域,蚀刻开窗区域露出基板正背面焊盘。

[0132]

3.9基板面板拆分单条基板和表面处理。

[0133]

将基板面板冲压拆分为封装可制造单条尺寸。除污活化,选择基板正背 面焊盘表面处理方式,本发明沿用lga方案,基板背面焊盘化镀镍钯金材料, 镍厚度3-8um,钯厚度0.1um,金厚度0.07um以上,基板正面沉积osp防氧化 有机材料,完成基板焊盘表面处理。

[0134]

4,基板测试包装出货。基板上每个单元进行电路测试分选良品次品,系 统标记次品位置。基板外观再次确认良品次品,系统再次记录次品位置。实 物次品镭射标记,系统生成e-mapping,统计良品数量后包装出货到封装工厂。

[0135]

5,模组产品封装。如3.7所述,滤波器模组封装可以选用已完成封装和 测试的100%良率的滤波器封装单体进行贴片二次封装封装,也可以选用含锡 球的滤波器芯片进行倒装贴片封装。滤波器封装体可以是4g单频段接收端制 式,也可以是4g双频段接收端制式。根据不同终端平台在频段1,2,3,5, 7,8,20,26,28,34,39,40,41,66中选取使用。两套方案的加工制作 方法如下:

[0136]

5.1使用单体滤波器封装体二次封装。

[0137]

根据设计结构对应频段需求贴装滤波器封装体,滤波器可以是单频段制 式,也可以是双频段制式,通常双频段制式主要有b1+b3,b8+b26,b2+b66, b20+b28,b34+b39,b39+b41等组合。双频滤波器集成模式制作成本和材料 使用相对理想,会提高空间释放,作为优选方案。

[0138]

滤波器封装体结构为滤波器芯片线路焊盘面通过超声焊方式实现金柱与 芯片,金柱与滤波器基板相结合,金柱高度为10-15um,芯片倒扣在基板上, 芯片和基板外路面覆一层20-50um厚半固化膜形成滤波器线路面与基板间空 腔,实现谐振器空腔结构正常工作,半固化隔离膜外进行塑封再固化,起到 内部元件有效保护和表面平整标准结构。

[0139]

滤波器封装体基板上外露焊盘和模组对位焊盘设计为圆形结构,在模组 二次封装中塑封过程利于环氧树脂塑封料涡流填充,防止滤波器基板与模组 基板间隙出现塑封料填充不满导致不同端子锡料桥接短路。

[0140]

滤波器模组封装过程。

[0141]

5.1.1滤波器封装体贴片。

[0142]

模组基板上钢网印刷锡膏在滤波器焊盘对位点,钢网厚度80um;根据设 计图纸对应不同位置贴装不同滤波器封装体,此过程一次贴装完成。贴装后 进行回流焊,将印刷锡膏液化再固化实现滤波器封装体端子与模组基板焊盘 电路连接,此时滤波器封装体由多个端子上圆柱形锡柱支撑在模组基板上, 锡柱间形成廊道间隙,滤波器封装体与模组基板垂直间距在40-60um,此间隙 是封装加工过程最小间隙。

[0143]

5.1.2滤波器模组塑封。

[0144]

回流烘烤去水汽后进行环氧树脂塑封,塑封材料选用最大20um直径的二 氧化硅或氮化铝陶瓷圆球作为填料,被塑封元器件最小间隙大于两倍填料直 径时塑封填充可实现完整有效填充,既保障塑封料在塑封过程流动性又能起 到缝隙位置填充支撑作用。封装过程是热固性环氧树脂小分子交联反应过程, 塑封后需要进行175度8-12小时恒温烘烤固化,确保交联反应完全。

[0145]

5.1.3塑封后工序加工。

[0146]

烘烤后进行镭射打标,将基板每颗元件塑封体上做标记。将基板切割分 离成单颗模组元件成品。进行外观检验,挑出次品后将良品进行电性能测试。

[0147]

5.2使用带锡球滤波器芯片封装。

[0148]

根据设计结构对应频段需求贴装滤波器芯片,滤波器可以是单频段制式, 也可以是双频段制式,通常双频段制式主要有b1+b3,b8+b26,b2+b66, b20+b28,b34+b39,b39+b41等组合。双频滤波器集成模式制作成本和材料 使用相对理想,会提高空间释放,作为优选方案。

[0149]

准备植锡球滤波器芯片。使用4寸或6寸滤波器芯片进行先进封装植锡球 加工,4寸滤波器芯片厚度250um,6寸滤波器芯片厚度350um,滤波器芯片上 芯片焊盘开口80um,植球后锡球直径80um,锡球高度50um。

[0150]

滤波器芯片中测。对完成植锡球晶圆上每颗芯片测试,系统中产生良品 和次品电子分布图。

[0151]

滤波器模组封装过程。

[0152]

5.2.1滤波器芯片研磨划片。

[0153]

4寸晶圆不需要研磨减薄,6寸晶圆需要减薄厚度到200-250um以内,方便 后工序隔离膜覆盖和模组整体厚度控制。划片后单颗滤波器芯片呈分离状态。

[0154]

5.2.2滤波器芯片良品编带。

[0155]

根据良次品电子分布图将分离状态滤波器良品芯片放到编带载带并盖 好,此过程每一种滤波器芯片放在一个编带内,不同滤波器芯片区分在不同 编带内,并做好标签处理。

[0156]

5.2.3贴装滤波器芯片。

[0157]

贴装前需要根据滤波器对应模组基板焊盘设计印刷锡膏钢网,完成锡膏 印刷后贴装所有已选型滤波器,此过程将模组中所需多型号滤波器一次性贴 装在埋入元件基板对应位置,完成贴装后进行锡球回流焊接。此时滤波器芯 片与模组基板完成电性能信号线路连接,滤波器芯片线路表面与模组基板表 面间距在20-30um。

[0158]

5.2.4覆隔离膜。

[0159]

真空贴覆隔离膜,贴膜后在130度恒温下的真空烤箱内烘烤2-4小时,确 保隔离膜与滤波器芯片及模组基板有效结合。此过程完成后,每个滤波器芯 片线路面与模组基板之间形成空腔结构,可保障滤波器芯片线路间谐振器正 常工作。

[0160]

5.2.5模组基板塑封。

[0161]

模组基板塑封在模压成型塑封设备上完成,单模腔塑封设备合模压力控 制在2.3-2.8ton,双模腔塑封设备合模压力控制在5-6ton,此设备有效控制合 模压力确保隔离膜不被塑封料高压挤破。塑封后在175度恒温烤箱内烘烤再固 化。

[0162]

5.2.6滤波器模组后工序加工。

[0163]

对模组基板每颗器件塑封料上镭射印制标签字符,切割模组基板分离每 颗模组器件。外观检验区分良次品。进行外观检验,挑出次品后将良品进行 电性能测试。

[0164]

6,测试包装出货。测试分选良品和不同电性能次品,良品进行包装,贴 好标签出货到应用端。对不良品进行分析验证,为后续新产品做改进准备。

[0165]

通过以上较佳具体实施例的详述,希望能更加清楚描述本发明的特征与 精神,而并非以上述所揭示的较佳具体实施例来对本发明的范畴加以限制。 相反地,其目的是希望能涵盖各种改变及具相等性的安排于本发明所欲申请 权利要求的范畴内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1