逐次逼近型模数转换器的制作方法

1.本发明涉及集成电路设计领域,特别是涉及一种逐次逼近型模数转换器。

背景技术:

2.模数转换器是将现实世界中,在时间上和幅度上连续的模拟信号转换为时间上和幅度上离散的数字信号,以便于数据的处理和存储。随着世界信息化的发展,这一功能模块已经成为绝大多数电子系统中必不可少的组成部分。

3.传统的模数转换器大部分都是基于模拟信号和参考信号源,通过比较器比较来得到数字结果。在电路设计中,一种方式是让输入模拟信号通过与某个参考信号的运算(相减、倍乘等)结果与固定的参考电压进行比较,从而得到数字结果,如流水线型模数转换器(pipelined-adc);另一种方式是输入模拟信号不变,根据比较器的输出来切换比较器输入的参考信号,通过获得比较器的输出来获得最终数字结果,如逐次逼近型模数转换器(sar adc)。

4.由于面积较小、成本低、功耗低,sar adc在深亚微米集成电路设计中逐渐成为主流adc。但是,由于sar adc采用开关电容电路,难以解决开关漏电、寄生等难题,所以,集成电路设计中通常采用一些高压mos管,从而加大了工艺复杂度,且提高了成本。同时,在许多adc应用中,保持单调性(monotonicity)是应用中的关键诉求,但是,在开关电容型sar adc中,由于电容匹配的难度,使得保持单调性成为设计难点。

5.因此,设计一种更适用于深亚微米工艺的sar adc,成为本领域技术人员迫切需要解决的技术问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种逐次逼近型模数转换器,用于解决现有sar adc在深亚微米工艺中存在开关漏电、寄生等问题。

7.为实现上述目的及其他相关目的,本发明提供一种逐次逼近型模数转换器,包括:

8.采样保持模块,用于对输入电压进行采样保持并产生采样电压输出;

9.比较模块,连接所述采样保持模块的输出端,用于比较所述采样电压和参考电压并产生比较结果输出;

10.数字处理模块,连接所述比较模块的输出端,用于根据所述比较结果产生数字控制信号输出,其中,所述数字控制信号包括n位高位控制信号和m位低位控制信号;

11.电阻型数模转换模块,连接于所述数字处理模块和所述比较模块之间,用于根据所述n位高位控制信号控制高位电阻网络产生粗调参考,根据所述m位低位控制信号控制低位电阻网络产生细调参考,并基于所述粗调参考和所述细调参考产生所述参考电压输出;

12.其中,(n+m)为所述数字控制信号的字长,且n、m均为大于等于1的正整数。

13.可选地,所述电阻型数模转换模块包括:

14.分压电阻网络,用于对初始电压进行电阻分压并产生第一电压和第二电压,其中,

所述第一电压大于所述第二电压;

15.所述高位电阻网络和所述低位电阻网络串联于所述第一电压和所述第二电压之间,且所述高位电阻网络在下,所述低位电阻网络在上;其中,所述高位电阻网络用于根据所述n位高位控制信号进行电阻接入控制并产生所述粗调参考输出,所述低位电阻网络用于根据所述m位低位控制信号进行电阻接入控制并产生所述细调参考输出;

16.运算单元,连接所述高位电阻网络和所述低位电阻网络的输出端,用于对所述粗调参考和所述细调参考进行加法相关运算并产生所述参考电压输出。

17.可选地,所述高位电阻网络包括:

18.由2n个单位电阻构成的高位电阻串,其中,2n个单位电阻依次串联于所述低位电阻网络和所述第二电压之间;

19.(2

n-1)个高位控制开关,与后(2

n-1)个单位电阻一一对应,且并联于相应单位电阻的两端;

20.高位接入逻辑控制单元,连接(2

n-1)个高位控制开关的控制端,用于对所述n位高位控制信号进行逻辑处理以控制(2

n-1)个高位控制开关。

21.可选地,所述低位电阻网络包括:

22.由(2

m-1)个单位电阻构成的低位电阻串,其中,(2

m-1)个单位电阻依次串联于所述第一电压和所述高位电阻网络之间;

23.(2

m-2)个低位控制开关,与后(2

m-2)个单位电阻一一对应,且并联于相应单位电阻的两端;

24.低位接入逻辑控制单元,连接(2

m-2)个低位控制开关的控制端,用于对所述m位低位控制信号进行逻辑处理以控制(2

m-2)个低位控制开关。

25.可选地,所述电阻型数模转换模块还包括:辅助电阻网络,并联于所述低位电阻串的两端,用于调节所述低位电阻网络的精度;其中,所述辅助电阻网络的阻值为单位电阻的2倍。

26.可选地,所述辅助电阻网络包括2个串联的单位电阻。

27.可选地,所述运算单元包括:第一运算放大器、第二运算放大器、第一电阻、第二电阻及第一电容;所述第一运算放大器的同相输入端接入所述低位参考,反相输入端连接其输出端并连接所述第一电阻的第一端;所述第一电阻的第二端连接所述第二运算放大器的反相输入端及第二电阻的第一端;所述第二运算放大器的同相输入端接入所述高位参考,输出端连接所述第二电阻的第二端并产生所述参考电压输出;所述第一电容并联于所述第二电阻的两端。

28.可选地,所述第一电阻和所述第二电阻的阻值相等。

29.可选地,所述数字处理模块基于高位搜索策略产生所述n位高位控制信号,基于低位搜索策略产生所述m位低位控制信号;其中,所述高位搜索策略包括二分法或累加法,所述低位搜索策略包括二分法或累加法。

30.如上所述,本发明的一种逐次逼近型模数转换器,利用高位电阻网络和低位电阻网络构成的两段式电阻串来产生逐次逼近的参考电压,避免了漏电问题,更适合深亚微米集成电路工艺;同时,还避免了电荷转移的模拟操作,从而对寄生电容不敏感,特别适合于电路工作环境更加复杂的应用场景,如片上系统soc。本发明产生的参考电压具有天然的单

调特性,是传统逐次逼近型模数转换器所不具备的优点。

附图说明

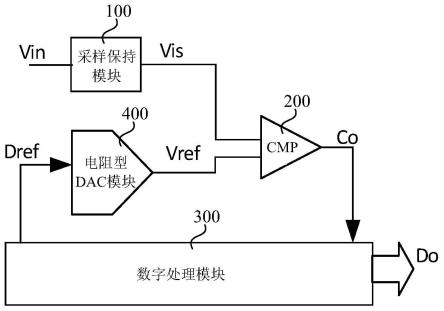

31.图1显示为本发明逐次逼近型模数转换器的电路框图。

32.图2显示为本发明逐次逼近型模数转换器中电阻型数模转换模块的原理图。

33.图3显示为本发明逐次逼近型模数转换器中电阻型数模转换模块的具体电路图。

34.元件标号说明

35.100采样保持模块

36.200比较模块

37.300数字处理模块

38.400电阻型数模转换模块

39.401分压电阻网络

40.402高位电阻网络

41.403低位电阻网络

42.404运算单元

具体实施方式

43.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

44.请参阅图1至图3。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

45.如图1和图2所示,本实施例提供一种逐次逼近型模数转换器,包括:采样保持模块100、比较模块200、数字处理模块300及电阻型数模转换模块400。

46.所述采样保持模块100用于对输入电压vin进行采样保持并产生采样电压vis输出。实际应用中,所述采样保持模块100可采用现有任一种采样保持电路来实现,本实施例对此不做限制。

47.所述比较模块200连接所述采样保持模块100的输出端,用于比较所述采样电压vis和参考电压vref并产生比较结果co输出。

48.具体的,所述比较模块200采用比较器cmp实现;其中,可以将所述比较器cmp的同相输入端连接所述采样保持模块100的输出端以接入所述采样电压vis,反相输入端连接所述电阻型数模转换模块400的输出端以接入所述参考电压vref,输出端产生所述比较结果co输出;当然,也可以将所述比较器cmp的同相输入端连接所述电阻型数模转换模块400的输出端以接入所述参考电压vref,反相输入端连接所述采样保持模块100的输出端以接入所述采样电压vis,这对本实施例没有影响。

49.本示例中,所述比较器cmp的同相输入端接入所述采样电压vis,反相输入端接入

所述参考电压vref;若所述采样电压vis大于所述参考电压vref,则所述比较器cmp输出高电平,反之,若所述采样电压vis小于所述参考电压vref,则所述比较器cmp输出低电平。

50.所述数字处理模块300连接所述比较模块200的输出端,用于根据所述比较结果co产生数字控制信号dref输出,所述数字控制信号dref包括n位高位控制信号msb和m位低位控制信号lsb,其中,(n+m)为所述数字控制信号dref的字长,且n、m均为大于等于1的正整数。进一步的,所述数字处理模块300还用于根据所述比较结果产生最终的数字转换结果do输出。

51.具体的,所述数字处理模块300基于高位搜索策略产生所述n位高位控制信号msb,基于低位搜索策略产生所述m位低位控制信号lsb;其中,所述高位搜索策略包括二分法或累加法,所述低位搜索策略包括二分法或累加法。

52.实际应用中,所述高位搜索策略和所述低位搜索策略可以相同,也可以不同,如所述高位搜索策略和所述低位搜索策略相同,均为二分法或累加法,或者,所述高位搜索策略和所述低位搜索策略不同,其中一个为二分法,另一个为累积法;当然,所述高位搜索策略和所述低位搜索策略也可以根据具体应用场景做调整,选用除二分法和累加法之外的其它逐次逼近策略。

53.所述电阻型数模转换模块400连接于所述数字处理模块300和所述比较模块200之间,用于根据所述n位高位控制信号msb控制高位电阻网络402产生粗调参考cref,根据所述m位低位控制信号lsb控制低位电阻网络403产生细调参考fref,并基于所述粗调参考cref和所述细调参考fref产生所述参考电压vref输出。

54.具体的,如图3所示,所述电阻型数模转换模块400包括:分压电阻网络401、高位电阻网络402、低位电阻网络403及运算单元404。进一步的,所述电阻型数模转换模块400还包括:辅助电阻网络405。

55.所述分压电阻网络401用于对初始电压vdd进行电阻分压并产生第一电压va和第二电压vb,其中,所述第一电压va大于所述第二电压vb。

56.更具体的,所述分压电阻网络401由若干分压电阻串联形成,其中,若干分压电阻可以选用阻值完全相同的电阻,也可以选用阻值部分相同,甚至完全不同的电阻,这对本实施例没有影响。需要说明的是,图3中分压电阻ra、rb、rc仅是示例,并非代表所述分压电阻网络401只包括三个分压电阻,实际上,所述分压电阻网络401中串联的分压电阻的数量应大于等于3。

57.需要说明的是,所述第一电压va和所述第二电压vb的取值决定了所述参考电压vref的范围,从而决定了所述输入电压vin的范围,故,实际应用中,应根据具体需求来选择分压电阻的数量和阻值,以便于得到所需数值的第一电压va和第二电压vb。

58.所述高位电阻网络402和所述低位电阻网络403串联于所述第一电压va和所述第二电压vb之间,且所述高位电阻网络402在下,所述低位电阻网络401在上;其中,所述高位电阻网络402用于根据所述n位高位控制信号msb进行电阻接入控制并产生所述粗调参考cref输出,所述低位电阻网络403用于根据所述m位低位控制信号lsb进行电阻接入控制并产生所述细调参考fref输出。

59.更具体的,所述高位电阻网络402包括:由2n个单位电阻r0构成的高位电阻串、(2

n-1)个高位控制开关及高位接入逻辑控制单元;其中,2n个单位电阻r0依次串联于所述低位

电阻网络403和所述第二电压vb之间,(2

n-1)个所述高位控制开关与后(2

n-1)个单位电阻r0一一对应,且并联于相应单位电阻r0的两端,所述高位接入逻辑控制单元连接(2

n-1)个所述高位控制开关的控制端,用于对所述n位高位控制信号msb进行逻辑处理以控制(2

n-1)个所述高位控制开关。

60.所述低位电阻网络403包括:由(2

m-1)个单位电阻r0构成的低位电阻串、(2

m-2)个低位控制开关及低位接入逻辑控制单元;其中,(2

m-1)个单位电阻r0依次串联于所述第一电压va和所述高位电阻网络402之间,(2

m-2)个所述低位控制开关与后(2

m-2)个单位电阻r0一一对应,且并联于相应单位电阻r0的两端,所述低位接入逻辑控制单元连接(2

m-2)个低位控制开关的控制端,用于对所述m位低位控制信号lsb进行逻辑处理以控制(2

m-2)个低位控制开关。

61.需要说明的是,此处所述单位电阻r0是指阻值为一已知值的电阻,而具体阻值大小则根据实际需求来设定,本实施例对此不做限制。

62.所述运算单元404连接所述高位电阻网络402和所述低位电阻网络403的输出端,用于对所述粗调参考cref和所述细调参考fref进行加法相关运算并产生所述参考电压vref输出。本实施例利用产生机制中的加法特性,使得所述参考电压vref具有单调性。

63.更具体的,所述运算单元可采用跨导放大电路、电流镜电路、运放电路等实现,当然,其它可实现加法相关运算的电路也同样适用于本实施例。可选地,本实施例中,所述运算单元采用运放电路实现。

64.所述运算单元404包括:第一运算放大器op1、第二运算放大器op2、第一电阻r1、第二电阻r2及第一电容c1;所述第一运算放大器op1的同相输入端接入所述低位参考fref,反相输入端连接其输出端并连接所述第一电阻r1的第一端;所述第一电阻r1的第二端连接所述第二运算放大器op2的反相输入端及所述第二电阻r2的第一端;所述第二运算放大器op2的同相输入端接入所述高位参考cref,输出端连接所述第二电阻r2的第二端并产生所述参考电压vref输出;所述第一电容c1并联于所述第二电阻r2的两端。其中,所述第一电阻r1和所述第二电阻r2的阻值相等。

65.所述辅助电阻网络405并联于所述低位电阻串的两端,用于调节所述低位电阻网络403的精度,使其最小调节量小于单位电阻r0;其中,所述辅助电阻网络405的阻值为单位电阻r0的2倍。更具体的,所述辅助电阻网络405包括2个串联的单位电阻r0。

66.下面请结合图1-图3,以12位精度的电阻型数模转换模块400为例,对本实施例的逐次逼近型模数转换器的性能进行说明。

67.其中,初始电压vdd=3v,第一电压va=2.8v,第二电压vb=1.497v;数字控制信号dref的字长为12位,高位控制信号msb的字长为8位,即n=8,低位控制信号lsb的字长为4位,即m=4,因此,高位电阻网络402中串联的单位电阻r0的数量为28=256个,低位电阻网络403中串联的单位电阻r0的数量为2

4-1=15个;同时,为了保证低位电阻网络403的精度要求,在其两端并联一个阻值为2r0的电阻。

68.基于图3所示电阻型数模转换模块400的具体电路可知:

69.[0070][0071][0072]

其中,且msb和lsb满足公式a=2m*msb+ls,a为数字控制信号dref对应的十进制数。

[0073]

可见,利用高位电阻网络和低位电阻网络构成的两段式电阻串来产生逐次逼近的参考电压,避免了漏电问题和寄生问题;更由于参考电压vref产生机制中的加法特性,使其具有单调性,这样,在比较器的性能得到保证的情况下,整体adc的输出特性可以大大提高。

[0074]

综上所述,本发明的一种逐次逼近型模数转换器,利用高位电阻网络和低位电阻网络构成的两段式电阻串来产生逐次逼近的参考电压,避免了漏电问题,更适合深亚微米集成电路工艺;同时,还避免了电荷转移的模拟操作,从而对寄生电容不敏感,特别适合于电路工作环境更加复杂的应用场景,如片上系统soc。本发明产生的参考电压具有天然的单调特性,是传统逐次逼近型模数转换器所不具备的优点。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0075]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1