功率半导体装置的制作方法

1.本发明涉及功率半导体装置。

背景技术:

2.在专利文献1中公开了对并联连接的si-igbt和sic-mosfet进行驱动的驱动装置。si-igbt是使用si作为半导体材料的igbt(insulated gate bipolar transistor)。sic-mosfet是使用sic作为半导体材料的mosfet(metal oxide semiconductor field effect transistor)。就专利文献1的驱动装置而言,如果过电流流过si-igbt和sic-mosfet的任意者,则通过将短路耐量低的sic-mosfet先行切换为断开状态而对sic-mosfet进行保护。

3.专利文献1:日本特开2020-141550号公报

4.专利文献1的驱动装置在将sic-mosfet切换为断开状态之后,将si-igbt也切换为断开状态。因此,功率半导体装置的短路耐量被耐量低的sic-mosfet限制。

技术实现要素:

5.本发明就是为了解决上述问题而提出的,其目的在于降低功率半导体装置的损耗及提高短路耐量。

6.本发明的功率半导体装置具有:第1开关元件;第2开关元件,其与第1开关元件并联连接,短路耐量比第1开关元件高;驱动电路,其对第1开关元件及第2开关元件进行驱动;以及判定电路,其将流过第1开关元件及第2开关元件的电流的合计即对象电流与第1阈值及大于第1阈值的第2阈值进行比较,如果由判定电路判定为对象电流大于或等于第1阈值,则驱动电路将第1开关元件设为断开状态,如果由判定电路判定为对象电流大于或等于第2阈值,则驱动电路将第2开关元件设为断开状态。

7.发明的效果

8.根据本发明的功率半导体装置,通过适当地设定第1阈值及第2阈值,从而实现损耗的降低及短路耐量的提高。

附图说明

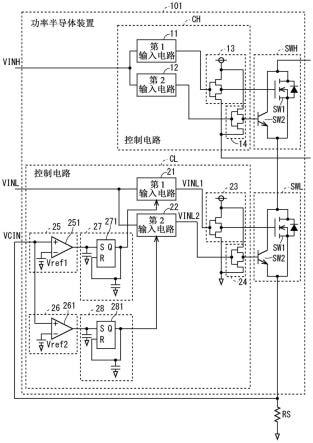

9.图1是表示实施方式1的功率半导体装置的结构的图。

10.图2是表示实施方式1的功率半导体装置的短路动作时的时序的图。

11.图3是表示实施方式1的功率半导体装置的短路动作时的时序的图。

12.图4是表示实施方式2的功率半导体装置的结构的图。

13.图5是表示流过开关元件的电流与接通电压之间的关系的图。

具体实施方式

14.<a.实施方式1>

15.<a-1.结构>

16.图1示出实施方式1的功率半导体装置101的结构。功率半导体装置101具有开关部swh、swl和控制电路ch、cl。开关部swh构成上桥臂。开关部swl构成下桥臂。控制电路ch对开关部swh进行控制。控制电路cl对开关部swl进行控制。在图1中仅示出功率半导体装置101的v相的结构。在u相、v相及w相各相中,开关部swh与开关部swl串联连接。

17.开关部swh呈与开关部swl相同的结构,因此,下面仅对开关部swh的结构进行说明。开关部swh具有第1开关元件sw1及第2开关元件sw2。第1开关元件sw1与第2开关元件sw2并联连接。第1开关元件sw1与第2开关元件sw2相比短路耐量小。在本实施方式中,第1开关元件sw1是sic-mosfet,第2开关元件sw2是si-igbt。在第1开关元件sw1形成有体二极管。sic-mosfet的漏极电极与si-igbt的集电极(collector)电极(electrode)连接,sic-mosfet的源极电极与si-igbt的发射极电极连接。此外,第1开关元件sw1不限于sic-mosfet,也可以是使用了除sic以外的宽带隙半导体的mosfet。

18.控制电路ch基于从功率半导体装置101的外部输入的输入信号vinh向开关部swh的第1开关元件sw1及第2开关元件sw2的栅极端子输出控制信号,对开关部swh的第1开关元件sw1及第2开关元件sw2的接通状态和断开状态进行切换。

19.控制电路ch具有第1输入电路11、第2输入电路12、第1驱动电路13及第2驱动电路14。第1输入电路11接收输入信号vinh,生成向第1驱动电路13输入的信号。第2输入电路12接收输入信号vinh,生成向第2驱动电路14输入的信号。第1驱动电路13接收来自第1输入电路11的信号,向第1开关元件sw1的栅极端子输出控制信号,由此对第1开关元件sw1的接通状态和断开状态进行切换。第2驱动电路14接收来自第2输入电路12的信号,向第2开关元件sw2的栅极端子输出控制信号,由此对第2开关元件sw1的接通状态和断开状态进行切换。

20.控制电路cl基于从功率半导体装置101的外部输入的输入信号vinl向开关部swl的第1开关元件sw1及第2开关元件sw2的栅极端子输出控制信号,对开关部swl的第1开关元件sw1及第2开关元件sw2的接通状态和断开状态进行切换。

21.除了第1输入电路21、第2输入电路22、第1驱动电路23及第2驱动电路24以外,控制电路cl还具有第1判定电路25、第2判定电路26、第1保护电路27及第2保护电路28。第1输入电路21、第2输入电路22、第1驱动电路23及第2驱动电路24分别呈与控制电路ch的第1输入电路11、第2输入电路12、第1驱动电路13及第2驱动电路14相同的结构。但是,向第1输入电路21及第2输入电路22输入来自第1保护电路27及第2保护电路28的输出。

22.第1判定电路25及第2判定电路26对开关部swl的短路状态进行判定,分别通知给第1保护电路27及第2保护电路28。开关部swl的第1开关元件sw1的源极电极与第2开关元件sw2的发射极电极经由电阻rs而接地。由于在开关部swl中在第1开关元件sw1和第2开关元件sw2的并联连接体流过的电流即对象电流而在电阻rs的两端产生电压降。换言之,电阻rs将对象电流转换为电压。在实施方式1中,对象电流是第1开关元件sw1的主电流与第2开关元件sw2的主电流的合计。通过电阻rs转换后的电压被作为电压信号vcin而输入至第1判定电路25及第2判定电路26。

23.第1判定电路25构成为具有比较器251。向比较器251的负极输入阈值电压vref1,向正极输入电压信号vcin。比较器251将电压信号vcin与阈值电压vref1进行比较,如果电压信号vcin大于或等于阈值电压vref1,则输出高电平的信号。该信号被输入至第1保护电路27的输入端子s。这样,第1判定电路25根据电压信号vcin大于或等于阈值电压vref1这一

点而判定为开关部swl处于短路状态,将该内容通知给第1保护电路27。换言之,第1判定电路25根据对象电流大于或等于与阈值电压vref1对应的第1阈值这一点而判定短路状态。在实施方式1中,阈值电压vref1设定为大于或等于由于与第1开关元件sw1的额定电流相当的对象电流而在电阻rs的两端产生的电压降的值。

24.第2判定电路26构成为具有比较器261。向比较器261的负极输入阈值电压vref2,向正极输入电压信号vcin。比较器261将电压信号vcin与阈值电压vref2进行比较,如果电压信号vcin大于或等于阈值电压vref2,则输出高电平的信号。该信号被输入至第2保护电路28的输入端子s。这样,第2判定电路26根据电压信号vcin大于或等于阈值电压vref2这一点而判定为开关部swl处于短路状态,将该内容通知给第2保护电路28。由于阈值电压vref2大于阈值电压vref1,因此,第2判定电路26与第1判定电路25相比,较晚地进行短路状态的判定。换言之,第2判定电路26根据对象电流大于或等于与阈值电压vref2对应的第2阈值这一点而判定短路状态。在实施方式1中,阈值电压vref2设定为大于或等于由于与第2开关元件sw2的额定电流相当的对象电流而在电阻rs的两端产生的电压降的值。

25.第1保护电路27构成为具有滤波器和锁存电路271。滤波器用于防止由噪声导致的误判定。锁存电路271使由第1判定电路25作出的短路判定保持一定期间。当在某个滤波时间之后电压信号vcin依然大于或等于阈值电压vref1的情况下,锁存电路271从输出端子q输出高电平的信号,对在第1输入电路21产生了短路电流这一情况进行通知。

26.第2保护电路28构成为具有滤波器和锁存电路281。滤波器用于防止由噪声导致的误判定。锁存电路281使由第2判定电路26作出的短路判定保持一定期间。当在某个滤波时间之后电压信号vcin仍然大于或等于阈值电压vref2的情况下,锁存电路281从输出端子q输出高电平的信号,对在第2输入电路22产生了短路电流这一情况进行通知。

27.向第1输入电路21输入输入信号vinl和来自锁存电路271的输出信号。在锁存电路271的输出是低电平的情况下,第1输入电路21的输出信号vinl1是将输入信号vinl一定程度延迟后的信号。在锁存电路271的输出是高电平的情况下,第1输入电路21的输出信号vinl1与输入信号vinl无关,是低电平。第1驱动电路23如果接收到低电平的输入,则将低电平的信号输出至开关部swl的第1开关元件sw1的栅极端子。由此,第1开关元件sw1成为断开状态。

28.向第2输入电路22输入输入信号vinl和来自锁存电路281的输出信号。在锁存电路281的输出是低电平的情况下,第2输入电路22的输出信号vinl2与输入信号vinl同步,如果输入信号vinl是低电平则输出信号vinl2是低电平,如果输入信号vinl是高电平则输出信号vinl2是高电平。在第2输入电路22中与第1输入电路21不同,相对于输入信号没有产生输出信号的延迟,或者即使产生延迟,延迟量也比第1输入电路21小。因此,在开关部swl的接通时,第2开关元件sw2比第1开关元件sw1先行成为接通状态。由此,能够防止过电流流过短路耐量低的第1开关元件sw1。

29.在锁存电路281的输出是高电平的情况下,第2输入电路22的输出信号vinl2与输入信号vinl无关,为低电平。第2驱动电路24如果接收到低电平的输入,则将低电平的信号输出至开关部swl的第2开关元件sw2的栅极端子。由此,第2开关元件sw2成为断开状态。如上所述,第2判定电路26与第1判定电路25相比较晚地进行短路状态的判定,因此,第2开关元件sw2与第1开关元件sw1相比较晚地成为断开状态。由此,能够防止过电流流过短路耐量

低的第1开关元件sw1。

30.将从锁存电路271、281的输出端子q输出的高电平的信号也称为短路通知信号。在从短路通知信号的输出算起的一定期间之后,向锁存电路271、281的复位端子r输入复位信号。由此,锁存电路271、281的输出端子q的信号从高电平变化为低电平。换言之,第1保护电路27及第2保护电路28解除短路判定。并且,开关部swl恢复为通常的通断动作。

31.<a-2.动作>

32.图2及图3示出功率半导体装置101的短路动作时的时序。图2示出短路电流大且开关部swl的第1开关元件sw1及第2开关元件sw2均成为断开状态的情况。

33.如果在第1开关元件sw1及第2开关元件sw2产生短路电流,则在第1开关元件sw1产生的短路电流与在第2开关元件sw2产生的短路电流之和流过电阻rs,在电阻rs的两端产生电压降。与该电压降相当的电压值成为电压信号vcin而被输入至第1判定电路25及第2判定电路26。如果电压信号vcin大于或等于阈值电压vref1,则第1判定电路25输出高电平的信号。如果第1判定电路25的输出以一定期间维持高电平,即如果电压信号vcin大于或等于阈值电压vref1的期间持续了一定期间,则第1保护电路27将高电平的信号即短路通知信号输出至第1输入电路21。由此,第1输入电路21的输出成为低电平,第1驱动电路23的输出成为低电平。其结果,第1开关元件sw1成为断开状态。

34.然后,如果短路电流增加,电压信号vcin大于或等于阈值电压vref2,则第2判定电路26输出高电平的信号。如果第2判定电路26的输出以一定期间维持高电平,即如果电压信号vcin大于或等于阈值电压vref2的期间持续了一定期间,则第2保护电路28将高电平的信号即短路通知信号输出至第2输入电路22。由此,第2输入电路22的输出成为低电平,第2驱动电路24的输出成为低电平。其结果,第2开关元件sw2成为断开状态。这里,从产生短路电流起至第1开关元件sw1成为断开状态为止的时间t1比从产生短路电流起至第2开关元件sw2成为断开状态为止的时间t2短。

35.图3示出短路电流小于图2的例子且仅开关部swl的第1开关元件sw1成为断开状态的情况。在vref1<vcin<vref2的情况下,功率半导体装置101仅将第1开关元件sw1设为断开状态,仅第2开关元件sw2通电。

36.<a-3.效果>

37.实施方式1的功率半导体装置101具有:第1开关元件sw1;第2开关元件sw2,其与第1开关元件sw1并联连接,短路耐量比第1开关元件sw1高;驱动电路23、24,它们对第1开关元件sw1及第2开关元件sw2进行驱动;以及判定电路25、26,它们将流过第1开关元件sw1及第2开关元件sw2的电流的合计即对象电流与第1阈值及比第1阈值大的第2阈值进行比较,如果由判定电路25、26判定为对象电流大于或等于第1阈值,则驱动电路23、24将第1开关元件sw1设为断开状态,如果由判定电路25、26判定为对象电流大于或等于第2阈值,则驱动电路23、24将第2开关元件sw2设为断开状态。因此,根据功率半导体装置101,通过适当地设定判定电路25、26的第1阈值及第2阈值,从而能够在短路电流流过时,仅切断第1开关元件sw1。其结果,能够防止短路耐量低的第1开关元件sw1的破坏,并且通过第2开关元件sw2而决定功率半导体装置101整体的短路耐量。其结果,容易将功率半导体装置101整体的短路耐量设计得高。

38.<b.实施方式2>

39.<b-1.结构>

40.图4示出实施方式2的功率半导体装置102的结构。功率半导体装置102与实施方式1的功率半导体装置101同样地,具有开关部swh、swl和控制电路ch、cl,但在图4中仅示出与下桥臂相关的开关部swl及控制电路cl的结构。功率半导体装置102的与上桥臂相关的开关部swh及控制电路ch的结构与功率半导体装置101相同。

41.就功率半导体装置102的开关部swl而言,第1开关元件sw1被划分为主单元sw11和感测单元sw12。并且,感测单元sw12的电流与第2开关元件sw2的感测电流的合计值通过电阻rsense而被转换为电压值,成为电压信号vcin。除此以外,功率半导体装置102与实施方式1的功率半导体装置101相同。

42.<b-2.效果>

43.即,就实施方式2的功率半导体装置102而言,成为判定电路25、26的判定所使用的电压信号vcin的基础的对象电流是流过第1开关元件sw1及第2开关元件sw2的感测电流的合计。由此,功率半导体装置102能够在自身的内部生成电压信号vcin。因此,根据功率半导体装置102,除了实施方式1的功率半导体装置101的效果以外,还能够削减外部输入端子。

44.<c.实施方式3>

45.<c-1.结构>

46.实施方式3的功率半导体装置是与图1所示的实施方式1的功率半导体装置101或者图4所示的实施方式2的功率半导体装置102相同的结构。在实施方式1、2中,说明了当在开关部swl的第1开关元件sw1及第2开关元件sw2的并联连接体流过短路电流等过电流的情况下,优先地将第1开关元件sw1设为断开状态。该优先地将第1开关元件sw1设为断开状态的动作不限于流过过电流的情况,在功率半导体装置的通常的通断动作时也是有效的。因此,在实施方式3中,第1判定电路25的阈值电压vref1设定于通常的动作区域而非开关部swl的短路动作。

47.图5示出流过第1开关元件sw1及第2开关元件sw2的电流与接通电压之间的关系。接通电压在第1开关元件sw1中是漏极-源极间接通电压vds(on),在第2开关元件sw2中是集电极-发射极间饱和电压vce(sat)。在图5中,ir示出第1开关元件sw1的额定电流,i1示出比额定电流ir小的预先确定的电流值,i2示出额定电流ir的2倍的电流。

48.在图5中,将针对相同电流而第1开关元件sw1的漏极-源极间接通电压vds(on)小于第2开关元件sw2的集电极-发射极间饱和电压vce(sat)的区域设为低电流区域a,将低电流区域a中的上限电流设为i1。在低电流区域a中,mosfet的接通电阻小于igbt的接通电阻,因此,与igbt相比,电流更多地流过mosfet。

49.另一方面,将针对相同电流而第1开关元件sw1的漏极-源极间接通电压vds(on)大于第2开关元件sw2的集电极-发射极间饱和电压vce(sat)的区域称为高电流区域。低电流区域a在功率半导体装置的使用动作条件下最有助于损耗改善。因此,在第1开关元件sw1是接通电阻小的sic-mosfet等宽带隙元件的情况下,在低电流区域a中电流大量地流过第1开关元件sw1,由此,改善了作为功率半导体装置的损耗。

50.另外,在高电流区域中在第2开关元件sw2即si-igbt流过大量电流,因此,由第1开关元件sw1使用宽带隙半导体带来的损耗改善效果小。

51.因此,在实施方式3中,第1判定电路25的阈值电压vref1被设定为与i1相当的值。

即,在作为实施方式3而采用实施方式1的结构的情况下,设为vref1=i1

×

rs。另外,在作为实施方式3而采用实施方式2的结构的情况下,设为vref1=i1

×

rsense。由此,在无助于损耗改善的高电流区域中以第1开关元件即sic-mosfet不会积极地接通的方式而进行控制。其结果,能够提高短路耐量低的器件的针对过电流的耐量。

52.此外,能够对各实施方式自由地进行组合,或对各实施方式适当地进行变形、省略。

53.标号的说明

54.11第1输入电路,12第2输入电路,13第1驱动电路,14第2驱动电路,21第1输入电路,22第2输入电路,23第1驱动电路,24第2驱动电路,25第1判定电路,26第2判定电路,27第1保护电路,28第2保护电路,101、102功率半导体装置,251、261比较器,271、281锁存电路,ch、cl控制电路,sw1第1开关元件,sw2第2开关元件,swh、swl开关部。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1