一种峰值检波器和峰值检波方法与流程

1.本发明属于峰值检波器技术领域,具体涉及一种峰值检波器和峰值检波方法。

背景技术:

2.高性能峰值检波器作为子电路单元广泛应用于各种通信系统中。通信系统中峰值检波器可用于协助判断通信信道是否正常,如峰值检波器监测到信号幅度低于某一设定的幅度时即认为信号中断或用户掉线。高速高精度峰值检波器可大大减少通信系统信号有无的诊断时间,提高网络效率。

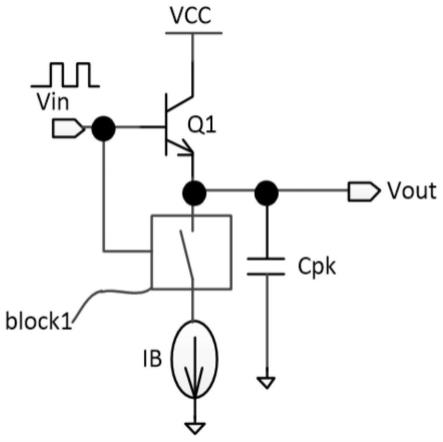

3.图1(a)为传统检波器电路原理图,传统检波器监测速度与监测精度相互制约。输入信号上升或处于峰值时段,峰值检波器q1快速将输出电容cpk充电至峰值;当输入信号处于非峰值时段,采样电容cpk保持检测到的峰值电压,但是由于偏置电流ib的放电作用,采样电容cpk上的检测电压持续下降,直到下一个峰值到来。传统检波器的工作原理导致检波器输出电压vout上不可避免的存在纹波。为了提高工作速度,需要适当提高偏置电流ib,而 ib的提高则导致输出纹波变大。

技术实现要素:

4.解决的技术问题:基于前述技术问题,本发明公开了一种峰值检波器和峰值检波方法,在高速检波时具有更高的检测精度。

5.技术方案:

6.一种峰值检波器,所述峰值检波器包括信号输入端、信号输出端、第一三极管(q1)、采样电容(cpk)和偏置电流控制电路(block1);

7.所述第一三极管(q1)的基极与信号输入端连接,用于接收输入信号(vin);第一三极管(q1)的集电极接电源电压,第一三极管(q1)的发射极分别与偏置电流控制电路(block1)、采样电容(cpk)和信号输出端连接,采样电容(cpk)不与第一三极管(q1)的发射极连接的端子接地,偏置电流控制电路(block1)与第一偏置电路连接;

8.其中,当输入信号(vin)处于待测峰值时段时,偏置电流控制电路(block1)连通第一偏置电路,将偏置电流(ib)接入第一三极管(q1)的发射极,信号输出端输出检波信号(vout);当输入信号(vin)处于非待测峰值时段时,偏置电流控制电路(block1)同时断开第一偏置电路和第一三极管(q1)。

9.进一步地,所述偏置电流控制电路(block1)包括第二三极管(q2)、第三三极管(q3)、第四三极管(q4)、第二偏置电路;

10.所述第二三极管(q2)的基极与信号输入端连接,第二三极管(q2)的发射极分别与第二偏置电路和第三三极管(q3)的基极连接,第二三极管(q2)的集电极与电源电压连接;

11.所述第三三极管(q3)的集电极和第四三极管(q4)的基极均与第一三极管(q1)的发射极连接,第三三极管(q3)的发射极和第四三极管(q4)的发射极均与第一偏置电路连接;第四三极管(q4)的集电极与电源电压连接;

12.当输入信号(vin)处于待测峰值时段时,第三三极管(q3)、第四三极管(q4)处于开启状态,由第一三极管(q1)对采样电容(cpk)充电;当输入信号(vin)处于非待测峰值时段时,第一三极管(q1)和第三三极管(q3)处于关闭状态,第四三极管(q4)处于开启状态,采样电容(cpk)电压保持。

13.进一步地,所述偏置电流控制电路(block1)包括电阻、滤波电容、第三三极管(q3)、第四三极管(q4)、第二偏置电路;

14.所述滤波电容的两端分别与信号输入端、第三三极管(q3)的基极连接;电阻的一端与第三三极管(q3)的基极连接,另一端与偏置电压连接;

15.所述第三三极管(q3)的集电极和第四三极管(q4)的基极均与第一三极管(q1)的发射极连接,第三三极管(q3)的发射极和第四三极管(q4)的发射极均与第一偏置电路连接;第四三极管(q4)的集电极与电源电压连接;

16.当输入信号(vin)处于待测峰值时段时,第三三极管(q3)、第四三极管(q4)处于开启状态,由第一三极管(q1)对采样电容(cpk)充电;当输入信号(vin)处于非待测峰值时段时,第一三极管(q1)和第三三极管(q3)处于关闭状态,第四三极管(q4)处于开启状态,采样电容(cpk)电压保持。

17.进一步地,所述峰值检波器中采用的三极管采用npn型三极管、pnp型三极管、pmos 型三极管、nmos型三级管、绝缘栅双极晶体管中的一种。

18.一种差分峰值检波器,所述差分峰值检波器包括对称设置的两个峰值检波器;

19.所述峰值检波器采用如前所述的峰值检波器,且两个峰值检波器共用同一个采样电容 (cpk)。

20.一种基于前述峰值检波器的峰值检波方法,所述峰值检波方法包括以下步骤:

21.当输入信号(vin)处于峰值检测时段时,偏置电流控制电路(block1)连通第一偏置电路,将偏置电流(ib)接入第一三极管(q1)的发射极,信号输出端输出检波信号(vout),同时对采样电容(cpk)进行充电;当输入信号(vin)处于非峰值检测时段时,偏置电流控制电路(block1)同时断开第一偏置电路和第一三极管(q1),采样电容(cpk)保持上一峰值的检波电压,直至下一个峰值检测时段。

22.有益效果:

23.第一,本发明的峰值检波器,在传统检波器基础上引入偏置电流控制电路block1,在无信号和峰值检测阶段保持检测电路q1偏置电流不变从而实现高速检测;在非信号进入谷底或负峰值阶段关闭偏置电流,采样电容cpk上无放电电流,从而保持检波信号不变;偏置电流控制电路block1的引入大大提高了高速检波器的检测精度。

24.第二,本发明的峰值检波器,能够解决传统检波器高速检波与高精度之间的冲突问题,采用本发明的检波器技术可以实现高速检波的同时保持高精度。

25.第三,本发明的峰值检波器具有广泛的应用,例如,可以用于pon系统中监测突发用户数据包是否有效;也可以用于高速agc(自动增益控制)环路中检测信号幅度等。

附图说明

26.图1(a)为传统的峰值检波器的结构示意图;

27.图1(b)为本实施例的峰值检波器的结构示意图;

28.图2为其中一种偏置电流控制电路的结构示意图;

29.图3为传统检波器和本实施例的检波器的仿真结果对比示意图;

30.图4(a)至图4(d)为本实施例的峰值检波器的部分检波实例示意图;图4(a)为基于 npn型三极管的差分正峰值检波器结构示意图;图4(b)为基于nmos型三极管的差分正峰值检波器结构示意图;图4(c)为基于ac耦合npn型三极管的单端正峰值检波器结构示意图;图4(d)为基于ac耦合nmos型三极管的单端正峰值检波器结构示意图。

具体实施方式

31.下面的实施例可使本专业技术人员更全面地理解本发明,但不以任何方式限制本发明。

32.图1(b)为本实施例的峰值检波器的结构示意图。参见图1(b),该峰值检波器包括信号输入端、信号输出端、第一三极管q1、采样电容cpk和偏置电流控制电路block1。

33.所述第一三极管q1的基极与信号输入端连接,用于接收输入信号vin;第一三极管q1 的集电极接电源电压,第一三极管q1的发射极分别与偏置电流控制电路block1、采样电容 cpk和信号输出端连接,采样电容cpk不与第一三极管q1的发射极连接的端子接地,偏置电流控制电路block1与第一偏置电路连接。

34.其中,当输入信号vin处于待测峰值时段时,偏置电流控制电路block1连通第一偏置电路,将偏置电流ib接入第一三极管q1的发射极,信号输出端输出检波信号vout;当输入信号vin处于非待测峰值时段时,偏置电流控制电路block1同时断开第一偏置电路和第一三极管q1。

35.在本实施例中,偏置电流控制电路block1的基本功能包括:1)信号vin处于待测峰值时段将偏置电流ib接入第一三极管q1的发射极,提高检波器工作速度,采样电容cpk上电压与输入信号vin相同;2)信号vin处于非待测峰值时段将偏置电流ib与第一三极管q1 断开或旁路掉,采样电容无放电路径精确维持采样峰值。从而,本实施例的峰值检波器在引入bolck1功能模块后,可以实现高速检波的同时保持较高的检波精度。

36.图2为其中一种偏置电流控制电路的结构示意图。第二三极管q2的基级接输入信号vin,发射级接第三三极管q3的基极和第二偏置电路,第二偏置电路为第二三极管q2提供偏置电流ib2;第三三极管q3的集电极接信号输出端,发射级接第三三极管q3的发射级;第四三极管q4的基极接信号输出端vout,集电极接电源电压vcc或其它。

37.在此结构基础上,峰值检波器的工作原理为:1)输入信号vin处于待测峰值时段,第三三极管q3、第四三极管q4同时开启,偏置电流ib的一半流过第一三极管q1,第一三极管 q1工作在高度等待状态,同时第一三极管q1对采样电容cpk进行充电,峰值检波器输出信号vout快速跟随输入信号vin上升。2)当输入信号vin处于非峰值时段,第一三极管q1、第三三极管q3关闭,第四三极管q4开启将偏置电流ib旁路掉,峰值检波器输出电压vout 由采样电容cpk保持。

38.图3为传统峰值检波器与本实施例的峰值检波器在相同输入条件下的检波特性仿真对比图:图3中黑色方波为输入信号vin,浅灰色波形为传统峰值检波器输出,深灰色波形为本实施例的峰值检波器输出。从图3中不难看出,本实施例的峰值检波器在高速检波时具有更高的检测精度。

39.图2仅为本实施例的峰值检波器的一种实施方案,图4(a)至图4(b)进一步给出了峰值检波器的其它几种典型实施方案。

40.应当理解,本实施例的峰值检波器的实施方案包括并不仅限于图2、图4(a)至图4(b) 所列的几种正峰值检波器。由于器件的可替代性和互补性,图2、图4(a)至图4(b)的峰值检波器实施方案可以简单的用pnp或pmos器件替换为对应的负峰值检波器和差分检波器;当采用pnp三极管或者pmos器件时,接地端和电源电压端更换连接方式,例如,与图4(c) 相对应的负峰值检波器,其中,第一三极管q1的集电极、第四三极管q4的集电极接地,第一偏置电路远离第三三极管q3的端子、采样电容远离信号输出端的端子与电源电压连接。本实施例的峰值检波器可以进一步优化成相应的正峰值检波器、负峰值检波器以及由此构建的峰峰值检波器(正峰值减负峰值)等等。

41.基于前述峰值检波器,本实施例提及一种峰值检波方法,该峰值检波方法包括以下步骤:

42.当输入信号vin处于峰值检测时段时,偏置电流控制电路block1连通第一偏置电路,将偏置电流ib接入第一三极管q1的发射极,信号输出端输出检波信号vout,同时对采样电容 cpk进行充电;当输入信号vin处于非峰值检测时段时,偏置电流控制电路block1同时断开第一偏置电路和第一三极管q1,采样电容cpk保持上一峰值的检波电压,直至下一个峰值检测时段。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1