半导体器件的制作方法、半导体器件及电子设备与流程

本公开涉及半导体,尤其涉及一种半导体器件的制作方法、半导体器件及电子设备。

背景技术:

1、随着现今科技快速的发展,半导体存储器被广泛地应用于电子装置中。动态随机存取存储器(dynamic random access memory,dram)属于一种挥发性存储器,对于储存大量数据的应用而言,动态随机存取存储器是最常被利用的解决方案。

2、通常,动态随机存取存储器是由多个存储单元构成,存储单元通常包括晶体管、电容等器件,各存储单元通过字线和位线进行数据的读取和写入。

3、然而,现有的动态随机存取存储器仍存在诸多问题。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开提供一种半导体器件的制作方法、半导体器件及电子设备。

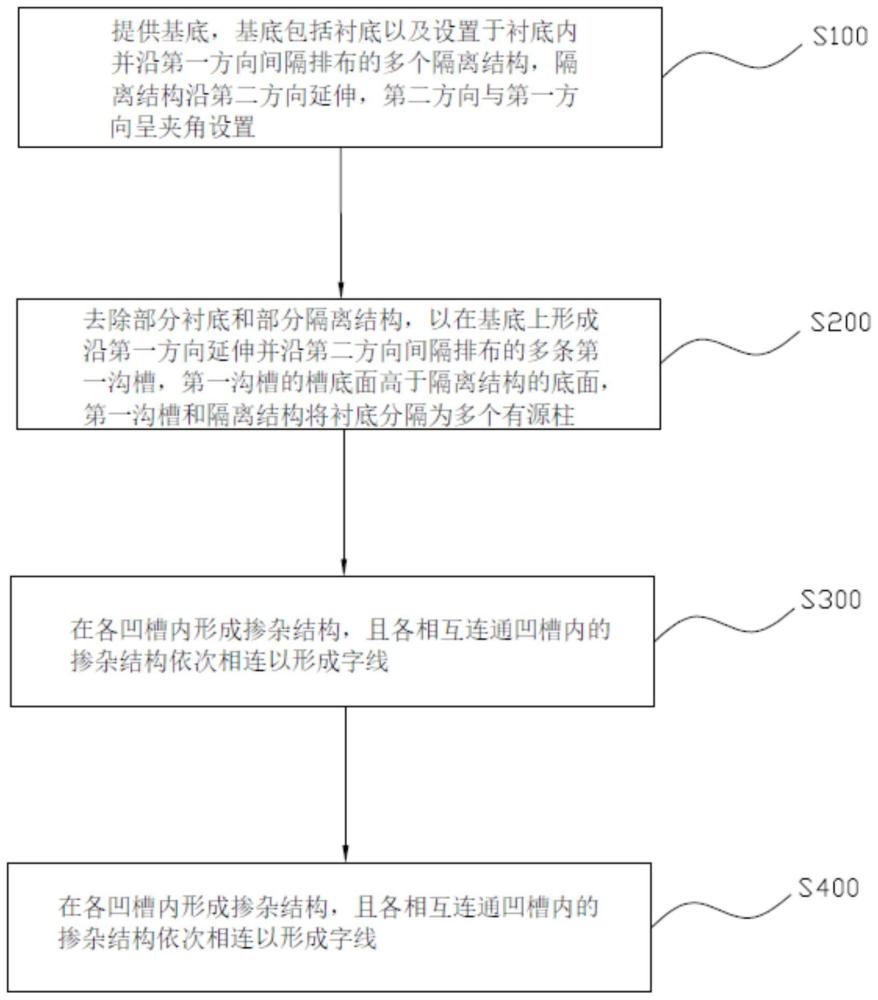

3、本公开的第一方面,提供一种半导体器件的制作方法,所述半导体器件的制作方法包括:

4、所述半导体器件的制作方法包括:

5、提供基底,所述基底包括衬底以及设置于所述衬底内并沿第一方向间隔排布的多个隔离结构,所述隔离结构沿第二方向延伸,所述第二方向与所述第一方向呈夹角设置;

6、去除部分所述衬底和部分所述隔离结构,以在所述基底上形成沿所述第一方向延伸并沿第二方向间隔排布的多条第一沟槽,所述第一沟槽的槽底面高于所述隔离结构的底面,所述第一沟槽和所述隔离结构将所述衬底分隔为多个有源柱;

7、自所述第一沟槽的槽底向下去除部分所述衬底,以形成多个由所述隔离结构隔开的凹槽,所述凹槽沿所述第一方向延伸至所述有源柱的下方;

8、在所述凹槽内形成掺杂结构,且相邻所述凹槽内的掺杂结构连接以形成位线。

9、根据本公开的一些实施例,所述在各所述凹槽内形成掺杂结构,包括:

10、在所述凹槽的槽壁上生长掺杂离子的外延层,所述外延层构成所述掺杂结构。

11、根据本公开的一些实施例,所述外延层中掺杂的离子包括磷、锑或砷;和/或,

12、所述离子的掺杂浓度大于1020每平方厘米。

13、根据本公开的一些实施例,所述凹槽的底壁高于所述隔离结构的底面。

14、根据本公开的一些实施例,所述自所述第一沟槽的槽底向下去除部分所述衬底,包括:

15、采用四甲基氢氧化铵或氨过氧化氢混合溶液对所述衬底进行湿法刻蚀,得到所述凹槽。

16、根据本公开的一些实施例,在自所述第一沟槽的槽底向下去除部分所述衬底之前,所述半导体器件的制作方法还包括:

17、在所述第一沟槽的侧壁上形成侧墙保护层。

18、根据本公开的一些实施例,所述在所述第一沟槽的侧壁上形成侧墙保护层,包括:

19、形成初始保护层,所述初始保护层覆盖所述衬底的顶面、所述隔离结构的顶面、所述第一沟槽的侧壁及底壁;

20、去除位于所述第一沟槽底壁上的所述初始保护层,保留的所述初始保护层构成所述侧墙保护层。

21、根据本公开的一些实施例,所述基底的形成方法包括:

22、提供衬底;

23、在所述衬底上形成沿所述第二方向延伸并沿所述第一方向间隔排布的多条第二沟槽;

24、在所述第二沟槽内形成所述隔离结构。

25、根据本公开的一些实施例,所述在所述第二沟槽内形成所述隔离结构,包括:

26、在所述衬底上形成隔离层,所述隔离层覆盖所述衬底的顶面并填充所述第二沟槽;

27、去除位于所述衬底顶面上的隔离层,保留的所述隔离层构成所述隔离结构。

28、根据本公开的一些实施例,所述去除位于所述衬底顶面上的隔离层,包括:

29、平坦化所述隔离层并暴露出所述衬底的顶面。

30、本公开实施例的第二方面,提供一种半导体器件,所述半导体器件包括:

31、基底,所述基底包括衬底以及设置于所述衬底内并沿第一方向间隔排布的多个隔离结构,所述隔离结构沿第二方向延伸,所述第二方向与所述第一方向呈夹角设置;

32、多条第一沟槽,设置于所述基底上,所述第一沟槽沿所述第一方向延伸,所述多条第一沟槽沿第二方向间隔排布,所述第一沟槽的槽底面高于所述隔离结构的底面,所述第一沟槽和所述隔离结构将所述衬底分隔为多个有源柱;

33、多条位线,所述位线包括沿所述第二方向排布并依次相连的多个掺杂结构,所述掺杂结构位于所述第一沟槽的下方并沿所述第二方向延伸至相邻的所述有源柱下方。

34、根据本公开的一些实施例,所述掺杂结构包括掺杂离子的外延层。

35、本剧本公开的一些实施例,所述外延层中的掺杂离子包括磷、锑或砷;和/或,

36、所述离子的掺杂浓度大于1020每平方厘米。

37、根据本公开的一些实施例,所述掺杂结构的底面高于所述隔离结构的底面。

38、根据本公开的一些实施例,所述第一沟槽的侧壁上覆盖有侧墙保护层。

39、本公开实施例的第三方面,提供一种电子设备,该电子设备包括上述的半导体器件。

40、本公开实施例所提供的半导体器件的制备方法及半导体器件中,通过基底上的隔离结构与形成在基底上的第一沟槽将衬底分隔成多个有源柱,由于第一沟槽的槽底面高于隔离结构的底面,从而使得后续去除部分衬底得到的凹槽能够经隔离结构隔开,进而使得后续形成于凹槽内的掺杂结构也经隔离结构隔开,又由于相邻第一沟槽之间位置对应的凹槽相互连通,从而使得各相互连通凹槽内的掺杂结构依次相连形成位线,如此形成的位线为具有低电阻率的掺杂结构,降低位线的电阻率,同时提高了迁移率,降低位线与有源柱之间的接触电阻,从而提高了半导体器件的性能。

41、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种半导体器件的制作方法,其特征在于,所述半导体器件的制作方法包括:

2.根据权利要求1所述的半导体器件的制作方法,其特征在于,所述在各所述凹槽内形成掺杂结构,包括:

3.根据权利要求2所述的半导体器件的制作方法,其特征在于,所述外延层中掺杂的离子包括磷、锑或砷;和/或,

4.根据权利要求1至3任一项所述的半导体器件的制作方法,其特征在于,所述凹槽的底壁高于所述隔离结构的底面。

5.根据权利要求1至3任一项所述的半导体器件的制作方法,其特征在于,所述自所述第一沟槽的槽底向下去除部分所述衬底,包括:

6.根据权利要求1至3任一项所述的半导体器件的制作方法,其特征在于,在自所述第一沟槽的槽底向下去除部分所述衬底之前,所述半导体器件的制作方法还包括:

7.根据权利要求6所述的半导体器件的制作方法,其特征在于,所述在所述第一沟槽的侧壁上形成侧墙保护层,包括:

8.根据权利要求1至3任一项所述的半导体器件的制作方法,其特征在于,所述基底的形成方法包括:

9.根据权利要求8所述的半导体器件的制作方法,其特征在于,所述在所述第二沟槽内形成所述隔离结构,包括:

10.根据权利要求9所述的半导体器件的制作方法,其特征在于,所述去除位于所述衬底顶面上的隔离层,包括:

11.一种半导体器件,其特征在于,所述半导体器件包括:

12.根据权利要求11所述的半导体器件,其特征在于,所述掺杂结构包括掺杂离子的外延层。

13.根据权利要求12所述的半导体器件,其特征在于,所述外延层中的掺杂离子包括磷、锑或砷;和/或,

14.根据权利要求11所述的半导体器件,其特征在于,所述掺杂结构的底面高于所述隔离结构的底面。

15.根据权利要求11所述的半导体器件,其特征在于,所述第一沟槽的侧壁上覆盖有侧墙保护层。

16.一种电子设备,其特征在于,包括根据权利要求11至15中任一项所述的半导体器件。

技术总结

本公开提供一种半导体器件的制作方法、半导体器件及电子设备,涉及半导体技术领域,半导体器件的制作方法包括:提供基底,去除部分衬底和部分隔离结构,自第一沟槽的槽底向下去除部分衬底,在各凹槽内形成掺杂结构,且相邻凹槽内的掺杂结构连接以形成字线。在本公开中,通过掺杂结构形成位线,能够有效降低位线的电阻率,同时提高迁移率,降低位线与有源柱之间的接触电阻,从而提高半导体器件的性能。

技术研发人员:李永杰,孟敬恒,平延磊

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!