半导体结构的形成方法与流程

本公开涉及半导体,涉及但不限于一种半导体结构的形成方法。

背景技术:

1、三维动态随机存储器(three dimensions dynamic random access memory,3ddram)能够在垂直方向上延伸,是未来dram技术发展的方向。相关技术中,3d dram的栅极结构可以选择全环栅(gate all around,gaa)结构或者是双栅(dual gate)结构;位于同一层的晶体管中相邻两个晶体管的栅极结构之间通过电子阻挡层(barrier layer)进行隔离,例如,通过空气或介质进行隔离,且位于同一层的晶体管中相邻两个晶体管的栅极结构需要相同的栅极金属层(即字线)引出。然而,相关技术中的3d dram,连接同一层晶体管中相邻两个晶体管的栅极结构的栅极金属层与位于同一层的每个晶体管的栅极结构不能同时形成,制备工艺复杂。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构的形成方法。

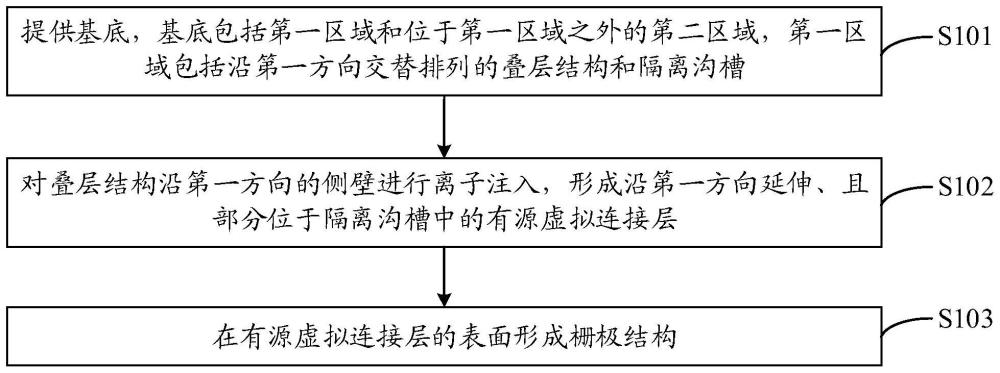

2、本公开实施例提供一种半导体结构的形成方法,所述方法包括:

3、提供基底,所述基底包括第一区域和位于所述第一区域之外的第二区域,所述第一区域包括沿第一方向交替排列的叠层结构和隔离沟槽;所述第一方向为所述基底所在平面内任意的一个方向;

4、对所述叠层结构沿所述第一方向的侧壁进行离子注入,形成沿所述第一方向延伸、且部分位于所述隔离沟槽中的有源虚拟连接层;

5、在所述有源虚拟连接层的表面形成栅极结构。

6、在一些实施例中,所述叠层结构包括沿第三方向交替堆叠的第一半导体层和第二半导体层;所述有源虚拟连接层包括沿所述第一方向交替排列的有源层和虚拟连接层;所述有源层和所述虚拟连接层通过以下步骤形成:

7、对所述叠层结构中的所述第二半导体层沿所述第一方向的两端进行预设深度的所述离子注入,形成所述虚拟连接层,未进行所述离子注入的所述第二半导体层构成所述有源层;

8、其中,所述预设深度小于所述叠层结构中的所述第二半导体层的初始尺寸;所述第三方向与所述基底所在的平面相交。

9、在一些实施例中,对所述叠层结构中的所述第二半导体层沿所述第一方向的两端进行预设深度的所述离子注入之后,所述方法还包括:

10、对所述离子注入后的所述第二半导体层进行退火处理。

11、在一些实施例中,所述第二半导体层包括沿所述第一方向上的第一表面和第二表面;所述虚拟连接层通过以下步骤形成:

12、沿所述第一表面对所述第二半导体层进行所述离子注入和所述退火处理,形成沿所述第一方向延伸的第一虚拟连接层;

13、沿所述第二表面对所述第二半导体层进行所述离子注入和所述退火处理,形成沿所述第一方向延伸的第二虚拟连接层;

14、位于同一所述隔离沟槽中的所述第一虚拟连接层和所述第二虚拟连接层构成所述虚拟连接层。

15、在一些实施例中,所述隔离沟槽沿所述第一方向具有第一尺寸;

16、所述虚拟连接层沿所述第一方向具有第二尺寸;

17、所述第一尺寸小于或者等于预设倍数的所述第二尺寸。

18、在一些实施例中,所述预设倍数为0.54。

19、在一些实施例中,在形成所述有源虚拟连接层之后,且在形成所述栅极结构之前,所述方法还包括:

20、对所述有源虚拟连接层进行减薄处理。

21、在一些实施例中,所述基底还包括牺牲结构和支撑结构,所述牺牲结构和所述支撑结构通过以下步骤形成:

22、在半导体衬底上形成初始叠层结构,其中,所述初始叠层结构包括沿所述第三方向交替堆叠的所述第一半导体层和所述第二半导体层;

23、去除部分所述初始叠层结构,形成沿第二方向排列、且沿所述第一方向和所述第三方向延伸的两个刻蚀凹槽;所述第二方向与所述第一方向位于同一平面内;

24、在所述刻蚀凹槽中形成支撑结构和位于所述支撑结构沿所述第二方向两侧的牺牲结构;其中,位于所述支撑结构之间的区域构成所述第一区域。

25、在一些实施例中,所述牺牲结构包括位于所述第一区域的第一牺牲层和位于所述第二区域的第二牺牲层。

26、在一些实施例中,所述牺牲结构与所述第二半导体层之间的刻蚀选择比大于所述支撑结构与所述第二半导体层之间的刻蚀选择比。

27、在一些实施例中,在形成所述牺牲结构和所述支撑结构之后,形成所述叠层结构和所述隔离沟槽;

28、所述叠层结构和所述隔离沟槽通过以下步骤形成:

29、在所述初始叠层结构的表面形成具有预设图案的掩膜层,所述预设图案包括沿所述第一方向排列的多个子图案;所述子图案暴露出位于所述第一区域的部分所述初始叠层结构;

30、通过所述掩膜层,去除所述子图案暴露出的部分所述初始叠层结构,形成沿所述第一方向交替排列的所述叠层结构和所述隔离沟槽。

31、在一些实施例中,在形成所述有源虚拟连接层之后,所述方法还包括:

32、去除所述第一区域中位于所述第一半导体层沿所述第二方向投影区域内的所述第二牺牲层,形成多个第一开口。

33、在一些实施例中,去除所述第二牺牲层之后,所述方法还包括:

34、去除所述第一半导体层。

35、在一些实施例中,所述栅极结构通过以下步骤形成:

36、在所述有源虚拟连接层沿所述第三方向上的第三表面和第四表面依次形成栅极介质层和位于所述栅极介质层表面的栅极导电层。

37、在一些实施例中,形成所述栅极结构之后,所述方法还包括:

38、在所述栅极导电层之间的空隙形成第二隔离结构。

39、在一些实施例中,所述第一半导体层包括锗化硅层;所述第二半导体层包括硅层。

40、本公开实施例中,在形成半导体结构的过程中,形成了连接第一方向上两个有源层的虚拟连接层,虚拟连接层可以方便后续形成连接同一层栅极结构的栅极金属层,简化了栅极结构的工艺过程,降低了半导体结构的制备成本;另外,虚拟连接层还可以作为电子阻挡层,来隔离位于同一层中相邻的栅极结构,减少漏电流的产生,从而提高所制备的半导体结构的良率。

技术特征:

1.一种半导体结构的形成方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述叠层结构包括沿第三方向交替堆叠的第一半导体层和第二半导体层;所述有源虚拟连接层包括沿所述第一方向交替排列的有源层和虚拟连接层;所述有源层和所述虚拟连接层通过以下步骤形成:

3.根据权利要求2所述的方法,其特征在于,对所述叠层结构中的所述第二半导体层沿所述第一方向的两端进行预设深度的所述离子注入之后,所述方法还包括:

4.根据权利要求3所述的方法,其特征在于,所述第二半导体层包括沿所述第一方向上的第一表面和第二表面;所述虚拟连接层通过以下步骤形成:

5.根据权利要求4所述的方法,其特征在于,所述隔离沟槽沿所述第一方向具有第一尺寸;

6.根据权利要求5所述的方法,其特征在于,所述预设倍数为0.54。

7.根据权利要求2至6任一项所述的方法,其特征在于,在形成所述有源虚拟连接层之后,且在形成所述栅极结构之前,所述方法还包括:

8.根据权利要求7所述的方法,其特征在于,所述基底还包括牺牲结构和支撑结构,所述牺牲结构和所述支撑结构通过以下步骤形成:

9.根据权利要求8所述的方法,其特征在于,所述牺牲结构包括位于所述第一区域的第一牺牲层和位于所述第二区域的第二牺牲层。

10.根据权利要求9所述的方法,其特征在于,所述牺牲结构与所述第二半导体层之间的刻蚀选择比大于所述支撑结构与所述第二半导体层之间的刻蚀选择比。

11.根据权利要求10所述的方法,其特征在于,在形成所述牺牲结构和所述支撑结构之后,形成所述叠层结构和所述隔离沟槽;

12.根据权利要求9所述的方法,其特征在于,在形成所述有源虚拟连接层之后,所述方法还包括:

13.根据权利要求12所述的方法,其特征在于,去除所述第二牺牲层之后,所述方法还包括:

14.根据权利要求13所述的方法,其特征在于,所述栅极结构通过以下步骤形成:

15.根据权利要求14所述的方法,其特征在于,形成所述栅极结构之后,所述方法还包括:

16.根据权利要求8至15任一项所述的方法,其特征在于,所述第一半导体层包括锗化硅层;所述第二半导体层包括硅层。

技术总结

本公开实施例提供一种半导体结构的形成方法,所述方法包括:提供基底,所述基底包括第一区域和位于所述第一区域之外的第二区域,所述第一区域包括沿第一方向交替排列的叠层结构和隔离沟槽;所述第一方向为所述基底所在平面内任意的一个方向;对所述叠层结构沿所述第一方向的侧壁进行离子注入,形成沿所述第一方向延伸、且部分位于所述隔离沟槽中的有源虚拟连接层;在所述有源虚拟连接层的表面形成栅极结构。

技术研发人员:林超

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!