一种宽阈值的MMIC正电压控制单刀双掷开关的制作方法

一种宽阈值的mmic正电压控制单刀双掷开关

技术领域

1.本发明涉及单刀双掷开关,特别是涉及一种宽阈值的mmic正电压控制单刀双掷开关。

背景技术:

2.开关是雷达、通信、测量等领域的重要控制元件,在系统中,开关是起收发切换、选择和隔离等一系列作用,是整机系统的重要组成元件;在工程应用中受到广泛关注,目前已有的一些mmic开关多使用负电压控制,或者同时需要正电压和负电压控制。在具体的工程应用中,通常正电压是很容易实现的,而负电压一般需要特殊提供,使得供电装置的复杂度升高,不利于提高开关的应用范围。

技术实现要素:

3.本发明的目的在于克服现有技术的不足,提供一种宽阈值的mmic正电压控制单刀双掷开关,仅使用正电压即可控制整个开关的切换,并且能够提高控制电压的阈值范围。

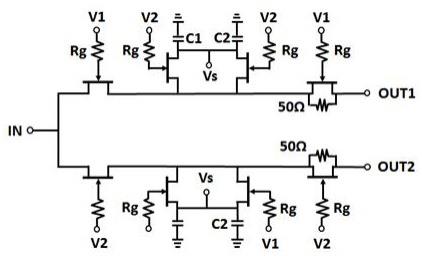

4.本发明的目的是通过以下技术方案来实现的:一种宽阈值的mmic正电压控制单刀双掷开关,包括开关电路和控制逻辑转换电路;所述开关电路包括所述端口in和两路相同的输出电路;每一路输出电路均包括输出端口第一晶体管~第四晶体管;在每一路输出电路中,所述第一晶体管的源极与输入端口连接,第一晶体管的漏极与第四晶体管的源极连接,第四晶体管的漏极连接到输出该路输出电路的输出端口,所述第一晶体管的栅极通过第一栅极电阻接入控制电平v1;所述第四晶体的栅极通过第四栅极电阻接入控制电平v1,所述第四晶体管的源极和漏极之间还连接有电阻r

sd

;所述第二晶体管的漏极与第一晶体管的漏极连接,第二晶体管的源极通过隔直电容c1接地,第二晶体管的栅极通过第二栅极电阻接入控制电平v2,所述第三晶体管的漏极与第四晶体管的源极连接,第三晶体管的源极通过隔直电容c2接地,第三晶体管的栅极通过第三栅极电阻连接控制电平v2;所述第二晶体管的源极和第三晶体管的源极相连,且连接的公共端接入工作电压vs;所述控制逻辑转换电路用于在控制电压vc的控制下对vdd电源提供的电压进行转换,得到控制电平v1、控制电平v2提供给开关电路,以实现对开关电路的控制,并将(+5v) vdd电源输出的电压作为工作电压vs,直接向所述开关电路提供工作电压。

5.优选地,所述第一晶体管~第四晶体管均为赝调制掺杂异质结场效应晶体管phemt。所述第一栅极电阻~第四栅极电阻采用阻值相同的电阻rg。所述电阻r

sd

采用50ω的电阻。

6.其中,所述控制逻辑转换电路包括lef管、第一ldf管和第二ldf管,所述第一ldf管的漏极和栅极之间连接有第一电阻r1,所述第二ldf管的漏极和栅极之间连接有第二电阻r2,所述lef管的栅极通过第三电阻r3连接控制电压vc的输入端,所述第三电阻r3和控制电压vc输入端之间连接有控制电平v2的输出端口,用于向开关电路提供控制电平v2;所述lef

管的源极与第一ldf管的栅极连接,且lef管的源极与第一ldf管的栅极之间连接有控制电平v1的输出端口,用于向开关电路提供控制电平v1;所述lef管的漏极与第二ldf管的栅极连接;所述第二ldf管的源极接地;所述第一ldf管的源极连接到vdd电源,且第一ldf管的源极还连接有工作电压vs的输出端口,用于向所述开关电路提供工作电压。

7.其中,所述控制逻辑转换电路还包括第四电阻r4,所述第四电阻r4的一端连接在第三电阻r3和lef管的栅极之间,第四电阻r4的另一端接地。所述控制逻辑转换电路还包括第五电阻r5,所述第五电阻r5的一端与vdd电源连接,第一电阻r5的与第一ldf管的源极连接。

8.本发明的有益效果是:本发明仅使用正电压即可控制整个开关的切换,应用范围广,并且通过第四电阻r4和第五电阻r5能够提高控制电压的阈值范围,实现宽阈值的mmic正电压控制单刀双掷开关控制。

附图说明

9.图1为本发明的原理示意图;图2为控制电平逻辑转换电路示意图;图3为控制电平转换曲线示意图;图4为加入电阻r4和电阻r5后的控制电平逻辑转换电路示意图;图5为并联电阻r4后的控制电平转换曲线示意图;图6为串联电阻r5后的控制电平转换曲线示意图;图7为实施例中in端驻波曲线示意图;图8为实施例中out1端驻波曲线示意图;图9为实施例中out2端驻波曲线示意图;图10为实施例中in-out1端传输损耗曲线示意图;图11为实施例中in-out2端传输损耗曲线示意图。

具体实施方式

10.下面结合附图进一步详细描述本发明的技术方案,但本发明的保护范围不局限于以下所述。

11.如图1所示,一种宽阈值的mmic正电压控制单刀双掷开关,包括开关电路和控制逻辑转换电路;所述开关电路包括所述端口in和两路相同的输出电路;每一路输出电路均包括输出端口第一晶体管~第四晶体管;在每一路输出电路中,所述第一晶体管的源极与输入端口连接,第一晶体管的漏极与第四晶体管的源极连接,第四晶体管的漏极连接到输出该路输出电路的输出端口,所述第一晶体管的栅极通过第一栅极电阻接入控制电平v1;所述第四晶体的栅极通过第四栅极电阻接入控制电平v1,所述第四晶体管的源极和漏极之间还连接有电阻rsd;所述第二晶体管的漏极与第一晶体管的漏极连接,第二晶体管的源极通过隔直电容c1接地,第二晶体管的栅极通过第二栅极电阻接入控制电平v2,所述第三晶体管的漏极与第四晶体管的源极连接,第三晶体管的源极通过隔直电容c2接地,第三晶体管的栅极通过第三栅极电阻连接控制电平v2;所述第二晶体管的源极和第三晶体管的源极相连,且连接的公共端接入工作电压vs;

所述控制逻辑转换电路用于在控制电压vc的控制下对vdd电源提供的电压进行转换,得到控制电平v1、控制电平v2提供给开关电路,以实现对开关电路的控制,并将(+5v) vdd电源输出的电压作为工作电压vs,直接向所述开关电路提供工作电压。

12.在本技术的实施例中,所述第一栅极电阻~第四栅极电阻采用阻值相同的电阻rg, rg可以采用阻值为20kω的电阻;所述电阻rsd采用50ω的电阻。所述第一晶体管~第四晶体管均为赝调制掺杂异质结场效应晶体管phemt,具体来说,是采用gaas赝配高电子迁移率晶体管。栅源电压≥0v时开启,≤-3v时关闭。在传统负电压控制开关的基础上,采用片上集成隔直电容c1和c2,在phemt源极供vs工作电压为+5v,形成正电压控制的单刀双掷开关,如图1所示,第一路输出电路的输出端为out1,另一路输出电路的输出端为out2,栅极电压v1和v2作为一高一低电平将输入端rfin切换到一路输出端out1或out2。v1=+5v、v2=0v时,v1-vs=0v、v2-vs=-5v,in输出到out1;v1=0v、v2=+5v时,v1-vs=-5v、v2-vs=0时, in输出到out2。

13.如图2所示,所述控制逻辑转换电路包括lef管、第一ldf管和第二ldf管,所述第一ldf管的漏极和栅极之间连接有第一电阻r1,所述第二ldf管的漏极和栅极之间连接有第二电阻r2,所述lef管的栅极通过第三电阻r3连接控制电压vc的输入端,所述第三电阻r3和控制电压vc输入端之间连接有控制电平v2的输出端口,用于向开关电路提供控制电平v2;所述lef管的源极与第一ldf管的栅极连接,且lef管的源极与第一ldf管的栅极之间连接有控制电平v1的输出端口,用于向开关电路提供控制电平v1;所述lef管的漏极与第二ldf管的栅极连接;所述第二ldf管的源极接地;所述第一ldf管的源极连接到vdd电源,且第一ldf管的源极还连接有工作电压vs的输出端口,用于向所述开关电路提供工作电压;其中,lef为增强型fet,ldf为耗尽型fet。

14.高低电平v1和v2是由控制电压vc提供,需经过电平逻辑转换,控制电压为vc一方面直接供给phemt栅极电压v2,另一方面供给电平逻辑转换电路。+5v电源vdd一方面直接供给phemt源极vs,另一方面供给电平逻辑转换电路。v1由电平逻辑转换电路输出,当lef栅源电压>0v时,lef开启,v1=0v;反之,v1=+5v。vc=0~+0.2v时,lef管关闭,v1=+5v,v1-vs=0v, v2-vs=-5v,输出out1; vc>0.4v时,lef管开启,v1=0v ,v1-vs=-5v,out1断开;当vc=+5v时,lef管开启,v1=0v,v1-vs=-5v,v2-vs=0v,输出out2。电平转换曲线如图3所示。此时vc阈值范围很窄,输出out1时的vc范围仅为0~+0.2v,输出out2时的vc仅为≥5v。

15.可以进一步对电平逻辑转换电路进行改进,使vc阈值范围加宽,改进后的控制电平逻辑转换电路如图4所示。

16.具体地,所述控制逻辑转换电路还包括第四电阻r4,所述第四电阻r4的一端连接在第三电阻r3和lef管的栅极之间,第四电阻r4的另一端接地。所述控制逻辑转换电路还包括第五电阻r5,所述第五电阻r5的一端与vdd电源连接,第一电阻r5的与第一ldf管的源极连接。

17.采用在vc控制端加入并联电阻r4的方式,可加宽输出out1时的vc阈值范围。并联电阻r4后,使lef逻辑管栅极电压被拉低,这样开启lef管的vc值增大,输出out1时的vc阈值范围加宽。当r4=10kω时,电平转换曲线如图5所示,vc=0~+1.2v时,lef管关闭,v1=5v,v1-vs=0v, v2-vs=-5~-3.8v,输出out1; vc>1.4v时,lef管开启,v1=0v ,v1-vs=-5v,out1断开;当vc=+5v时,lef管开启,v1=0v,v1-vs=-5v,v2-vs=0v,输出out2。

18.采用在在vdd工作电源端串联电阻r5的方式,可加宽输出out2时的vc阈值范围。串

联电阻r5后, lef开启时, phemt源极电压vs由+5v被拉低,此时开启phemt的栅极电压值降低。r5=320kω时,phemt源极电压vs由+5v被拉低到+3v,此时开启phemt的栅极电压值由+5v降低为+3v,电平转换曲线如图6所示,vc=0~+1.2v时,lef管关闭,v1=5v,v1-vs=0v, v2-vs=-5~-3.8v,输出out1;vc>1.4v时,lef管开启,v1=0v ,v1-vs=-3v,out1断开;当vc=+3v时,lef管开启,v1=0v,v1-vs=-3v,v2-vs=0v,输出out2。至此,vc阈值范围加宽,输出out1时的vc范围为0~+1.2v,输出out2时的vc为≥+3v。

19.在本技术的实施例中,利用ads软件对设计的宽控制电压阈值的正电压控制mmic单刀双掷开关进行建模、仿真,得到控制电压vc为低电平(vc=0~+1.2v)、高电平(vc=+3~+5v)两种状态下的仿真曲线,如图7~图11所示;图7(a),图8(a),图9(a),图10(a),图11(a)体现的是控制电压vc为低电平(vc=0~+1.2v)的仿真曲线,图7(b),图8(b),图9(b),图10(b),图11(b)体现的是控制电压vc为高电平(vc=+3~+5v)的仿真曲线。通过仿真结果可以看出,该mmic单刀双掷开关为正电压控制,控制电平为低电平vc=0~+1.2v时,输出out1;高电平vc=+3~+5v,输出out2,具有较宽的控制电压阈值。在200mhz~7ghz内隔离度>47.5db,损耗<1.25db,输入输出驻波优于1.3,性能良好。

20.以上所述是本发明的优选实施方式,应当理解本发明并非局限于本文所披露的形式,不应该看作是对其他实施例的排除,而可用于其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1