反熔丝存储器的制作方法

本发明涉及一种半导体组件,且特别是涉及一种反熔丝存储器(anti-fusememory)。

背景技术:

1、反熔丝存储器是一种个人计算机和电子设备所广泛采用的单次可编程只读存储器(one time programmable rom,otprom)。在反熔丝存储器的操作过程中,通过施加电压使电流流过反熔丝层来造成反熔丝层击穿(高温烧断),以形成导电路径。此外,随着存储器组件的集成度(integration)持续不断地增加,存储器组件朝向速度更快、尺寸更小的目标发展。然而,随着存储器组件的线宽持续缩小,往往导致存储单元(memory cell)产生漏电流,因而影响存储器组件的效能。

技术实现思路

1、本发明提供一种反熔丝存储器,其中位于反熔丝栅极(anti-fuse gate)下方的作为轻掺杂漏极区(lightly-doped drain,ldd)的掺杂区与隔离结构之间不存在沟道区(channel region)或其他区域。

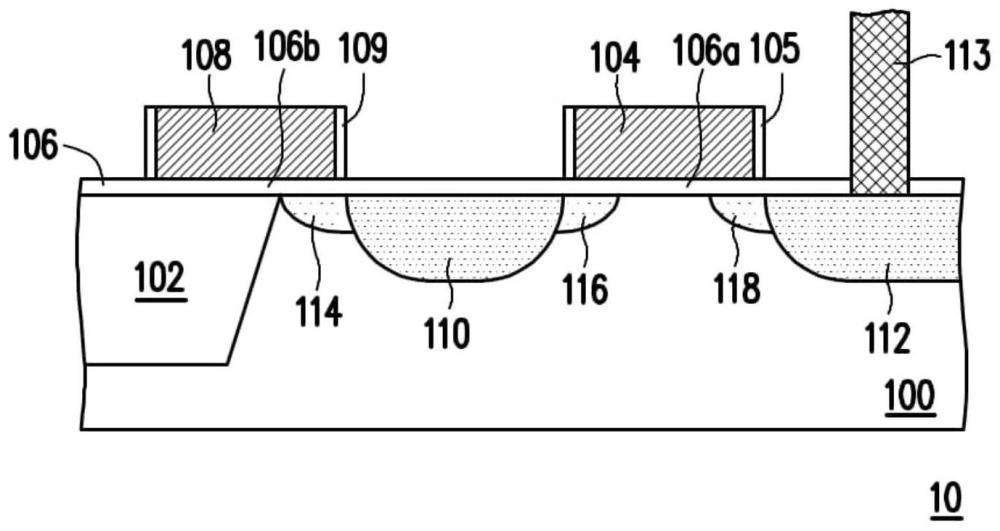

2、本发明的反熔丝存储器包括至少一个反熔丝存储单元。所述反熔丝存储单元包括隔离结构、选择栅极(select gate)、第一栅极绝缘层、反熔丝栅极、第二栅极绝缘层、第一掺杂区、第二掺杂区以及第三掺杂区。所述隔离结构设置在衬底中。所述选择栅极设置在所述衬底上。所述第一栅极绝缘层设置在所述选择栅极和所述衬底之间。所述反熔丝栅极设置在所述衬底上,且与所述隔离结构部分地重叠。所述第二栅极绝缘层设置在所述反熔丝栅极与所述衬底之间。所述第一掺杂区与所述第二掺杂区分别设置在所述选择栅极的相对两侧的所述衬底中,其中所述第一掺杂区位于所述选择栅极与所述反熔丝栅极之间。所述第三掺杂区设置在所述衬底中,且位于所述第一掺杂区与所述隔离结构之间。

3、在本发明的反熔丝存储器的一实施例中,所述第三掺杂区为轻掺杂漏极区。

4、在本发明的反熔丝存储器的一实施例中,所述第三掺杂区与所述隔离结构接触。

5、在本发明的反熔丝存储器的一实施例中,还包括第四掺杂区与第五掺杂区,其中所述第四掺杂区设置在所述衬底中、位于所述选择栅极的下方并与所述第一掺杂区连接,且所述第五掺杂区设置在所述衬底中、位于所述选择栅极的下方并与所述第二掺杂区连接。

6、在本发明的反熔丝存储器的一实施例中,所述第三掺杂区与所述反熔丝栅极的重叠宽度大于所述第四掺杂区与所述选择栅极的重叠宽度,且大于所述第五掺杂区与所述选择栅极的重叠宽度。

7、在本发明的反熔丝存储器的一实施例中,还包括接点(contact),其设置在所述第二掺杂区上。

8、在本发明的反熔丝存储器的一实施例中,所述反熔丝存储器包括两个所述反熔丝存储单元以及位线,其中:所述两个反熔丝存储单元共用一个所述第二掺杂区与所述接点;所述两个反熔丝存储单元相对于所述接点以镜像方式设置;且所述位线设置在所述两个反熔丝存储单元上且与所述接点连接。

9、在本发明的反熔丝存储器的一实施例中,所述反熔丝存储器包括第一对的所述反熔丝存储单元、第二对的所述反熔丝存储单元以及位线,其中:在所述第一对与所述第二对的每一个中,两个反熔丝存储单元共用一个所述第二掺杂区与所述接点,且所述两个反熔丝存储单元相对于所述接点以镜像方式设置;所述位线设置在所述第一对与所述第二对上,且与对应于所述第一对的所述接点以及对应于所述第二对的所述接点连接;且在所述位线的延伸方向上,所述第一对中的一个反熔丝栅极邻近所述第二对中的一个反熔丝栅极。

10、在本发明的反熔丝存储器的一实施例中,所述反熔丝存储器包括第一对的所述反熔丝存储单元、第二对的所述反熔丝存储单元、第一位线以及第二位线,其中:在所述第一对与所述第二对的每一个中,两个反熔丝存储单元共用一个所述第二掺杂区与所述接点,且所述两个反熔丝存储单元相对于所述接点以镜像方式设置;所述第一对与所述第二对共用一个所述反熔丝栅极;所述第一位线与所述第二位线设置在所述第一对与所述第二对上;所述第一位线与对应于所述第一对的所述接点连接;且所述第二位线与对应于所述第二对的所述接点连接。

11、在本发明的反熔丝存储器的一实施例中,所述第一位线与所述第二位线位于不同高度处。

12、在本发明的反熔丝存储器的一实施例中,所述第一位线与所述第二位线位于相同高度处。

13、在本发明的反熔丝存储器的一实施例中,所述第三掺杂区与所述反熔丝栅极部分地重叠。

14、在本发明的反熔丝存储器的一实施例中,在对包括所述反熔丝栅极的反熔丝晶体管进行编程操作时,位于所述反熔丝栅极与所述第三掺杂区之间的所述第二栅极绝缘层击穿而形成击穿区域,使得电流自所述反熔丝栅极通过所述击穿区域而流至所述第三掺杂区。

15、在本发明的反熔丝存储器的一实施例中,所述选择栅极与所述反熔丝栅极具有相同的宽度。

16、在本发明的反熔丝存储器的一实施例中,所述反熔丝栅极的宽度大于所述选择栅极的宽度。

17、在本发明的反熔丝存储器的一实施例中,所述第四掺杂区与所述第五掺杂区作为轻掺杂漏极区。

18、在本发明的反熔丝存储器的一实施例中,所述选择栅极包括多晶硅栅极。

19、在本发明的反熔丝存储器的一实施例中,所述反熔丝栅极包括多晶硅栅极。

20、在本发明的反熔丝存储器的一实施例中,所述第二栅极绝缘层包括氧化硅层、hfo2层或al2o3层。

21、在本发明的反熔丝存储器的一实施例中,所述第一栅极绝缘层不同于所述第二栅极绝缘层。

22、综上所述,在本发明的反熔丝存储器中,第三掺杂区与隔离结构之间不存在沟道区或其他区域。因此,在对反熔丝存储器进行编程操作的过程中,通过使反熔丝栅极下方的第二栅极绝缘层击穿(高温烧断)而形成导电路径,可避免漏电流产生。此外,由于第三掺杂区与隔离结构之间不存在沟道区或其他区域,因此可避免在编程操作的过程中寄生二极管(diode)形成于沟道区处而导致临界电压(vt)提高,且也可避免环状注入区(halo implantregion)或口袋注入区(pocket implant region)所造成的临界电压提高。

23、为让本发明能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:

1.一种反熔丝存储器,包括:

2.根据权利要求1所述的反熔丝存储器,其特征在于,所述第三掺杂区为轻掺杂漏极区。

3.根据权利要求1所述的反熔丝存储器,其特征在于,所述第三掺杂区与所述隔离结构接触。

4.根据权利要求1所述的反熔丝存储器,其特征在于,还包括第四掺杂区与第五掺杂区,其中所述第四掺杂区设置在所述衬底中、位于所述选择栅极的下方并与所述第一掺杂区连接,且所述第五掺杂区设置在所述衬底中、位于所述选择栅极的下方并与所述第二掺杂区连接。

5.根据权利要求4所述的反熔丝存储器,其特征在于,所述第三掺杂区与所述反熔丝栅极的重叠宽度大于所述第四掺杂区与所述选择栅极的重叠宽度,且大于所述第五掺杂区与所述选择栅极的重叠宽度。

6.根据权利要求1所述的反熔丝存储器,其特征在于,还包括接点,设置在所述第二掺杂区上。

7.根据权利要求6所述的反熔丝存储器,其特征在于,包括两个所述反熔丝存储单元以及位线,其中:

8.根据权利要求6所述的反熔丝存储器,其特征在于,包括第一对的所述反熔丝存储单元、第二对的所述反熔丝存储单元以及位线,其中:

9.根据权利要求6所述的反熔丝存储器,其特征在于,包括第一对的所述反熔丝存储单元、第二对的所述反熔丝存储单元、第一位线以及第二位线,其中:

10.根据权利要求9所述的反熔丝存储器,其特征在于,所述第一位线与所述第二位线位于不同高度处。

11.根据权利要求9所述的反熔丝存储器,其特征在于,所述第一位线与所述第二位线位于相同高度处。

12.根据权利要求1所述的反熔丝存储器,其特征在于,所述第三掺杂区与所述反熔丝栅极部分地重叠。

13.根据权利要求1所述的反熔丝存储器,其特征在于,在对包括所述反熔丝栅极的反熔丝晶体管进行编程操作时,位于所述反熔丝栅极与所述第三掺杂区之间的所述第二栅极绝缘层击穿而形成击穿区域,使得电流自所述反熔丝栅极通过所述击穿区域而流至所述第三掺杂区。

14.根据权利要求1所述的反熔丝存储器,其特征在于,所述选择栅极与所述反熔丝栅极具有相同的宽度。

15.根据权利要求1所述的反熔丝存储器,其特征在于,所述反熔丝栅极的宽度大于所述选择栅极的宽度。

16.根据权利要求1所述的反熔丝存储器,其特征在于,所述第四掺杂区与所述第五掺杂区作为轻掺杂漏极区。

17.根据权利要求1所述的反熔丝存储器,其特征在于,所述选择栅极包括多晶硅栅极。

18.根据权利要求1所述的反熔丝存储器,其特征在于,所述反熔丝栅极包括多晶硅栅极。

19.根据权利要求1所述的反熔丝存储器,其特征在于,所述第二栅极绝缘层包括氧化硅层、hfo2层或al2o3层。

20.根据权利要求1所述的反熔丝存储器,其特征在于,所述第一栅极绝缘层不同于所述第二栅极绝缘层。

技术总结

本发明提供一种反熔丝存储器,其包括至少一个反熔丝存储单元。反熔丝存储单元包括隔离结构、选择栅极、第一栅极绝缘层、反熔丝栅极、第二栅极绝缘层、第一掺杂区、第二掺杂区以及第三掺杂区。隔离结构设置在衬底中。选择栅极设置在衬底上。第一栅极绝缘层设置在选择栅极和衬底之间。反熔丝栅极设置在衬底上,且与隔离结构部分地重叠。第二栅极绝缘层设置在反熔丝栅极与衬底之间。第一掺杂区与第二掺杂区分别设置在选择栅极的相对两侧的衬底中,其中第一掺杂区位于选择栅极与反熔丝栅极之间。第三掺杂区设置在衬底中,且位于第一掺杂区与隔离结构之间。

技术研发人员:郑仲皓,许齐修,连启发,林英廷,赖成孝,莫亚楠

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!