相位同步装置和方法、射频电源、半导体工艺设备与流程

1.本发明涉及半导体制造领域,具体地,涉及一种相位同步装置和方法、射频电源、半导体工艺设备。

背景技术:

2.等离子体腔室中的上电极和下电极通过连接头、射频线缆等器件分别与两个射频电源电连接,这两个射频电源根据工艺要求,需要在相同的频率和相位下工作,但是,不同射频电源所连接的线缆长度、连接头等器件往往存在差异,这会导致加载至上、下电极的功率信号的相位有偏差,为此,通常使用相位同步装置实现多个电源的相位同步,具体地,如图1所示,多个电源中有一个主电源(master),其余电源为从电源(slave),其中,主电源向其中一个从电源发送同步信号,接收到该同步信号的从电源通过对应的相位同步装置进行相位调节,以实现与主电源的相位同步,同时该从电源向另一从电源发送同步信号,以使下一个从电源对应的相位同步装置进行相位调节,从而可以实现多个电源的相位同步。

3.图2为现有的相位同步装置的原理框图。如图2所示,相位同步装置集成于射频电源(被设定为从电源)中,且包括鉴相器、滤波器、比例积分(pi)控制器和压控振荡器(vcxo),其中,鉴相器用于接收主电源发送的同步信号,并根据该同步信号获得主电源与从电源的相位差,并通过滤波器得到与该相位差对应的模拟电压信号v

ref

(该信号与相位差为线性关系);比例积分(pi)控制器用于根据该模拟电压信号v

ref

和预设的电压设定值v

set

计算获得相位调整量,并根据该相位调整量控制压控振荡器进行移相,移相后输出的电压信号反馈至鉴相器。经过多次闭环控制,使模拟电压信号v

ref

逐渐接近电压设定值v

set

,从而实现主电源与从电源的相位同步。

4.但是,由于上述相位同步装置处理的是模拟信号,这在实际应用中不可避免地存在以下问题:

5.其一,由于是模拟信号,鉴相器因无法鉴别超过180

°

的相位差,例如对于90

°

和270

°

的相位差,该鉴相器均认为相位差为90

°

,导致相位器的相位检测范围只有0-180

°

,而且压控振荡器也只能在0-180

°

的范围内移相,可调范围较小;

6.其二,模拟信号的波形具有尖峰或纹波,导致鉴相器输出的相位差精度受到影响。

技术实现要素:

7.本发明旨在至少解决现有技术中存在的技术问题之一,提出了一种相位同步装置和方法、射频电源、半导体工艺设备,其可以实现0-360

°

相位可调,同时可以消除模拟信号的尖峰或波纹产生的影响,从而可以提高相位检测精度。

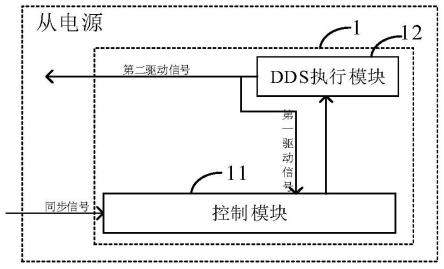

8.为实现本发明的目的而提供一种相位同步装置,用于实现主电源和从电源的相位同步,包括控制模块和dds执行模块,其中:

9.所述控制模块用于在所述相位同步装置位于所述从电源时,将所述主电源发送的同步信号转换为数字信号,并根据转换后的数字信号的频率,控制所述dds执行模块的频

率,以使所述dds执行模块输出的第一驱动信号的频率与所述同步信号的频率一致;

10.所述dds执行模块用于向所述控制模块反馈所述第一驱动信号;所述控制模块还用于根据所述第一驱动信号的数字信号和所述同步信号的数字信号,获得相位控制信息,并向所述dds执行模块发送所述相位控制信息;所述dds执行模块还用于根据所述相位控制信息进行移相,以使所述dds执行模块输出的第二驱动信号的相位与所述同步信号的相位一致。

11.可选的,所述控制模块包括i/o接口单元、鉴相单元和控制单元,其中,

12.所述i/o接口单元的输出端与所述鉴相单元的输入端连接,所述i/o接口单元用于将所述同步信号转换为数字信号,并向所述鉴相单元发送转换后的数字信号;

13.所述鉴相单元的输出端与所述控制单元的输入端连接,所述鉴相单元用于根据所述第一驱动信号和所述同步信号,获得相位差信息,且向所述控制单元发送所述相位差信息;

14.所述控制单元的输出端与所述dds执行模块的输入端连接,所述控制单元用于根据所述相位差信息,判断所述从电源的相位是超前还是滞后于所述主电源的相位,以及计算获得所述第一驱动信号和所述同步信号的相位差,并根据所述相位差向所述dds执行模块发送所述相位控制信息。

15.可选的,所述相位差信息包括第一脉冲信号和第二脉冲信号,所述第一脉冲信号和所述第二脉冲信号根据所述第一驱动信号和所述同步信号获得;

16.所述控制单元用于比较所述第一脉冲信号与所述第二脉冲信号的脉宽,若所述第一脉冲信号的脉宽大于所述第二脉冲信号的脉宽,则表示所述主电源的相位超前于所述从电源的相位;若所述第二脉冲信号的脉宽大于所述第一脉冲信号的脉宽,则表示所述从电源的相位超前于所述主电源的相位。

17.可选的,所述控制单元还用于根据所述第一脉冲信号和所述第二脉冲信号,计算获得第一参数值,并根据所述第一参数值和预设的第二参数值,计算获得所述相位差,并根据所述相位差向所述dds执行模块发送所述相位控制信息:

18.所述第一参数值为在预设的门控时钟为高电平的时段内,所述第一脉冲信号与所述第二脉冲信号均为高电平时,所述参考时钟信号的上升沿数量;所述第二参数值为在所述门控时钟为高电平的时段内,预设的参考时钟信号的上升沿数量。

19.可选的,所述相位差满足下述关系式:

[0020][0021]

其中,φ为所述相位差;fs_cnt为所述第一参数值;up_cnt为所述第二参数值;

[0022]

所述相位控制信息包括相位控制字,所述相位控制字满足下述关系式:

[0023][0024]

其中,pow为所述相位控制字。

[0025]

可选的,所述控制模块还包括锁相环单元,所述锁相环单元的输入端与所述i/o接口单元的输出端连接,所述锁相环单元的输出端分别与所述控制单元的输入端和所述dds执行模块的输入端连接,所述锁相环单元用于根据所述主电源输出的所述同步信号的频率

范围和所述dds执行模块的参考时钟输入范围,确定所述数字信号的倍数,并计算所述数字信号的频率与所述倍数的乘积,作为第一参考频率向所述dds执行模块和所述控制单元发送;

[0026]

所述控制单元还用于根据所述第一参考频率,向所述dds执行模块发送第一频率控制信息。

[0027]

可选的,所述第一频率控制信息包括第一频率控制字;

[0028]

所述第一参考频率和所述第一频率控制字满足下述关系式:

[0029][0030]

其中,f0为所述dds执行模块输出的所述第一驱动信号的频率;ftw1为所述第一频率控制字;f

osc1

为所述第一参考频率,f

osc1

=m

×

cex_in,m为所述倍数;cex_in为所述同步信号的频率,且cex_in=f0;n为所述dds执行模块的倍频系数,n大于等于4,且小于等于20。

[0031]

可选的,所述dds执行模块包括dds和滤波器,其中,所述dds的输入端与所述控制模块的输出端连接,所述dds的输出端与所述滤波器的输入端连接,所述dds用于向所述滤波器发送所述第一驱动信号,以及根据所述相位控制信息进行移相,并向所述滤波器发送所述第二驱动信号;

[0032]

所述滤波器用于滤除所述第一驱动信号和所述第二驱动信号中的谐波。

[0033]

可选的,所述dds执行模块还包括传输线变压器,所述传输线变压器的输入端与所述滤波器的输出端连接,所述传输线变压器的输出端与所述控制模块的输入端连接,所述传输线变压器用于将经所述滤波器处理后的所述第一驱动信号和所述第二驱动信号转换为单端信号,并向所述控制模块发送所述单端信号。

[0034]

可选的,所述锁相环单元还用于在所述相位同步装置位于所述主电源时向所述dds执行模块和所述控制单元发送预设的第二参考频率;

[0035]

所述控制单元还用于根据所述第二参考频率,向所述dds执行模块发送第二频率控制信息;

[0036]

所述dds执行模块还用于根据所述第二参考频率和所述第二频率控制信息输出第三驱动信号,所述第三驱动信号驱动当前射频电源输出射频功率,其中,基于所述射频功率耦合出的射频功率信号作为所述从电源的同步信号。

[0037]

可选的,所述第二频率控制信息包括第二频率控制字;

[0038]

所述第二参考频率和所述第二频率控制字满足下述关系式:

[0039][0040]

其中,f

osc2

为所述第二参考频率;f1为在所述相位同步装置位于所述主电源时,所述dds执行模块输出的第三驱动信号的频率;ftw2为所述第二频率控制字。

[0041]

可选的,所述控制单元还用于根据所述第三驱动信号的频率的测量值,以及预设的目标值和校准系数,对所述第二频率控制字进行校准,并向所述dds执行模块发送所述第二频率控制字的校准值。

[0042]

可选的,所述第二频率控制字的校准值采用下述关系式计算获得:

[0043][0044]

其中,ftw3为所述第二频率控制字的校准值;ftw4满足下述关系式:

[0045][0046]

f4为所述目标值;f3为所述测量值;所述校准系数等于

[0047]

可选的,所述控制模块还包括通讯单元,所述通讯单元用于接收上位机发送的控制指令,并向所述控制单元发送所述控制指令;所述控制指令包括表示所述相位同步装置所在的射频电源为所述从电源或者所述主电源的指令。

[0048]

可选的,所述相位同步装置还包括信号处理模块;

[0049]

所述信号处理模块与所述控制模块相连,用于接收所述主电源发送的同步信号,对所述同步信号进行滤波得到模拟方波信号,并将所述模拟方波信号的幅值调制在预设幅值范围内,然后向所述控制模块发送调制后的模拟方波信号;

[0050]

所述控制模块用于将接收的所述模拟方波信号转换为数字信号。

[0051]

作为另一个技术方案,本发明还提供一种射频电源,包括功率输出模块和电源控制模块,所述电源控制模块用于向所述功率输出模块输出驱动信号,以驱动所述功率输出模块输出射频功率,所述电源控制模块包括用于控制所述驱动信号相位的相位同步装置,所述相位同步装置为本发明提供的上述相位同步装置。

[0052]

作为另一个技术方案,本发明还提供一种相位同步方法,采用本发明提供的上述相位同步装置对所在射频电源的相位进行控制,所述相位同步方法包括:

[0053]

在所述相位同步装置所在的射频电源为所述从电源时,接收所述主电源发送的同步信号,并将其转换为数字信号;

[0054]

根据转换后的数字信号的频率,控制所述dds执行模块的频率,以使输出的第一驱动信号的频率与所述同步信号的频率一致;

[0055]

根据所述第一驱动信号的数字信号和所述同步信号的数字信号,获得相位控制信息;

[0056]

根据所述相位控制信息控制所述dds执行模块进行移相,以使输出的第二驱动信号的相位与所述同步信号的相位一致。

[0057]

可选的,所述方法还包括:

[0058]

在所述相位同步装置所在的射频电源为所述主电源时,向所述dds执行模块发送预设的第二参考频率和第二频率控制信息;

[0059]

控制所述dds执行模块根据所述第二参考频率和所述第二频率控制信息输出第三驱动信号,所述第三驱动信号用于驱动当前射频电源输出射频功率,其中,基于所述射频功率耦合出的射频功率信号作为所述从电源的同步信号。

[0060]

作为另一个技术方案,本发明还提供一种半导体工艺设备,包括多个电极以及与所述多个电极一一对应连接的多个射频电源,所述射频电源采用本发明提供的上述射频电源。

[0061]

本发明具有以下有益效果:

digital synthesis,直接数字频率合成)执行模块12,其中,控制模块11用于在相位同步装置1位于从电源时,将主电源发送的同步信号转换为数字信号,并根据转换后的数字信号的频率,控制dds执行模块12的频率,以使dds执行模块12输出的第一驱动信号的频率与上述同步信号的频率一致,从而可以实现从电源与主电源的频率一致。dds执行模块12用于向控制模块11反馈上述第一驱动信号;控制模块11还用于根据上述第一驱动信号的数字信号和同步信号的数字信号,获得相位控制信息,并向dds执行模块12发送上述相位控制信息;dds执行模块12还用于根据上述相位控制信息进行移相,以使dds执行模块12输出的第二驱动信号的相位与同步信号的相位一致,从而可以实现从电源与主电源的相位同步。

[0083]

在相位同步装置1位于从电源时,通过将主电源发送的同步信号转换为数字信号,可以在控制模块11的控制下结合dds执行模块12进行移相,由于是数字信号,控制模块11可以根据dds执行模块12反馈的第一驱动信号的数字信号和同步信号的数字信号,鉴别超过180

°

的相位差,例如可以区分90

°

和270

°

的相位差,结合dds执行模块12根据相位控制信息进行移相,可以实现0-360

°

相位可调;同时,由于是数字信号,不存在模拟信号的尖峰或波纹产生的影响,从而可以提高相位检测精度。

[0084]

在一些可选的实施例中,如图4所示,相位同步装置1还包括信号处理模块13,该信号处理模块13与控制模块12相连,用于接收主电源发送的同步信号,对该同步信号进行滤波得到模拟方波信号,并将该模拟方波信号的幅值调制在预设幅值范围(幅值例如为3.3v)内,然后向控制模块12发送调制后的模拟方波信号;控制模块12用于将接收的模拟方波信号转换为数字信号。通过将上述同步信号转换为方波信号,可以提高控制的可靠性和精度。可选的,信号处理模块13例如包括电压比较器。

[0085]

在一些可选的实施例中,上述控制模块11例如为fpga(field-programmable gate array,现场可编程门阵列)或者其他具有较宽的信号调理范围的控制器。以fpga为例,由于fpga是cmos电平(即,“1”逻辑电平电压接近于电源电压,“0”逻辑电平接近于0v),在模拟信号的幅值高于2.31v时,fpga会判断该信号是高电平,在模拟信号的幅值低于0.99v时,fpga会判断该信号是低电平,因此,fpga具有很宽的信号调理范围,从而可以在信号存在尖峰或波纹时,不容易出现高、低电平的误判断,从而可以消除模拟信号的尖峰或波纹产生的影响,提高相位检测精度。

[0086]

在一些可选的实施例中,请参阅图5,控制模块11包括i/o接口单元113、鉴相单元111和控制单元112,其中,i/o接口单元113的输出端与鉴相单元111的输入端连接,i/o接口单元113用于将上述同步信号转换为数字信号,并向鉴相单元111发送转换后的数字信号。鉴相单元111的输出端与控制单元112的输入端连接,鉴相单元111用于根据上述第一驱动信号和同步信号,获得相位差信息,且向控制单元112发送该相位差信息;控制单元112的输出端与dds执行模块12的输入端连接,控制单元112用于根据上述相位差信息,判断从电源的相位是超前还是滞后于主电源的相位,以及计算获得上述第一驱动信号和同步信号的相位差,并根据该相位差向dds执行模块12发送上述相位控制信息。借助上述鉴相单元111获得相位差信息,可以使控制单元112判断从电源的相位是超前还是滞后于主电源的相位,从而不仅可以结合dds执行模块12实现0-360

°

相位可调,而且还可以提高相位检测精度。上述鉴相单元111例如为三态鉴相器。上述鉴相单元111可以是集成于控制单元112中的鉴相电路,或者也可以是另外配置的鉴相器芯片。

[0087]

在一些可选的实施例中,上述鉴相单元111获得的相位差信息包括第一脉冲信号和第二脉冲信号,该第一脉冲信号和第二脉冲信号根据上述第一驱动信号和同步信号获得;控制单元112用于比较第一脉冲信号与第二脉冲信号的脉宽(即,高电平持续的时间),若第一脉冲信号的脉宽大于第二脉冲信号的脉宽,则表示主电源的相位超前于从电源的相位;反之,若第二脉冲信号的脉宽大于第一脉冲信号的脉宽,则表示从电源的相位超前于主电源的相位。

[0088]

通过上述鉴相单元111结合控制单元112,来判断从电源的相位是超前还是滞后于主电源的相位的方法具体为:请一并参阅图6和图7,上述鉴相单元111例如为三态鉴相器,其主要由两个d触发器组成,二者的clk端分别接收dds执行模块12反馈的上述第一驱动信号(即,图6中的s_clk)和同步信号(即,图6中的m_clk);q端为d触发器的输出端,rst端是复位引脚,d端赋值“1”。请参阅图7,当m_clk和s_clk各自为上升沿时,q=d,即,两个d触发器的输出值为“1”,并发送至控制单元112;控制单元112将两个d触发器的该输出值分别赋值于up和dn,当up、dn同为“1”时,rst端置高,此时两个d触发器复位,将up、dn复位为“0”,up、dn在高电平和低电平之间变化形成了如图7所示的与up对应的第一脉冲信号和与dn对应的第二脉冲信号。控制单元112用于比较该第一脉冲信号与第二脉冲信号的脉宽,如图7中的图(a)所示,若up对应的第一脉冲信号的脉宽大于dn对应的第二脉冲信号的脉宽,则表示同步信号的相位超前于第一驱动信号的相位,即,主电源的相位超前于从电源的相位;如图7中的图(b)所示,若dn对应的第二脉冲信号的脉宽大于up对应的第一脉冲信号的脉宽,则表示第一驱动信号的相位超前于同步信号的相位,即,从电源的相位超前于主电源的相位。

[0089]

在一些可选的实施例中,控制单元112还用于根据上述第一脉冲信号和第二脉冲信号,计算获得第一参数值,并根据该第一参数值和预设的第二参数值,计算获得第一驱动信号和同步信号的相位差,并根据该相位差向dds执行模块12发送上述相位控制信息。上述第一参数值为在预设的门控时钟为高电平的时段内,上述第一脉冲信号与第二脉冲信号均为高电平时,参考时钟信号的上升沿数量;上述第二参数值为在门控时钟为高电平的时段内,预设的参考时钟信号的上升沿数量。具体来说,如图8所示,上述门控时钟gate_time是与up对应的第一脉冲信号和与dn对应的第二脉冲信号的周期的整数倍,该整数倍为设定值;fs为参考时钟信号,其为设定值,频率例如为400mhz。

[0090]

需要说明的是,在实际应用中,由于门控时钟gate_time不是参考时钟信号fs的整数倍,而只有在参考时钟信号fs为上升沿时,fs_cnt才会更新,这使得上述相位差会产生对参考时钟信号fs

±

1个周期的误差,为了消除该误差,以提高测量相位差的准确度,可以延长门控时钟gate_time的高电平时间,或者,也可以提高参考时钟信号fs的频率。

[0091]

进一步可选的,上述相位差满足下述关系式:

[0092][0093]

其中,φ为上述相位差;fs_cnt为上述第一参数值;up_cnt为上述第二参数值。

[0094]

在此基础上,上述相位控制信息可以包括相位控制字,该相位控制字可以满足下述关系式:

[0095]

[0096]

其中,pow为相位控制字。

[0097]

dds执行模块12例如集成有14位相位控制字,控制单元112将上述相位控制字pow写入dds执行模块12,再由dds执行模块12根据该相位控制字pow进行0~360

°

相位调节。

[0098]

在一些可选的实施例中,请参阅图9,控制模块11还包括锁相环单元114,该锁相环单元114的输入端与i/o接口单元113的输出端连接,锁相环单元114的输出端分别与控制单元112的输入端和dds执行模块12的输入端连接,用于根据主电源输出的同步信号的频率范围和dds执行模块12的参考时钟输入范围,确定数字信号的倍数,并计算该数字信号的频率与倍数的乘积,作为第一参考频率向dds执行模块12和控制单元112发送。锁相环单元114可以集成于控制模块11中的锁相环电路,或者也可以是另外配置的锁相环芯片。

[0099]

例如,若主电源输出的同步信号的频率范围为12.882mhz~14.238mhz;dds执行模块12的参考时钟输入范围为20mhz~30mhz,则上述倍数可以为2,即,锁相环单元114对上述数字信号进行二倍频,从而可以使dds执行模块12的参考时钟输入范围与主电源输出的同步信号的频率范围相适配,即,主电源输出的同步信号的频率范围应落入dds执行模块12的参考时钟输入范围内。

[0100]

需要说明的是,以射频电源的频率为13.56mhz为例,若dds执行模块12的参考时钟输入范围为20mhz~30mhz,则需要锁相环单元114对上述数字信号进行二倍频,以主电源输出的同步信号的频率范围应落入dds执行模块12的参考时钟输入范围内。但是,在实际应用中,dds执行模块12的参考时钟输入范围并不局限于上述范围,若dds执行模块12具有其他的参考时钟输入范围,且适用于13.56mhz,则无需对上述数字信号进行二倍频。在实际应用中,可以根据主电源输出的同步信号的频率范围和dds执行模块12的参考时钟输入范围,进行多倍频或分频,只要能够使dds执行模块12的参考时钟输入范围与主电源输出的同步信号的频率范围相适配即可。

[0101]

控制单元112还用于根据上述第一参考频率,向dds执行模块12发送第一频率控制信息。在一些可选的实施例中,该第一频率控制信息包括第一频率控制字,该第一参考频率和第一频率控制字满足下述关系式:

[0102][0103]

其中,f0为dds执行模块12输出的第一驱动信号的频率;ftw1为上述第一频率控制字;f

osc1

为上述第一参考频率,f

osc1

=m

×

cex_in,m为上述倍数,例如如果是二倍频,则m=2;cex_in为上述同步信号的频率,且cex_in=f0;n为dds执行模块12的倍频系数,n大于等于4,且小于等于20,例如n=24。

[0104]

在一些可选的实施例中,请参阅图10,控制模块11还包括通讯单元115,该通讯单元115用于接收上位机3发送的控制指令,并向控制单元112发送该控制指令;上述控制指令包括相位同步装置1所在的射频电源为从电源或者主电源的指令,从而可以实现对相位同步装置1所在的射频电源是从电源还是主电源的设定。当然,在实际应用中,还可以发送实现其他功能的相应指令,本发明实施例对此没有特别的限制。

[0105]

在一些可选的实施例中,请参阅图11,上述dds执行模块12包括dds121和滤波器122,其中,dds121即为直接数字频率合成器,其输入端与控制单元112的输出端连接,dds121的输出端与滤波器132的输入端连接,dds121用于向滤波器122发送上述第一驱动信

号,以及根据上述相位控制信息进行移相,并向滤波器122发送上述第二驱动信号;滤波器122用于滤除上述第一驱动信号和上述第二驱动信号中的谐波。上述dds121输出的信号为差分信号,即,互补的正弦信号(即,相位差为180

°

),该信号含有谐波,滤波器122用于滤除该谐波,以获得干净的正弦信号。

[0106]

在一些可选的实施例中,请参阅图11,上述dds执行模块12还包括传输线变压器123,该传输线变压器123的输入端与滤波器122的输出端连接,传输线变压器123的输出端与控制模块11的输入端连接,传输线变压器123用于将经滤波器122处理后的上述第一驱动信号和上述第二驱动信号转换为单端信号。例如,如图13所示,传输线变压器123可以将两路相位差为180

°

、幅值为5v的信号(即,上述差分信号)变换为一路

±

5v的驱动信号(即,单端信号),该传输线变压器123例如为1:1传输型巴伦。

[0107]

在一些可选的实施例中,请参阅图12,上述锁相环单元114还用于在相位同步装置1位于主电源时,向dds执行模块12和控制单元112发送预设的第二参考频率;控制单元112还用于根据该第二参考频率,向dds执行模块12发送第二频率控制信息;dds执行模块12还用于根据上述第二参考频率和上述第二频率控制信息输出第三驱动信号,该第三驱动信号驱动当前射频电源(即,相位同步装置1所在主电源)输出射频功率,其中,基于该射频功率耦合出的射频功率信号作为从电源的同步信号向作为从电源的其他射频电源发送。需要说明的是,上述基于该射频功率耦合出的射频功率信号的功率大小相对于当前射频电源输出的射频功率的占比非常小(例如是射频功率的万分之一),即可作为同步信号。在实际应用中,主电源和从电源之间可以通过线缆连接,主电源通过线缆将同步信号传递给从电源。

[0108]

还需要说明的是,在实际应用中,当前射频电源(即,相位同步装置1所在主电源)输出的射频功率和同步信号的频率是一致的,但是主电源和从电源各自输出的射频功率信号在经各自的功率输出模块和线缆输出到负载(例如半导体腔室)时,二者的射频功率信号的相位仍然可能会存在相位差,在这种情况下,根据工艺的具体需要,用户可以根据该相位差,通过上位机3向从电源对应的相位同步装置1中的控制单元112发送预设的相位调整量,再次对从电源的相位进行调节,以消除该相位差。

[0109]

在一些可选的实施例中,上述第二频率控制信息包括第二参考频率控制字,上述第二参考频率和上述第二频率控制字满足下述关系式:

[0110][0111]

其中,f

osc2

为上述第二参考频率,例如可以设定为20mhz;f1为在相位同步装置1位于主电源时,dds执行模块12输出的第三驱动信号的频率;ftw2为第二频率控制字。

[0112]

在相位同步装置1位于主电源时,通过锁相环单元114和控制单元112对dds执行模块12输出的第三驱动信号的频率进行控制,可以保证dds执行模块12的正常输出,实现正常工作。另外,可选的,还可以对dds执行模块12输出的第三驱动信号的频率进行校准,从而可以提高相位控制精度,具体地,控制单元112还用于根据上述第三驱动信号的频率的测量值,以及预设的目标值和校准系数,对上述第二频率控制字进行校准,并向dds执行模块12发送第二频率控制字的校准值。

[0113]

在一些可选的实施例中,上述第二频率控制字的校准值采用下述关系式计算获得:

[0114][0115]

其中,ftw3为第二频率控制字的校准值;ftw4满足下述关系式:

[0116][0117]

f4为上述目标值;f3为上述测量值;上述校准系数等于

[0118]

由此,可以实现对dds执行模块12输出的第三驱动信号的频率的闭环控制。在实际应用中,上述第三驱动信号的频率的测量值可以通过频率测量工具测量获得,该频率测量工具例如为示波器或者频率计等的可以检测上述第三驱动信号的频率的部件。

[0119]

作为另一个技术方案,请参阅图14,本发明实施例还提供一种相位同步方法,采用本发明实施例提供的上述相位同步装置对所在射频电源的相位进行控制,以采用图3所示的相位同步装置1为例,该相位同步方法包括:

[0120]

s1、在相位同步装置1所在的射频电源为从电源时,接收主电源发送的同步信号,并将其转换为数字信号;

[0121]

s2、根据转换后的数字信号的频率,控制dds执行模块12的频率,以使输出的第一驱动信号的频率与同步信号的频率一致;

[0122]

s3、根据上述第一驱动信号的数字信号和上述同步信号的数字信号,获得相位控制信息;

[0123]

s4、根据上述相位控制信息控制dds执行模块12进行移相,以使输出的第二驱动信号的相位与上述同步信号的相位一致。

[0124]

综上所述,本发明实施例提供的相位同步装置和方法的技术方案中,通过将主电源发送的同步信号转换为数字信号,可以在控制模块的控制下结合dds(direct digital synthesis,直接数字频率合成)执行模块进行移相,由于是数字信号,控制模块可以根据dds执行模块反馈的第一驱动信号的数字信号和同步信号的数字信号,鉴别超过180

°

的相位差,例如可以区分90

°

和270

°

的相位差,结合dds执行模块根据相位控制信息进行移相,可以实现0-360

°

相位可调;同时可以消除模拟信号的尖峰或波纹产生的影响,从而可以提高相位检测精度。

[0125]

作为另一个技术方案,请参阅图15,本发明实施例还提供一种射频电源100,该射频电源100包括功率输出模块101和电源控制模块102,该电源控制模块102用于向功率输出模块101输出驱动信号,以驱动功率输出模块101输出射频功率,并且电源控制模块102包括用于控制上述驱动信号相位的相位同步装置1,该相位同步装置1为本发明实施例提供的上述相位同步装置。

[0126]

本发明实施例提供的射频电源,其通过采用本发明实施例提供的上述相位同步装置,可以实现0-360

°

相位可调,同时可以消除模拟信号的尖峰或波纹产生的影响,从而可以提高相位检测精度。

[0127]

作为另一个技术方案,本发明实施例还提供一种半导体工艺设备,包括多个电极以及与多个电极一一对应连接的多个射频电源,以及本发明实施例提供的上述射频电源。在实际应用中,上述多个电极中例如有诸如射频线圈、电极板等的上电极,诸如基座等的下

电极。

[0128]

本发明实施例提供的半导体工艺设备,其通过采用本发明实施例提供的上述射频电源,可以实现0-360

°

相位可调,同时可以消除模拟信号的尖峰或波纹产生的影响,从而可以提高相位检测精度。

[0129]

可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1