半导体结构及其制造方法、存储器与流程

本公开实施例涉及但不限于半导体制造领域,具体是涉及一种半导体结构及其制造方法、存储器。

背景技术:

1、半导体技术发展史的本质就是晶体管尺寸的缩小史。从上世纪七十年代的10微米节点开始,遵循着摩尔定律一步一步走到了今天的5纳米。在这一过程中,每当摩尔定律遭遇困境,总会有新的技术及时出现并引领着摩尔定律继续前行。gaa(gate-all-around,全环绕栅极)晶体管作为finfet(fin field effect transistor,鳍式场效应晶体管)的下一代技术可进一步节省空间,与此同时,使用3d结构模式在此基础上又再次向上进行了空间拓展,对dram的发展有极大的帮助。对3d darm结构进行新的空间结构设计,是本领域的重要研究方向。

技术实现思路

1、有鉴于此,本公开实施例提供了一种半导体结构及其制造方法、存储器。

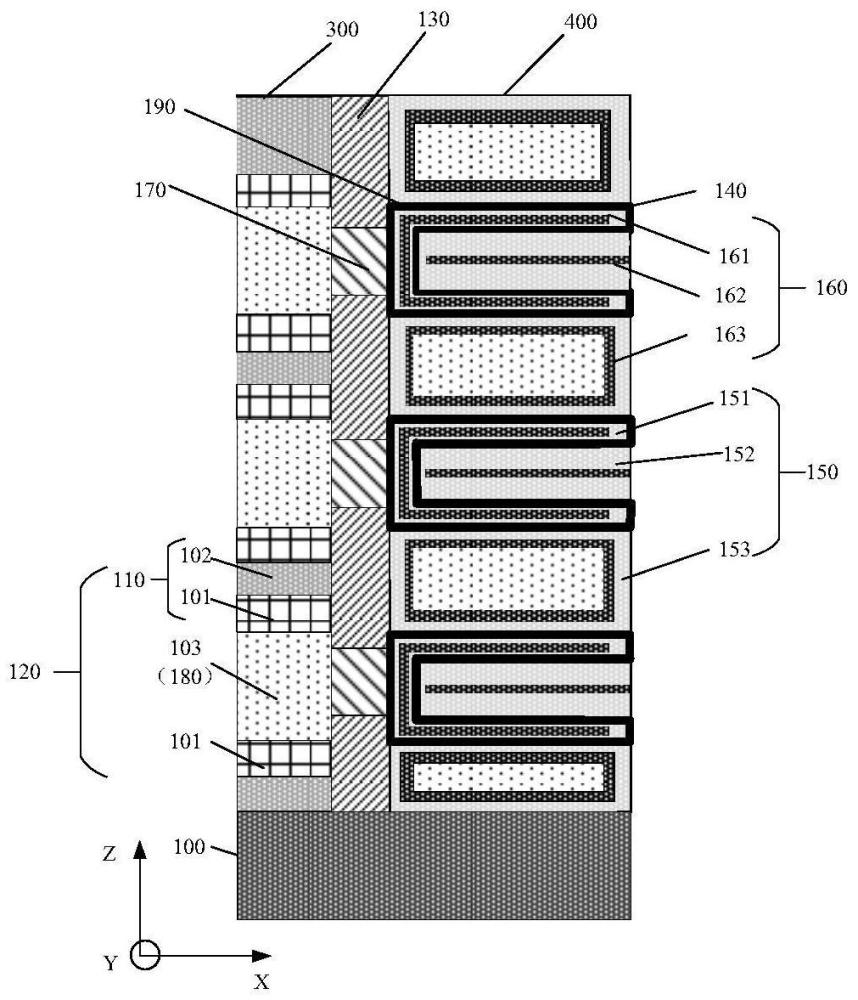

2、第一方面,本公开实施例提供了一种所述半导体结构包括:

3、衬底;

4、堆叠结构,位于所述衬底上;所述堆叠结构至少包括多个第一介质层;所述第一介质层由氧化硅层和/或氮化硅层组成;

5、第一隔离层,位于所述堆叠结构中沿平行于所述衬底表面的第一方向延伸;所述第一隔离层用于将所述堆叠结构划分为晶体管区和电容区;

6、多个层叠的晶体管,位于所述晶体管区中;

7、多个层叠的电容结构,位于所述电容区中;所述电容结构包括第一电极,第二介质层以及第二电极;

8、所述第一电极包括:多个平行于所述衬底表面的第一部分和多个垂直于所述衬底表面的第二部分,且所述第一部分和所述第二部分交替首尾相连;

9、多个电容接触结构,位于所述第一隔离层中,所述电容接触结构的两侧分别连接所述晶体管和所述电容结构的第一电极。

10、在一些实施例中,所述第二介质层覆盖所述第一电极的内壁和部分外壁;其中,所述第一电极的内壁位于所述第一电极所包围的区域内;所述第一电极的外壁位于所述第一电极所包围的区域外。

11、在一些实施例中,所述第二电极覆盖所述第二介质层的表面;其中,所述第二介质层的表面包括位于所述第一电极所包围的区域内的第一表面以及位于所述第一电极所包围的区域外的第二表面。

12、在一些实施例中,所述第二电极包括:位于所述第一电极所包围的区域内的第三部分,以及位于所述第一电极所包围的区域外的第四部分。

13、在一些实施例中,所述第一电极的厚度为2nm至7nm。

14、在一些实施例中,多个所述第一隔离层分别用于将所述堆叠结构划分为并列排布的第一晶体管区、电容区以及第二晶体管区。

15、在一些实施例中,所述电容区中包括:

16、第二隔离层,沿所述第一方向延伸,且将所述电容区划分为两个子电容区;其中,两个所述子电容区中包括对称分布的多个层叠的所述电容结构。

17、在一些实施例中,所述电容区中包括:

18、多个第四隔离层,沿平行于所述衬底的第二方向延伸;其中,所述第二方向与所述第一方向相交;所述第四隔离层用于隔离所述电容区的多个所述电容结构。

19、在一些实施例中,所述晶体管区中包括:

20、多个第三隔离层,沿平行于所述衬底的第二方向延伸;其中,所述第二方与所述第一方向相交;所述第三隔离层用于隔离所述晶体管区中的多个所述晶体管。

21、第二方面,本公开实施例还提供一种半导体结构的制造方法,所述方法包括:

22、提供衬底;

23、在所述衬底上形成堆叠结构;其中,所述堆叠结构包括交替堆叠的第一介质层和第一多晶硅层;所述第一介质层由氧化硅层和/或氮化硅层组成;

24、在所述堆叠结构中,沿平行于所述衬底表面的第一方向形成第一隔离层;所述第一隔离层用于将所述堆叠结构划分为晶体管区和电容区;其中,位于所述晶体管区的所述第一多晶硅层用于形成多个晶体管;

25、去除所述电容区的所述第一多晶硅层,形成多层用于容纳电容结构的凹陷结构;

26、在所述凹陷结构裸露出的所述第一隔离层中形成多个电容接触结构;所述电容接触结构用于连接所述电容结构和所述晶体管;

27、基于所述凹陷结构的形貌形成多层的所述电容结构;所述电容结构包括第一电极,第二介质层以及第二电极;

28、所述第一电极包括:多个平行于所述衬底表面的第一部分和多个垂直于所述衬底表面的第二部分,且所述第一部分和所述第二部分交替首尾相连。

29、在一些实施例中,所述基于所述凹陷结构的形貌形成多层的所述电容结构,包括:

30、基于所述凹陷结构的内壁的形貌形成所述第一电极;

31、形成覆盖所述第一电极的内壁和部分外壁的第二介质层;其中,所述第一电极的内壁位于所述第一电极所包围的区域内;所述第一电极的外壁位于所述第一电极所包围的区域外;

32、形成覆盖所述第二介质层的表面的第二电极;其中,所述第二介质层的表面包括位于所述第一电极所包围的区域内的第一表面以及位于所述第一电极所包围的区域外的第二表面。

33、在一些实施例中,所述基于所述凹陷结构的内壁的形貌形成第一电极,包括:

34、在所述凹陷结构的内壁覆盖第一牺牲材料;

35、在覆盖有所述第一牺牲材料的所述凹陷结构中填充第二牺牲材料;

36、去除所述第一牺牲材料,在所述第二牺牲材料中形成第一空隙;

37、在所述第一空隙的内壁进行原子层沉积,形成所述第一电极。

38、在一些实施例中,所述形成覆盖所述第一电极的内壁和部分外壁的第二介质层,包括:

39、去除所述第二牺牲材料和至少部分所述第一介质层,形成第二空隙;所述第一电极的部分外壁暴露在所述第二空隙中;

40、形成覆盖所述第一电极的内壁和所述部分外壁的第二介质层。

41、在一些实施例中,所述在所述堆叠结构中,沿平行于所述衬底表面的第一方向形成第一隔离层,包括:

42、刻蚀所述堆叠结构,形成平行的两条第一沟槽;所述第一沟槽将所述堆叠结构划分为并列排布的第一晶体管区、电容区以及第二晶体管区;

43、在所述第一沟槽中填充第一介质材料,形成第一隔离层。

44、在一些实施例中,所述去除所述电容区的所述第一多晶硅层,形成多层用于容纳电容结构的凹陷结构,包括:

45、刻蚀所述电容区,形成平行于第一沟槽的第三沟槽,所述第三沟槽将所述电容区划分为并列的两个子电容区;

46、从所述第三沟槽,刻蚀所述堆叠结构,去除所述堆叠结构中位于所述电容区内的各层所述第一多晶硅层,在所述第三沟槽两侧分别形成多层用于容纳电容结构的凹陷结构。

47、在一些实施例中,所述在所述凹陷结构裸露出的所述第一隔离层中形成多个电容接触结构,包括:

48、从所述第三沟槽刻蚀所述第一隔离层,形成位于两个所述子电容区的所述凹陷结构一端的电容接触孔;

49、在所述电容接触孔内填充第一导电材料,形成所述电容接触结构。

50、在一些实施例中,所述方法还包括:

51、形成覆盖所述第三沟槽的内壁的第二介质材料;

52、在覆盖有所述第二介质材料的所述第三沟槽内填充多晶硅材料,形成第二隔离层。

53、在一些实施例中,所述基于所述凹陷结构的形貌形成多层的所述电容结构,包括:

54、基于所述凹陷结构位于两个所述子电容区的形貌,分别形成两组对称分布的多个层叠的所述电容结构。

55、在一些实施例中,所述方法还包括:

56、在所述电容区沿平行于所述衬底的第二方向刻蚀所述堆叠结构,形成多个第五沟槽;其中,所述第二方向与所述第一方向相交;

57、在所述第五沟槽中填充绝缘材料,形成第四隔离层;所述第四隔离层用于在所述电容区隔离多个所述电容结构。

58、第三方面,本公开实施例提供了一种存储器,包括:

59、存储单元阵列;所述存储单元阵列包括上述第一方面的半导体结构;以及与所述存储单元阵列耦接的外围电路。

60、本公开实施例提供的一种半导体结构、半导体结构制造方法以及存储器,其中,半导体结构至少包括第一电极,所述第一电极包括:多个平行于所述衬底表面的第一部分和多个垂直于所述衬底表面的第二部分,且第一部分和所述第二部分交替首尾相连;根据第一电极的形状形成第二介质层和第二电极,从而在一定尺寸的半导体器件上构建叠层结构的电容结构,使得第一电极与第二电极的正对面积增大,从而增大该叠层电容结构的电容,进而提高具备该电容结构的存储器的存储容量。

- 还没有人留言评论。精彩留言会获得点赞!