三维存储器设备及其形成方法与流程

本公开内容的实施例涉及三维(3d)存储器设备及其制造方法。

背景技术:

1、通过改进工艺技术、电路设计、编程算法和制造工艺,将平面存储单元缩小到更小的尺寸。然而,随着存储单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性且成本高昂。结果,平面存储单元的存储密度接近上限。3d存储器架构可以解决平面存储单元中的密度限制问题。

技术实现思路

1、本文公开了3d存储器设备及其形成方法的实施例。

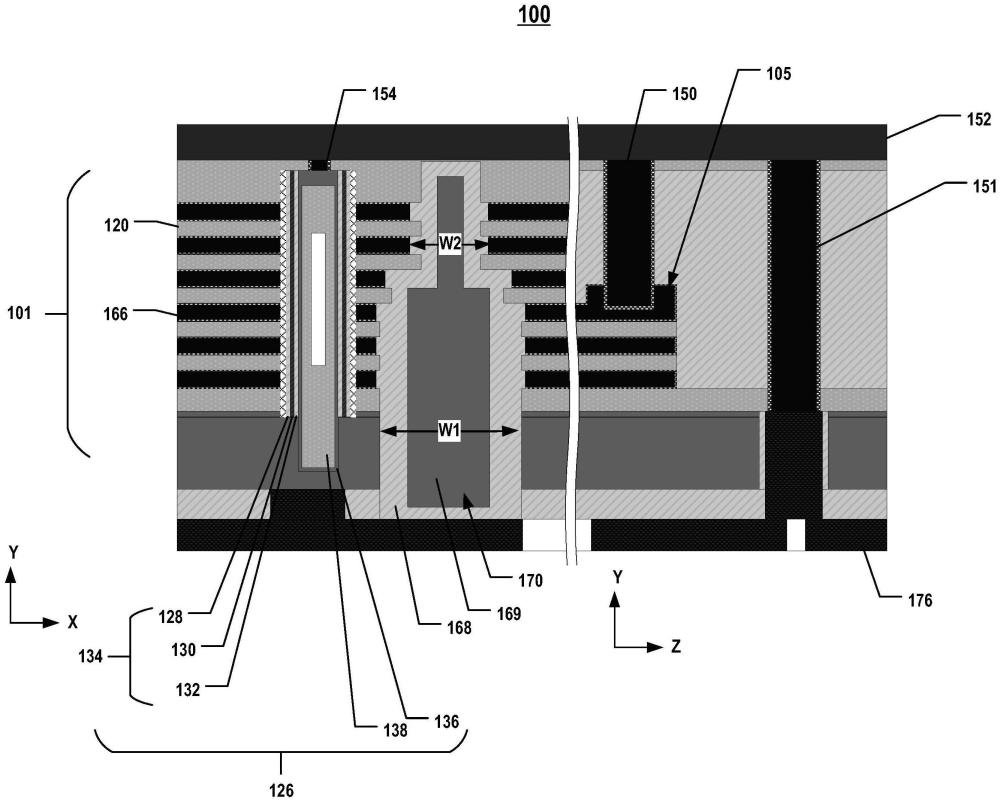

2、在一个方面,公开了一种3d存储器设备。该3d存储器设备包括存储器设备。该存储器设备包括堆叠体结构、沟道结构和缝隙结构。所述堆叠体结构包括交错的导电层和电介质层,并且所述导电层包括多条字线。所述沟道结构中的每一个沟道结构垂直地延伸穿过所述堆叠体结构。所述缝隙结构垂直地延伸穿过所述堆叠体结构。所述堆叠体结构的外部区域包括阶梯结构,并且所述堆叠体结构的底部部分中的交错的导电层和电介质层比所述堆叠体结构的顶部部分中的交错的导电层和电介质层宽。所述堆叠体结构的底部部分中的所述缝隙结构的第一外部宽度大于所述堆叠体结构的顶部部分中的所述缝隙结构的第二外部宽度。

3、在一些实施方式中,所述3d存储器设备还包括设置在所述存储器设备上方并与所述多个沟道结构电接触的外围设备。

4、在一些实施方式中,所述3d存储器设备还包括设置在所述堆叠体结构下方的互连结构。所述互连结构和所述外围设备设置在所述堆叠体结构的相对侧处。

5、在一些实施方式中,所述3d存储器设备还包括垂直地延伸穿过所述堆叠体结构的多个接触结构。所述多个接触结构中的每一个接触结构分别与所述多条字线中的一条字线电接触。

6、在一些实施方式中,所述字线在所述字线的边缘部分处与所述接触结构电接触,并且所述字线的所述边缘部分具有比所述字线的其它部分大的厚度。

7、在另一个方面,公开了一种系统。该系统包括被配置为存储数据的3d存储器设备、以及存储器控制器,所述存储器控制器耦合到该3d存储器设备并且被配置为控制该3d存储器设备的操作。所述3d存储器设备包括存储器设备。该存储器设备包括堆叠体结构、多个沟道结构和缝隙结构。所述堆叠体结构包括交错的导电层和电介质层,并且所述导电层包括多条字线。所述多个沟道结构中的每一个垂直地延伸穿过所述堆叠体结构。所述缝隙结构垂直地延伸穿过所述堆叠体结构。所述堆叠体结构的外部区域包括阶梯结构,并且所述堆叠体结构的底部部分中的交错的导电层和电介质层比所述堆叠体结构的顶部部分中的交错的导电层和电介质层宽。所述堆叠体结构的底部部分中的所述缝隙结构的第一外部宽度大于所述堆叠体结构的顶部部分中的所述缝隙结构的第二外部宽度。

8、在又一个方面,公开了一种用于形成3d存储器设备的方法。在衬底上形成包括交错的多个第一电介质层和多个第一牺牲层的电介质堆叠体。形成垂直地延伸穿过所述电介质堆叠体的多个沟道结构。从所述电介质堆叠体的顶侧形成第一开口。从所述电介质堆叠体的底侧形成与所述第一开口对准和连通的第二开口。利用多条字线来替换所述多个第一牺牲层。在所述第一开口和所述第二开口中形成缝隙结构。

9、在一些实施方式中,所述第二开口的外部宽度大于所述第一开口的外部宽度。

10、在一些实施方式中,在所述衬底上形成第一半导体层,在所述第一半导体层中形成第二电介质层,并且在所述第一半导体层和所述第二电介质层上形成包括交错的多个第一电介质层和多个第一牺牲层的电介质堆叠体。

11、在一些实施方式中,在所述第一半导体层中形成沟槽,并且在所述沟槽中形成所述第二电介质层。

12、在一些实施方式中,在所述电介质堆叠体的外部区域处形成阶梯结构,从所述电介质堆叠体的顶侧形成所述第一开口,所述第一开口垂直地对准所述第二电介质层,并且在所述第一开口中形成第二牺牲层。

13、在一些实施方式中,所述第二牺牲层包括碳化硅。

14、在一些实施方式中,在所述阶梯结构上方形成第三电介质层,并且形成垂直地延伸穿过所述第三电介质层的多个接触结构,所述多个接触结构中的每一个接触结构与所述多个第一牺牲层中的一个第一牺牲层接触。

15、在一些实施方式中,在所述电介质堆叠体上形成与所述多个沟道结构和所述多个接触结构电接触的外围设备。

16、在一些实施方式中,去除所述衬底和所述第一半导体层,在所述第二电介质层周围形成第二半导体层,从所述电介质堆叠体的所述底侧去除所述第二电介质层和去除所述电介质堆叠体的一部分,并且从所述电介质堆叠体的底侧去除所述第一开口中的所述第二牺牲层。

17、在一些实施方式中,执行蚀刻操作,以去除所述第二电介质层和去除所述电介质堆叠体的所述部分,直到被所述第二牺牲层停止为止。

18、在一些实施方式中,通过所述第一开口和所述第二开口去除所述多个第一牺牲层,以形成多个空腔,并且在所述多个空腔中形成所述多条字线。

19、在一些实施方式中,所述缝隙结构的底部部分的外部宽度大于所述缝隙结构的顶部部分的外部宽度。

20、在又一个方面,公开了一种用于形成3d存储器设备的方法。在衬底上形成第一半导体层。在所述第一半导体层中形成第一电介质层。在所述第一电介质层和所述第一半导体层上形成包括交错的多个第二电介质层和多个第一牺牲层的电介质堆叠体。形成垂直地延伸穿过所述电介质堆叠体的多个沟道结构。形成在所述电介质堆叠体的顶部部分中垂直地延伸的第二牺牲层。从所述电介质堆叠体的底侧去除所述第一电介质层和所述第二牺牲层以形成第一开口。在所述第一开口中形成缝隙结构。

21、在一些实施方式中,在所述第一半导体层中形成沟槽,并在所述沟槽中形成所述第二电介质层。

22、在一些实施方式中,形成在所述电介质堆叠体的所述顶部部分中垂直地延伸的第二开口,在所述3d存储器设备的平面图中,所述第二开口与所述第一电介质层重叠,并且在所述第二开口中形成所述第二牺牲层。

23、在一些实施方式中,所述第二牺牲层包括碳化硅。

24、在一些实施方式中,去除所述衬底和所述第一半导体层,在所述第一电介质层周围形成第二半导体层,从所述电介质堆叠体的底侧去除所述第一电介质层和去除所述电介质堆叠体的一部分,并且从所述电介质堆叠体的所述底侧去除所述电介质堆叠体的顶部部分中的所述第二牺牲层。

25、在一些实施方式中,减薄所述第二半导体层,在所述第二半导体层和所述第一电介质层之上形成掩模层,在所述掩模层之上形成第三电介质层,执行平坦化操作以去除所述第三电介质层的一部分和所述掩模层的一部分,并且执行蚀刻操作,以从所述电介质堆叠体的底侧去除所述第一电介质层和所述第二牺牲层。

26、在一些实施方式中,从所述电介质堆叠体的底侧去除所述第一电介质层、所述电介质堆叠体的一部分和所述第二牺牲层。

27、在一些实施方式中,在所述电介质堆叠体的外部区域处形成阶梯结构。

28、在一些实施方式中,在所述阶梯结构上方形成第四电介质层,并且形成垂直地延伸穿过所述第四电介质层的多个接触结构,所述多个接触结构中的每一个接触结构与所述多个第一牺牲层中的一个第一牺牲层接触。

29、在一些实施方式中,在电介质堆叠体上形成与所述多个沟道结构和所述多个接触结构电接触的外围设备。

30、在一些实施方式中,利用多条字线替换所述多个第一牺牲层。

31、在一些实施方式中,通过所述第一开口和所述第二开口去除所述多个第一牺牲层以形成多个空腔,并且在所述多个空腔中形成所述多条字线。

32、在一些实施方式中,所述缝隙结构的底部部分的外部宽度大于所述缝隙结构的顶部部分的外部宽度。

- 还没有人留言评论。精彩留言会获得点赞!