射频功率放大器和用于制作多赫帝功率放大器的方法与流程

本发明实施例关于一种射频电路设计及其制造方法,尤其是一种射频功率放大器和用于制作多赫蒂功率放大器(如正向或反向多赫蒂功率放大器)的方法及其相关改进。

背景技术:

1、在即将到来的5g mimo应用中,对高效率的功率放大器的需求不断地在增加。此外,高频宽是在微波通讯应用下对于5g和其他标准中为了实现高速数据传输所不可或缺的需求。传统的开关式多赫蒂(doherty)功率放大器因为可以采用谐波负载消除架构(例如f类、f-1类等)以提供较佳的回退效率而被广泛的采用,但其在于频宽方面会受到必须使用窄频的四分之一波长传输线,而具有较严重的限制。

2、为了解决所述的频宽限制问题,有很多的解决方案被提出。然而,始终没有可行的方案可在整合谐波消除架构的前提下同时实现高效率。因此,目前在产业中所使用的多赫蒂功率放大器中,因需要使用寄生补偿技术,因此通常需要在高效率和高频宽之间做出取舍。如先前所解释,由于谐波网路设计的困难和规模的复杂性,即使一些器件寄生效应可用于提供较佳的频宽,但也无法同时用于消除谐波以实现高效率设计。类似地,若器件寄生效应被用作于谐波负载消除的设计以提供较佳的效率,则器件寄生效应则会造成频宽的限制,另外因为这样的设计必须使用额外的四分之一波长传输线和偏移线的配置,此配置也会进一步造成频宽的缩减,同时也会造成电路体积庞大,无法实现微小化和集成化的目的。

3、因此,在现有采用开关式功率放大器架构作为谐波匹配网路的多赫蒂功率放大器中,通常仅能实现高效率但是具有低频宽(窄频宽设计)并且电路设计复杂而具有庞大的尺寸。如此的设计不适于应用在单片微波集成电路(monol ithic microwave integratedcircuits,mmic)、混合ic或其他类型的分散式射频电路应用中。

技术实现思路

1、本发明的实施例通过使用阻抗逆变网路取代基本匹配网路来解决射频功率放大器的频宽过窄问题,同时还消除负载谐波的寄生效应。

2、本发明的实施例还实现了使开关式射频放大器的电路设计有效地微小化的功效。

3、本发明的实施例更解决了现今应用于产业中的多赫蒂功率放大器的主要问题,像是频宽和效率之间的取舍。本发明的实施例还解决了效率跟尺寸最小化之间的取舍问题,使得根据本发明的实施例设计的功率放大器可不只提供高回退效率的特性,还可同时实现尺寸最小化和高频宽的效果。

4、本发明实施例还解决了在设计可控制二次谐波和三次谐波的开关式多赫蒂功率放大器时所遭遇的设计过于复杂和尺寸过大的问题。

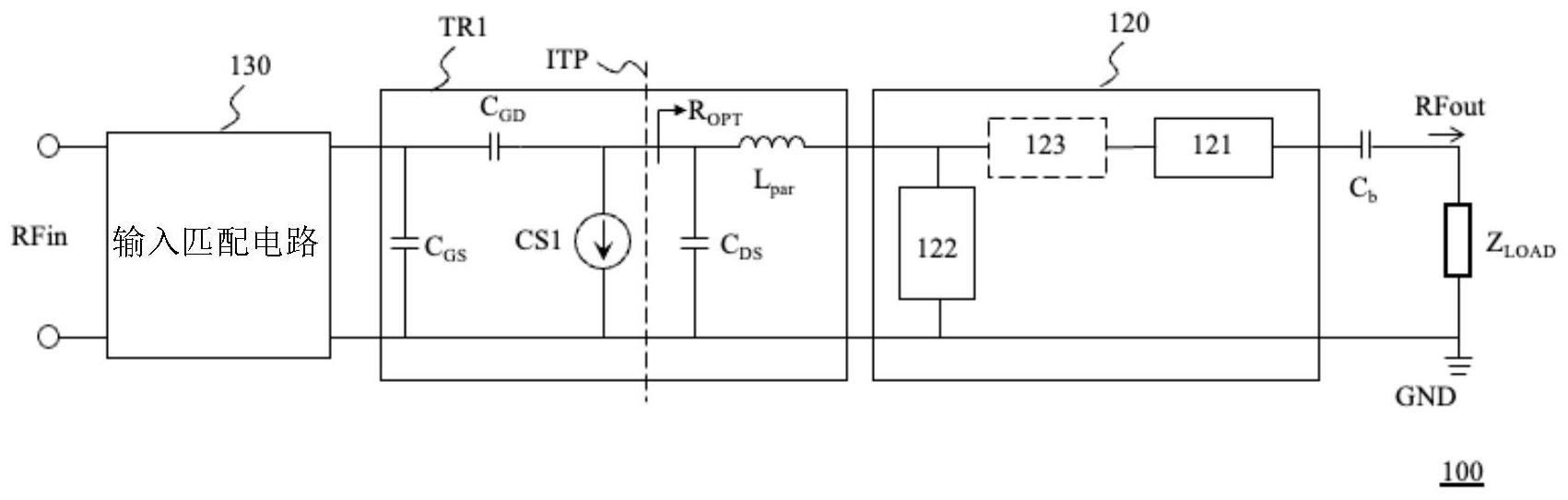

5、本发明提出一种射频功率放大器,其适于操作在基频并用以电性连接一负载,所述射频功率放大器包括至少一电晶体以及混成匹配电路。所述混成匹配电路电性连接于所述至少一电晶体的汲极和所述负载之间,其中所述混成匹配电路包括:一第一电路,其第一端电性连接所述至少一电晶体的所述汲极,且其第二端电性连接所述负载;以及一第二电路,电性连接于所述至少一电晶体的所述汲极和一射频接地端之间,其中所述第一电路和所述至少一电晶体的一输出寄生元件在所述基频下作为所述射频功率放大器的一阻抗逆变器工作,并且所述第二电路在所述基频下提供相对于所述射频接地端的一高阻抗路径,以及其中所述第二电路用以在所述基频的一第一目标谐波的频率下,提供相对于所述射频接地端的一阻抗,使从所述至少一电晶体的本质平面(intrins ic plane)观察到的阻抗为一高阻抗和一低阻抗其中之一,以消除所述第一目标谐波。所述第二电路可用以在所述基频的一第二目标谐波的频率下,提供相对于所述射频接地端的一阻抗,使从所述至少一电晶体的所述本质平面观察到的阻抗为一高阻抗和一低阻抗其中之另一,以消除所述第二目标谐波。

6、其中,当所述至少一电晶体为单一电晶体时,所述单一电晶体的谐波匹配网路是至少基于所述单一电晶体的至少一输出寄生元件、所述第一电路以及所述第二电路形成;以及当所述至少一电晶体为多个电晶体时,所述多个电晶体其中之一的谐波匹配网路是至少基于所述多个电晶体其中之一的输出寄生元件、所述第一电路以及所述第二电路形成。

7、其中,所述第一目标谐波的频率为所述基频的二次谐波频率,以及所述第二目标谐波的频率为所述基频的三次谐波频率。

8、其中,在所述基频的第二谐波频率下,从所述至少一电晶体的本质平面观察到的阻抗为所述低阻抗;并且在所述基频的第三谐波频率下,从所述至少一电晶体的本质平面观察到的阻抗为所述低阻抗。

9、其中,所述第一电路包括:

10、一传输电路,电性连接于所述第一端和所述第二端之间;

11、一第一电抗元件,电性连接于所述第一端和所述第二端其中之一与所述射频接地端之间;以及

12、一第二电抗元件,电性连接于所述第一端和所述第二端其中之另一与所述射频接地端之间。

13、其中,所述传输电路包括一电感和一传输线中的至少一者。

14、其中,所述第二电路包括一电容性元件以及二电感性元件,所述电容性元件与所述二电感性元件其中之一并联,并且所述电容性元件与所述二电感性元件其中之另一串联。

15、其中,所述电容性元件和所述电感性元件包括:

16、一第一电容性元件;

17、一第一电感性元件,与所述第一电容性元件串联,并且介于所述至少一电晶体的汲极与所述射频接地端之间;以及

18、一第二电感性元件,其一端电性连接所述至少一电晶体的汲极和所述第一端,其另一端电性连接所述射频接地端。

19、其中,所述第一电容性元件和所述第一电感性元件的尺寸被设计为在所述基频的所述第一目标谐波的频率下,提供连接至所述射频接地端的一低阻抗路径。

20、其中,所述第二电感性元件的尺寸被设计为在所述基频下,使所述第一电容性元件、所述第一电感性元件以及所述第二电感性元件等效为相对于所述射频接地端的开路。

21、其中,所述第一电容性元件以一电容实施,所述第一电感性元件和第二电感性元件各自以电感和传输线中的至少一者作为一部分或整体来实施,所述电容、所述电感以及所述传输线的尺寸符合以下公式:

22、

23、

24、z21tan(θ21)=ω0l21;

25、z22tan(θ22)=ω0l22;

26、z21′tan(θ21′)+ω0l21′=ω0l21;

27、z22′tan(θ22′)+ω0l22′=ω0l21;

28、其中c21为所述电容的电容值,l21为用以实施所述第一电感性元件的电感的电感值,l22为用以实施所述第二电感性元件的电感的电感值,z21为用以实施电感值为l21的所述第一电感性元件的传输线的特征阻抗,z22为用以实施电感值为l22的所述第二电感性元件的传输线的特征阻抗,ωo为所述基频,n为谐波次数指标,θ21为用以实施电感值为l21的所述第一电感性元件的传输线的电角度,θ22为用以实施电感值为l22的所述第二电感性元件的传输线的电角度,z21′和θ21′为用以搭配电感l21'来实施电感值为l21的所述第一电感性元件的传输线的特征阻抗和电角度,以及z22′和θ22′为用以搭配电感l22'来实施电感值l22的所述第二电感性元件的传输线的特征阻抗和电角度。

29、其中,所述阻抗逆变器包括以下架构中的至少一者:n级低通集总式四分之一波长变换器、四分之一波长短截传输线、准集总式n阶低通滤波器、准集总式n阶低通四分之一波长转换器、准集总式低通柴比雪夫转换器、准集总式低通柴比雪夫四分之一波长转换器、准集总式低通四分之一波长步阶阻抗转换器以及准集总式低通四分之一波长步阶阻抗四分之一波长转换器。

30、其中,所述电容性元件和所述电感性元件包括:

31、一第一电感性元件;以及

32、一电感电容谐振回路,与所述第一电感性元件串联,并且电性连接于所述至少一电晶体的汲极与所述射频接地端之间,其中:

33、所述电感电容谐振回路包括相互并联的一第二电感性元件以及一第一电容性元件,

34、其中所述第一电感性元件和所述第二电感性元件用以在连接所述第二电路的所述电晶体的本质平面提供第二谐波高阻抗、第二谐波低阻抗以及第三谐波低阻抗中的至少一者,

35、其中所述第二电感性元件和所述第一电容性元件用以在基频下基于以下公式提供相对于所述射频接地端的高阻抗路径:

36、

37、其中lch为所述第二电感性元件的电感值,cch为所述第一电容性元件的电容值,以及ωo为基频。

38、本发明提出一种制造多赫蒂功率放大器的方法,包括以下步骤:提供操作在一基频的至少一主放大器;提供与所述至少一主放大器并联且共享一共同负载或一负载的至少一峰值放大器;以一第一混成匹配电路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中连接所述第一混成匹配电路包括:以一第一电路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中所述第一电路作为所述多赫蒂功率放大器的所述第一混成匹配电路的一阻抗逆变网路的一部分。

39、其中,连接所述第一混成匹配电路还包括:

40、以一第二电路连接于所述至少一主放大器的输出端和一射频接地端之间;

41、以一第三电路连接于所述至少一峰值放大器的输出端和所述射频接地端之间;

42、决定包含于所述第一电路的元件类型和尺寸,借以在所述基频下利用所述主放大器和所述峰值放大器其中之一的一输出寄生元件构成一阻抗逆变网路;

43、决定包含于所述第二电路和所述第三电路的元件尺寸,借以使所述第二电路和所述第三电路在所述基频下提供相对于所述射频接地端的一高阻抗,令所述阻抗逆变网路的功能不受影响;以及

44、决定包含于所述第二电路和所述第三电路的元件尺寸,借以利用至少所述第一电路、所述第二电路以及所述第三电路提供的阻抗,使从所述主放大器和所述峰值放大器的本质平面观察到的阻抗为一高阻抗和一低阻抗其中之一,以消除所述基频的二次谐波和三次谐波其中之一。

45、其中,连接所述第一混成匹配电路更包括:

46、决定包含于所述第二电路和所述第三电路的元件尺寸,借以利用至少所述第一电路、所述第二电路以及所述第三电路提供的阻抗,使从所述主放大器和所述峰值放大器的本质平面观察到的阻抗为一高阻抗和一低阻抗其中之一,以消除所述基频的二次谐波和三次谐波其中之另一。

47、其中,所述第一混成匹配电路的所述阻抗逆变网路包括以下架构中的至少一者:n级低通集总式四分之一波长变换器、四分之一波长短截传输线、准集总式n阶低通滤波器、准集总式n阶低通四分之一波长转换器、准集总式低通柴比雪夫转换器、准集总式低通柴比雪夫四分之一波长转换器、准集总式低通四分之一波长步阶阻抗转换器以及准集总式低通四分之一波长步阶阻抗四分之一波长转换器。

48、其中,提供所述至少一峰值放大器包括提供至少两个峰值放大器,且所述方法还包括:

49、以至少一额外混成匹配电路连接于所述至少两个峰值放大器的输出端之间,使所述至少两个峰值放大器中的任意两个都与至少一混成匹配电路关联,其中所述第一混成匹配电路及所述一额外混成匹配电路被电性连接且共享所述共同负载,其中连接所述至少一额外混成匹配电路包括:

50、以一第一电路连接于所述至少一主放大器的输出端和所述至少两个峰值放大器的输出端之间,其中所述第一电路作为所述多赫蒂功率放大器的所述至少一额外混成匹配电路的一阻抗逆变网路的一部分。

51、本发明提出另一种制造多赫蒂功率放大器的方法,包括以下步骤:提供操作在一基频的至少一主放大器;提供与所述至少一主放大器并联且共享一共同负载或一负载的至少一峰值放大器;以一第一混成匹配电路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中连接所述第一混成匹配电路包括:以一第一电路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中所述第一电路作为所述多赫蒂功率放大器的所述第一混成匹配电路的一阻抗逆变网路的一部分;以一第二混成匹配电路或一额外阻抗逆变网路和一寄生消除分流网路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中所述第一混成匹配电路及所述第二混成匹配电路,或所述第一混成匹配电路、所述至少一额外混成匹配电路和一寄生消除分流网路被所述阻抗逆变网路连接在一起且共享所述共同负载,其中连接所述第二混成匹配电路包括:以一第一电路连接于所述至少一主放大器的输出端和所述至少一峰值放大器的输出端之间,其中所述第二混成匹配电路的所述第一电路作为所述多赫蒂功率放大器的所述第二混成匹配电路的一阻抗逆变网路的一部分。

52、其中,连接所述第一混成匹配电路和所述第二混成匹配电路的所述阻抗逆变网路包括以下架构中的至少一者:四分之一波长转换器、n阶高通四分之一波长转换器、n阶低通四分之一波长转换器、n级低通集总式四分之一波长变换器、n级高通集总式四分之一波长变换器、四分之一波长短截传输线、准集总式n阶低通滤波器、准集总式n阶高通滤波器、准集总式n阶低通四分之一波长转换器、准集总式低通柴比雪夫转换器、准集总式低通柴比雪夫四分之一波长转换器、准集总式低通四分之一波长步阶阻抗转换器、准集总式低通四分之一波长步阶阻抗四分之一波长转换器、准集总式n阶高通四分之一波长转换器、准集总式高通柴比雪夫转换器、准集总式高通柴比雪夫四分之一波长转换器、准集总式高通四分之一波长步阶阻抗转换器、准集总式高通四分之一波长步阶阻抗四分之一波长转换器,以及低通和高通集总式或分散式四分之一波长转换器的组合。

53、其中,所述第二混成匹配电路的所述阻抗逆变网路包括以下架构中的至少一者:n级低通集总式四分之一波长变换器、四分之一波长短截传输线、准集总式n阶低通滤波器、准集总式n阶低通四分之一波长转换器、准集总式低通柴比雪夫转换器、准集总式低通柴比雪夫四分之一波长转换器、准集总式低通四分之一波长步阶阻抗转换器以及准集总式低通四分之一波长步阶阻抗四分之一波长转换器。

54、其中,提供所述至少一峰值放大器包括提供至少两个峰值放大器,且所述方法还包括:

55、以至少一额外混成匹配电路连接于所述至少两个峰值放大器的输出端之间,使所述至少两个峰值放大器中的任意两个都与一混成匹配电路关联,其中所述第一混成匹配电路、所述第二混成匹配电路及所述至少一额外混成匹配电路被所述阻抗逆变网路连接在一起且共享所述共同负载,其中连接所述至少一额外混成匹配电路包括:

56、以一第一电路连接于所述至少两个峰值放大器的输出端之间,其中所述第一电路作为所述多赫蒂功率放大器的所述至少一额外混成匹配电路的一阻抗逆变网路的一部分。

57、本发明提出一种操作在一基频的射频功率放大器,所述射频功率放大器用以电性连接一负载,并且包括:至少一电晶体;谐波消除电路,其一端直接连接所述至少一电晶体的汲极,且其另一端电性连接射频接地端,其中谐波消除电路在所述基频的二次谐波频率和三次谐波频率其中之一作为所述至少一电晶体的谐波匹配网路的一部分;以及阻抗逆变器,具有第一端电性连接所述至少一电晶体的汲极,并且具有第二端电性连接所述负载,所述阻抗逆变器用以在不影响谐波消除电路的前提下,进行对静态阻抗的阻抗逆变,或对在基频的调变阻抗的阻抗逆变。

58、本发明通过使用称之为“混成匹配网路”的新型的连接网路来设计新的多赫蒂功率放大器,其可被整合在产业应用中的任何射频应用。虽然本发明的说明集中在于多赫蒂功率放大器的混成匹配网路的应用,但其也可以用于各类开关式或连续式放大器架构中,像是f类、f-1类、j类、e类、连续f类、连续f-1类、连续j类、连续e类等放大器架构。

- 还没有人留言评论。精彩留言会获得点赞!