用于PCB布局的宽带布线技术的制作方法

用于pcb布局的宽带布线技术

背景技术:

1.本公开总体上涉及印刷电路板(pcb)上信号布线的设计。更具体地,本公开涉及pcb上集成电路器件的贯穿区域(escape region)内的宽带信号路径的布线技术。

附图说明

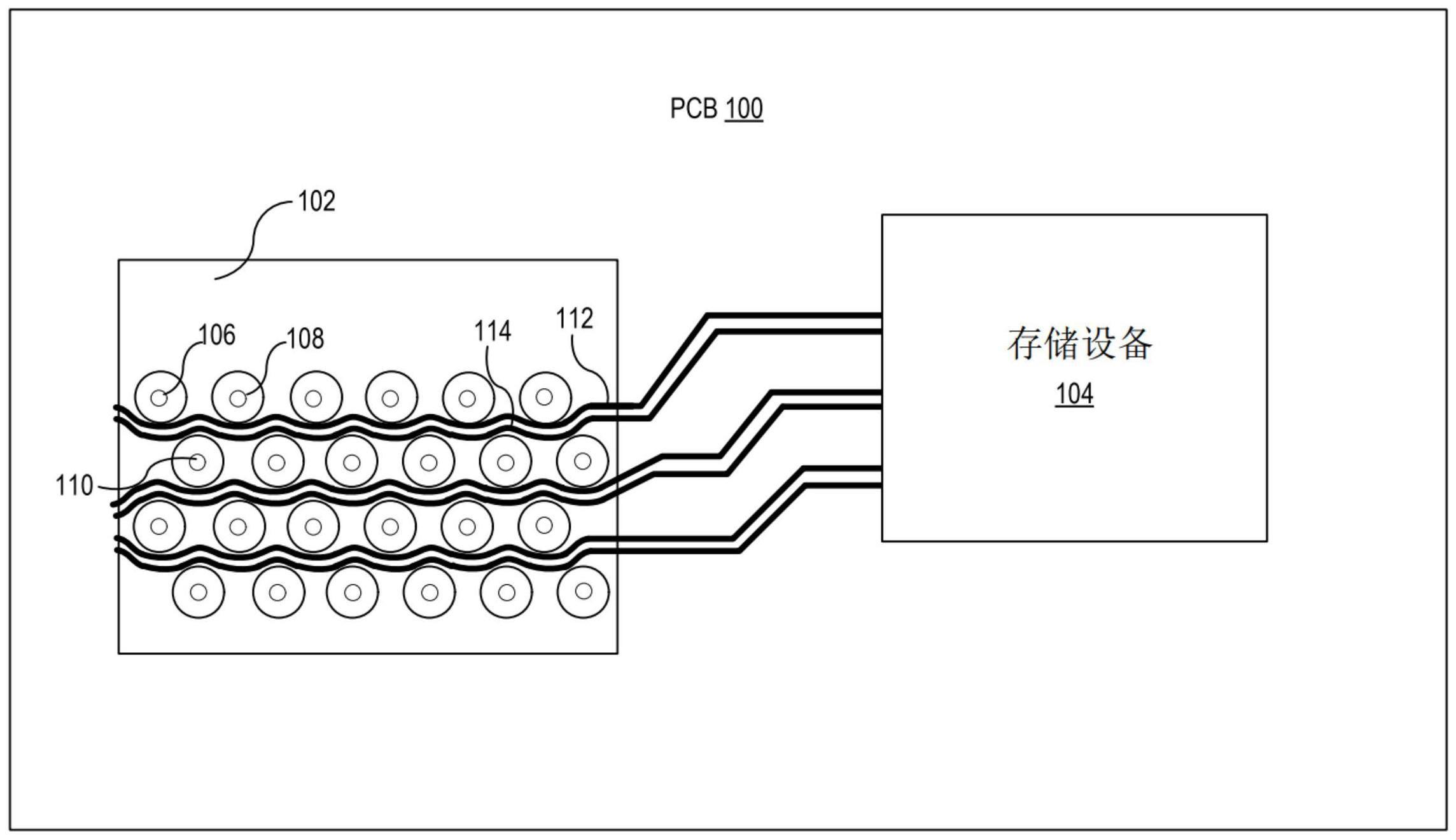

2.图1图示了从片上系统(soc)器件的管脚场(pin field)过孔阵列贯穿的多个高速信号迹线。

3.图2图示了根据本技术的一个方面的布线穿过过孔阵列的多个高速信号迹线。

4.图3图示了根据本技术的一个方面的过孔反焊盘和信号迹线的放大视图。

5.图4图示了根据本技术的一个方面的信号迹线的对称布线。

6.图5图示了根据本技术的一个方面的信号迹线绕信号过孔和接地过孔的布线。

7.图6图示了根据本技术的一个方面的具有加宽段的信号迹线。

8.图7呈现了根据本技术的一个方面的图示了在pcb上设计贯穿布线的过程的流程图。

9.在这些附图中,相同的附图标记指代相同的附图元素。

具体实施方式

10.以下描述被呈现以使得本领域的任何技术人员能够制造和使用示例,并且在特定应用及其要求的上下文中被提供。对所公开示例的各种修改对于本领域技术人员来说将是清楚的,并且在不脱离本公开的精神和范围的情况下,本文定义的一般原理可以应用于其他示例和应用。因此,本公开的范围不限于所示示例,而旨在符合与本文公开的原理和特征一致的最大范围。

11.本公开提供了一种用于对从表面安装集成电路器件(诸如球栅阵列(bga)封装或平面网格阵列(lga)封装)贯穿的宽带单端信号迹线进行布线的解决方案。根据第一方面,一对单端信号迹线可以布置在集成电路器件的过孔阵列的相邻行之间。可以通过向这两个信号迹线中的一个信号迹线(例如,上信号迹线)增加额外长度来调节这两个单端信号迹线之间的间隔。更具体地,可以向相邻两个过孔反焊盘之间的每个位置处的信号迹线增加附加长度,使得该信号迹线远离该位置处的另一个信号迹线进行布线。该增加长度增大了信号迹线之间的间隙,从而减少了信号迹线之间的串扰。根据第二方面,可以向两个信号迹线增加附加长度以增大总体间隙,而不会导致这两个信号迹线之间存在显著的长度差异。根据第三方面,信号迹线可以更接近接地过孔布线,因为参考平面不具有过孔反焊盘。这可以增大与接地过孔相邻的位置处信号迹线之间的间隙,并且可以打破贯穿布线的重复性周期结构,从而进一步减少信号迹线之间的串扰量。此外,可以在相邻过孔反焊盘之间的位置处加宽信号迹线的宽度,以降低单端信号迹线的阻抗。

12.片上系统(soc)技术的发展导致了高速输入/输出(i/o)通道数量的增加以及存储器通道数量的增加。一般来说,每一次较新一代soc的信号数量都会增加。这可能导致soc封

装尺寸增加,从而增加了soc封装下pcb上管脚场区域中的信号路径长度,该soc封装可以是bga封装或lga封装。

13.增加的路径长度会对沿着路径传播的信号、特别是高速信号的质量产生负面影响。例如,通常的soc可以具有多个单端高速/宽带信号通道,诸如双倍数据速率4或5(ddr4或ddr5)存储器通道。注意,ddr5存储器通道可以支持每秒数千兆次(mt/s)的数据传输速率,这要求通道带宽远远超过3ghz。当多个(例如,两个)这种高速信号被彼此平行地布线,达到电学意义上的显著距离(例如,比信号的上升时间所经过的距离更长的距离)时,长耦合长度和相邻焊盘或过孔的影响会对信号质量产生不利影响,使串扰增加,并且频率依赖阻抗发生变化。

14.图1图示了贯穿soc器件的管脚场过孔阵列的多个高速信号迹线。在图1中,示出了pcb 100的局部俯视图。pcb 100可以是多层pcb,并且可以包括安装在其表面上的多个器件,包括soc器件102和存储器件104。soc器件102和存储器件104可以通过多个单端高速信号迹线互连。soc器件102可以是包括管脚阵列的bga封装或lga封装。注意,图1中仅示出了pcb 100的一部分。图1还示出了定位在soc器件102下方的过孔阵列(例如,过孔106、108和110)。在pcb 100中包括过孔允许内部pcb信号布线层上的信号迹线(例如,迹线112和114)连接到soc器件102的管脚/焊盘。过孔阵列的存在也使从soc器件102的管脚场贯穿的信号迹线的布线变得复杂。更具体地,信号迹线必须在过孔的相邻行之间的间隔内布线,这被称为布线通道。如图1中所示,信号迹线112和114在过孔阵列的顶行与过孔阵列的第二行之间的通道中布线。

15.在图1中示出的示例中,过孔阵列以交错的方式布置,其中相邻行的过孔在位置上有所偏移。例如,过孔106和108处于同一行,过孔110处于相邻行,并且过孔110不是与过孔106或108对准,而是与过孔106和108之间的中点对准。注意,过孔阵列的模式与封装的接触管脚/焊盘的模式(图1中未示出)一致。交错的管脚/焊盘阵列使得管脚场的密度更紧密。与此同时,紧密布置的管脚/焊盘和过孔会使贯穿布线更具挑战性。与非交错阵列相比,布线通道的宽度(即,相邻两行之间的空间)可以小得多,这意味着每个通道中的一对单端信号迹线(例如,迹线112和114)之间的距离可以更小。

16.在图1中示出的示例中,每个布线通道中的一对信号迹线基本上是彼此平行延伸的,这可能会导致串扰量相当大。随着soc器件102的尺寸的增加(例如,由于存储器通道计数的增加),需要从soc器件102的管脚场贯穿的信号迹线(例如,迹线112和114)的长度也会增加,从而导致这些相邻信号迹线之间的串扰增加。为了减少串扰,根据本技术的一个方面,布线通道中的信号迹线可以以不同于图1所示的方式进行布线。更具体地,除了使用相邻过孔行之间的空间之外,布线通道还可以使用同一行中相邻过孔之间的空白空间来对信号迹线进行布线。

17.图2图示了根据本技术的一个方面的通过过孔阵列布线的多个高速信号迹线。在图2中,特定的信号迹线层200可以包括多个信号迹线以及过孔反焊盘阵列。注意,术语“过孔反焊盘”通常指pcb的参考金属层上的空隙。为了保持信号完整性,信号迹线不应在参考平面上的空隙上方布线。由于该“阻进”区域可以由参考平面上对应过孔反焊盘的外径来定义,因此我们也可以使用术语“过孔反焊盘”来描述信号平面上由于存在过孔而导致信号迹线无法布线的区域。

18.图2示出了包括过孔反焊盘202和204的过孔反焊盘的阵列。注意,外圆定义了过孔反焊盘的外部边界,而内圆是过孔的实际孔。图2中未示出过孔焊盘。在图2中,多个反焊盘(例如,过孔反焊盘214)被示出为使用虚线圆来表示这些反焊盘的外部边界。这些虚线过孔反焊盘对应于接地过孔。我们使用虚线圆来标记绕接地过孔的、与信号过孔的过孔反焊盘区域类似的区域,因为接地过孔实际上在接地参考平面上不具有过孔反焊盘。然而,在图2中示出的示例中,对接地过孔(其为连接到接地平面的过孔)和信号过孔(其承载信号)以类似方式进行处理,这意味着信号迹线以类似的方式绕信号过孔和接地过孔进行布线。

19.如前所述,信号迹线需要在过孔反焊盘的相邻行之间的布线通道中进行布线,并且一对信号迹线(例如,图1中示出的迹线112和114)之间的长耦合长度会增加串扰。为了减轻信号迹线之间的串扰,根据本技术的一个方面,可以向每个布线通道内的一对信号迹线中的至少一个信号迹线增加附加长度。可以在绕每个过孔反焊盘的周界的位置处以及同一行中相邻过孔反焊盘之间的位置处增加附加长度,使得信号迹线可以包裹(或“环绕”)每个过孔反焊盘的实质部分。

20.在图2中示出的示例中,可以在多个位置(例如,位置206和208)处向信号迹线210增加附加长度,使得信号迹线210被布线为包裹每个过孔反焊盘的周界的实质部分(例如,高达50%)或沿着每个过孔反焊盘的周界的实质部分弯曲。这意味着信号迹线210和212不再基本上彼此平行地延伸。这也意味着信号迹线210的实质部分(例如,位置206处的部分)已经延伸到了过孔反焊盘的相邻行之间的传统布线通道之外。另一方面,信号迹线212大部分保持在传统布线通道内。

21.增加到信号迹线210的长度可以周期性地增大信号迹线210和212之间的间隙。如图2中所示,信号迹线210和212之间的间隙可以在与信号迹线212相邻的一行的相邻过孔反焊盘之间的位置(例如,位置216)处具有最小值,并且可以在与信号迹线210相邻的一行的相邻两个过孔反焊盘之间的位置(例如,位置206)处达到最大值。更具体地,在相邻信号迹线(例如,迹线210和212)之间的间隔增大的位置处,沿着信号迹线传播的信号之间的耦合可以减小,从而减少总体串扰。一般来说,可以提高传播信号的信噪比(snr)。在一些情况下,snr可以提高5%到10%。

22.根据一个方面,可以在同一布线通道中的一对信号迹线之间选择具有总体距离较短的信号迹线来增加长度(或使较短的信号迹线绕每个过孔反焊盘的外部边界弯曲)。这样,信号迹线之间的总体长度差异可以保持相对较小。如果所选信号迹线的长度需要与同一pcb上不同信号迹线的长度相匹配,则可以在soc覆盖区之外的区域使用附加长度补偿方案。

23.图3图示了根据本技术的一个方面的过孔反焊盘和信号迹线的放大视图。在图3中,信号过孔反焊盘302和接地过孔反焊盘304是同一行中相邻的过孔反焊盘,而信号过孔反焊盘306处于相邻的一行中并定位在过孔反焊盘302和304之间。除了每个过孔反焊盘的外部边界之外,图3还示出了每个过孔的孔(例如,最里面的圆)和过孔焊盘(例如,交叉阴影区域)。

24.信号迹线310和312被示出为沿着两行过孔反焊盘之间的布线通道进行布线。更具体地,从过孔反焊盘302的周界上的一点开始,信号迹线310被布线为包裹过孔反焊盘302的实质部分(其可以高达50%,例如,介于25%到50%之间或介于40%到50%之间)或沿着过

孔反焊盘的实质部分弯曲,然后再远离过孔反焊盘302进行布线。根据一个方面,过孔反焊盘的周界的包裹部分的弧角(例如,θ)可以介于π/2(或90

°

)到π(或180

°

)之间。θ越大,信号迹线310和312之间的间隙就越大。根据一个方面,信号迹线310的边缘与对应的过孔反焊盘的外部边界之间的距离可以保持最小(例如,保持在符合制造公差的值),以防止信号迹线310进入过孔反焊盘区域,同时保持信号迹线310尽可能地远离信号迹线312。

25.图3还示出:从最低点开始,随着信号迹线310沿着过孔反焊盘302的边缘进行布线并且然后远离过孔反焊盘302,信号迹线310和312之间的间隙会增大。间隙值基本上在过孔反焊盘302和304之间的中点处达到其最大值。从中点开始,信号迹线310折回并朝向过孔反焊盘304进行布线,从而包裹过孔反焊盘304的周界的一部分或沿着过孔反焊盘的周界的一部分弯曲。注意,为了增大信号迹线310和312之间的间隙,期望的是,使信号迹线310尽可能地远离信号迹线312进行布线。然而,由于信号迹线不能在由过孔反焊盘(例如,过孔反焊盘302和304)占据的区域上方布线,因此沿着(或紧邻)过孔反焊盘的周界对信号迹线310进行布线实际上可以提供最大的间隙量。还应注意,在过孔反焊盘302和304之间的中点处,可以通过使信号迹线310进一步远离信号迹线312进行布线来增大间隙。然而,还需要考虑信号迹线310与相邻布线通道内的另一个信号迹线之间的距离。根据一个方面,可以确定中点处同一布线通道内的相邻信号迹线之间的间隙,以确保相邻布线通道的相邻信号迹线之间的间隙不小于预定阈值。

26.在图2和图3中示出的示例中,布线通道中的一对信号迹线以非对称方式被布线。这种方案可以在某些位置处(例如,在同一行中的相邻过孔反焊盘之间的中点处)使信号迹线之间的间隙最大化。然而,这种非对称布线方案可能导致信号迹线之间的长度差异较大,这有时可能是有问题的。为了在减少信号串扰的同时减小迹线长度差异,根据一个方面,每个布线通道中的信号迹线可以基本上对称地布线。

27.图4图示了根据本技术的一个方面的信号迹线的对称布线。在图4中,信号平面400包括过孔反焊盘(例如,过孔反焊盘402、404和406)的阵列以及多个信号迹线(例如,迹线410和412)。更具体地,过孔反焊盘402和404定位在顶行,过孔反焊盘406定位在第二行,并且信号迹线410和412在顶行与第二行之间的布线通道中进行布线。注意,传统布线通道主要局限于相邻行之间的空白空间(例如,如图1中示出的示例),而本公开中的布线通道还包括同一行中相邻过孔反焊盘之间的空白空间。例如,过孔反焊盘402和404之间的空白空间现在可以用于布线信号迹线。

28.与图1至图3中示出的信号迹线相比,在图4中,每个布线通道中的两个信号迹线的长度都得到增加,使得每个信号迹线都可以包括包裹过孔反焊盘的实质部分的段。例如,信号迹线410包括绕过孔反焊盘402的周界的一部分弯曲的段以及绕过孔反焊盘404的周界的一部分弯曲的段。此外,信号迹线412包括绕过孔反焊盘406的周界的一部分弯曲的段。这可以使得过孔反焊盘周界的两个连续部分被信号迹线包裹(或“环绕”)。例如,过孔反焊盘402周界的上部部分可以被信号迹线414包裹,而其周界的下部部分可以被信号迹线410包裹。

29.在图4中示出的示例中,当每个信号迹线绕相邻一行的过孔反焊盘弯曲时,布线通道中两个信号迹线之间的间隙会发生变化。根据本技术的一个方面,在相邻行的过孔反焊盘(例如,过孔反焊盘402和406)彼此最接近的位置处,信号迹线彼此最接近。在图4中示出的示例中,信号迹线410和412在位置422处彼此最接近,该位置可以沿着连接过孔反焊盘

402和406的中心的直线。根据一个方面,信号迹线410和412之间的最小距离应大于信号迹线410和412宽度的两倍或三倍。在同一行中相邻过孔反焊盘之间的中点处,信号迹线彼此相距最远。例如,信号迹线410和412在位置424处彼此相距最远,该位置可以大致在相邻过孔反焊盘402和404之间的中点处。类似于图3中示出的,一个布线通道中信号迹线之间的最大间隙也受到相邻布线通道中信号迹线的约束。例如,信号迹线410和412之间在位置424处的间隙可能会受到同一位置处信号迹线410和414之间的间隙的约束。增大信号迹线410和412之间在位置424处的间隙会导致信号迹线410和414之间的间隙减小,这可能是有问题的,因为这会增加信号迹线410和414之间的串扰。注意,相邻布线通道中的相邻信号迹线(例如,迹线410和414)大部分被过孔反焊盘彼此分隔开,并且因此,它们之间在相邻过孔反焊盘之间的空间处的间隙决定了它们之间的串扰。根据一个方面,在相邻过孔之间的中点处(例如,在位置424处),通道内间隙(例如,同一布线通道中相邻信号迹线之间的间隙)和通道间间隙(例如,相邻布线通道中相邻信号迹线之间的间隙)可以是类似的。根据替代性方面,在相邻过孔之间的中点处(例如,在位置424处),通道内间隙可以大于通道间间隙(例如,大20%)。这是因为,一般来说,通道内串扰大于通道间串扰,并且更需要确保同一布线通道中信号迹线之间有足够的间隙。

30.在图3中示出的示例中,信号迹线310包裹每个过孔反焊盘的约50%,并且弧角θ可以约为π或180

°

。这可以使得信号迹线310上升超过过孔反焊盘302的中心,从而增大信号迹线310和312之间的间隙。然而,这种布置在图4中示出的示例中会造成问题。更具体地,如果信号迹线410上升超过过孔反焊盘402的中心,则所述信号迹线可能会太过接近包裹过孔反焊盘402的上部部分的信号迹线414。在最极端的情况下,信号迹线410和414各自包裹过孔反焊盘402的50%,这可以使得信号迹线410和414彼此接触或交叉路径。为了防止过度的通道间串扰,根据一个实施例,过孔反焊盘周界的被信号迹线包裹的部分可以高达40%,诸如介于0%到40%之间或介于20%到40%之间。

31.在图4中,这两个信号迹线对过孔反焊盘的包裹量可以基本上类似。例如,信号迹线410包裹顶行中每个过孔反焊盘(例如,过孔反焊盘402和404)的约40%,并且信号迹线412类似地包裹第二行中每个过孔反焊盘(例如,过孔反焊盘406)的约40%。这种布置可以确保增大迹线间隙,而不会增大信号迹线之间的长度差异。换句话说,soc覆盖区内的每个信号迹线的长度都可以保持基本上类似。然而,这也可能导致耦合信号的相位延迟发生周期性变化。为了防止相位延迟的周期性变化,根据一个方面,每个布线通道中的两个信号迹线绕过孔反焊盘可以具有不同的包裹深度。例如,信号迹线410可以包裹顶行中每个过孔反焊盘的约40%,而信号迹线412仅包裹第二行中每个过孔反焊盘的约30%。

32.在前面的讨论中,已经以类似方式处理了所有过孔,包括信号过孔和接地过孔两者。在信号平面上,信号迹线绕每个过孔周围的过孔反焊盘区域进行布线。对于信号过孔,信号平面中过孔反焊盘区域的位置和尺寸对应于接地参考平面上实际过孔反焊盘的位置和尺寸。另一方面,接地过孔在接地参考平面上不具有过孔反焊盘。然而,在图2至图4所示的示例中,信号迹线绕接地过孔进行布线,就好像每个接地过孔都具有与信号过孔类似的过孔反焊盘区域。这使得布设信号迹线的过程更简单。然而,由于信号迹线具有周期性结构,因此可能会发生高频滤波,导致频率依赖阻抗的变化或不需要的信号反射。

33.根据本技术的一个方面,可以利用接地过孔在接地参考平面中实际上不具有过孔

反焊盘这一事实,并且可以通过允许信号迹线的布线更接近接地过孔来以不同方式处理接地过孔和信号过孔。图5图示了根据本技术的一个方面的绕信号过孔和接地过孔对信号迹线进行布线。在图5中,信号平面500包括过孔反焊盘(例如,过孔反焊盘502-508)的阵列以及多个信号迹线(例如,迹线510和512)。对于每个过孔反焊盘,内圆表示孔,并且交叉阴影区域表示过孔焊盘。过孔反焊盘502和504与信号过孔相关联,其中所述过孔反焊盘的外部边界(表示为实心圆)由参考平面中对应的过孔反焊盘定义。另一方面,过孔反焊盘506和508与在信号平面中不具有过孔反焊盘的接地过孔相关联。过孔反焊盘506和508的外部边界由信号迹线可以绕对应接地过孔的过孔焊盘进行布线的紧密程度来决定。一般来说,信号迹线的布线离接地过孔可以比离信号过孔更近,这意味着接地过孔的等效过孔反焊盘(例如,接地过孔反焊盘506和508)小于信号过孔的过孔反焊盘(例如,信号过孔反焊盘502和504)。

34.在图5中,对信号过孔和接地过孔以不同方式进行处理,其中信号过孔反焊盘被示出为大于接地过孔反焊盘。图5还示出了每个信号迹线绕每个信号过孔反焊盘的实质部分进行布线,并绕接地过孔反焊盘的实质部分进行布线。更具体地,信号迹线的布线离接地过孔比离信号过孔更近。例如,信号迹线510包裹过孔反焊盘502、504和506中每个过孔反焊盘的一部分,并且信号迹线510与信号过孔反焊盘502或504的过孔焊盘之间的距离大于信号迹线510与接地过孔反焊盘506的过孔焊盘之间的距离。

35.由于接地过孔在某种程度上随机地散布在过孔阵列中,因此使布线信号绕信号过孔和接地过孔以不同方式进行布线会打破贯穿布线的重复性周期结构,从而降低高频滤波效应。此外,使信号迹线的布线更接近接地过孔还增大了这样的位置处信号迹线之间的间隙。例如,由于信号迹线512的布线更接近接地过孔反焊盘508的接地过孔,因此信号迹线510和512之间的间隙在与接地过孔反焊盘508相邻的位置处可以比在与信号过孔反焊盘相邻的位置处更大。

36.由于贯穿布线的空间约束,信号迹线被设计得很窄。例如,从soc覆盖区贯穿的信号迹线的宽度可以是约四密耳。这些窄迹线可能具有潜在的高阻抗,这是不期望的。为了降低信号迹线的阻抗,根据一个方面,在信号迹线之间的间隙相对较大的位置处,可以加宽一个或两个信号迹线。例如,在信号迹线之间的间隙达到最大值的位置处,可以加宽信号迹线中的一者或两者。

37.图6图示了根据本技术的一个方面的具有加宽段的信号迹线。在图6中,信号平面600可以包括两行过孔反焊盘,其中过孔反焊盘602和604定位在顶行,而过孔反焊盘606定位在底行。图6还示出了定位在顶行与底行之间的布线通道中的信号迹线610和612。图6中示出的贯穿布线方案可以类似于图2和图3中所示的方案,其中布线通道中只有一个信号迹线(例如,信号迹线610)绕每个过孔反焊盘的实质部分进行布线。类似于图3,信号迹线610和612之间的间隙可以在过孔反焊盘602和604之间的中点处最大。该相对较大的间隙允许信号迹线610在该位置处包括加宽段614。根据一个方面,加宽段614可以为锥形。

38.在图6中示出的示例中,只有一个信号迹线包括加宽段。在实践中,两个信号迹线都可以包括加宽段。例如,尽管未示出为加宽,但是信号迹线612也可以在相邻过孔反焊盘之间的位置(例如,位置616和618)处具有加宽段。根据一个方面,加宽段也可以随机地放置在贯穿布线路径中,以进一步打破贯穿布线的周期性,从而降低高频滤波效应。

39.图6还图示了过孔阵列的示例性行间距和列间距。过孔阵列的密度以及各个过孔的尺寸可以决定实现期望间隙(例如,在一行中相邻过孔之间的中点处的期望间隙)所需的对过孔反焊盘的包裹量。

40.图7呈现了根据本技术的一个方面的图示了在pcb上设计贯穿布线的过程的流程图。在操作期间,可以首先确定过孔的位置(操作702),并且识别哪些过孔是信号过孔以及哪些过孔是接地过孔(操作704)。然后确定每个信号过孔或接地过孔的过孔反焊盘或“阻进”区域(操作706)。根据设计,信号过孔和接地过孔的阻进区域可以相同,也可以不同。例如,接地过孔的阻进区域可以小于信号过孔的阻进区域。

41.对于从过孔阵列贯穿的每个信号迹线,可以确定包裹率(即,过孔反焊盘周界被信号迹线包裹所占的比例)(操作708)。根据一个方面,布线通道内的两个信号迹线可以具有相同的包裹率。根据替代性方面,同一布线中的两个信号迹线可以具有不同的包裹率,其中一个信号迹线包裹每个过孔反焊盘的更大一部分。此外,可以基于过孔阵列的间距(例如,行间距和列间距)和过孔反焊盘的尺寸来确定包裹率。更大的间距和/或更小的过孔可以意味着可以使用更小的包裹率来实现迹线之间的期望间隙。注意,期望的是,使得信号迹线之间的最小间隙大于信号迹线宽度的两倍或三倍。

42.一旦确定了包裹率,设计者就可以根据确定的包裹率绕过孔反焊盘来布设信号迹线的段(称为过孔反焊盘包裹段)(操作710),并且然后使用连接段连接每一对相邻的过孔反焊盘包裹段,以完成逸出soc覆盖区的信号迹线的布线(操作712)。连接段通常定位在相邻过孔反焊盘之间的空白空间,并且其曲率也可以基于过孔阵列的间距来确定。根据一个方面,连接段可以部分地被加宽以降低信号迹线的阻抗。根据进一步方面,连接段的加宽部分可以为锥形。然后,可以根据pcb设计完成过孔阵列外部的信号迹线的布线(操作714)。

43.总体上,本公开提供了一种用于减少pcb上集成电路器件的贯穿布线内的串扰的技术。更具体地,在信号迹线需要从大soc器件的高密度过孔阵列贯穿的情况下,布线通道中一对信号迹线之间的长耦合长度和紧密间隔会导致串扰量更大。为了减少串扰量,根据本技术的第一方面,布线通道中的一个信号迹线可以包括多个过孔反焊盘包裹段,其中每个过孔反焊盘包裹段都包裹对应过孔反焊盘的实质部分。根据期望间隙以及过孔阵列的间距,过孔反焊盘的周界的包裹部分(即,包裹率)可以变化(例如,在0%到50%之间变化,在25%到50%之间变化,或者在40%到50%之间变化)。根据第二方面,布线通道中的两个信号迹线都可以具有过孔反焊盘包裹部分。这两个信号迹线的包裹率可以相同,也可以不同。根据第三方面,信号过孔和接地过孔的过孔反焊盘或“阻进”区域可以以不同方式定义。接地过孔的“阻进”区域可以更小,以允许信号迹线的布线更接近接地过孔,从而进一步增大每个布线通道中信号迹线之间的间隙。根据第四方面,至少一个信号迹线可以包括一个或多个加宽段。加宽段可以位于同一行中相邻过孔反焊盘之间的区域中。

44.在所公开的示例(例如,图2至图6中示出的示例)中,信号迹线是定位在pcb内层上的带状线,并且贯穿布线用于将信号迹线布线通过过孔阵列。在实践中,可以使用相同的布线技术(例如,通过使信号迹线的一段包裹阻进区域的周界的一部分以绕阻进区域来布线信号迹线)将微带布线通过pcb的顶表面布线层上的接触焊盘阵列。此外,在所公开的示例中,所述过孔阵列是交错阵列。在实践中,可以使用同一布线技术将信号迹线布线通过任何形式的过孔或接触焊盘阵列。

45.本技术的一个方面提供了一种印刷电路板(pcb)。所述pcb可以包括多个层和过孔阵列,所述过孔阵列包括多个行,所述多个行被配置为跨层连接信号。所述pcb的内层可以包括定位在所述过孔的相邻的第一行和第二行之间的第一信号迹线和第二信号迹线,所述第一信号迹线与所述第一行相邻定位,并且所述第二信号迹线与所述第二行相邻定位。所述第一信号迹线可以包括绕所述第一行中的对应过孔的实质部分弯曲的至少一个弯曲段,使得所述第一信号迹线与所述第二信号迹线之间的间隙沿着所述弯曲段变化。

46.在关于此方面的变型中,所述弯曲段沿着与所述对应过孔相关联的过孔反焊盘区域的周界的一部分弯曲。

47.在进一步变型中,所述弯曲段沿着所述过孔反焊盘区域的所述周界的0%到50%弯曲。

48.在进一步变型中,所述对应过孔是信号过孔,并且所述信号过孔的所述过孔反焊盘区域对应于与所述第一信号迹线相关联的参考平面上的过孔反焊盘。

49.在进一步变型中,所述对应过孔是接地过孔,并且所述接地过孔的所述过孔反焊盘区域小于所述信号过孔的所述过孔反焊盘区域。

50.在关于此方面的变型中,所述第二信号迹线可以包括绕所述第二行中的对应过孔的实质部分弯曲的至少一个弯曲段。

51.在进一步变型中,所述第二信号迹线的所述弯曲段沿着所述第二行中所述过孔反焊盘区域的所述周界的0%到40%弯曲。

52.在关于此方面的变型中,至少一个信号迹线在所述第一信号迹线与所述第二信号迹线之间的所述间隙增大的位置处包括加宽部分。

53.在进一步变型中,所述加宽部分定位在同一行的相邻过孔之间。

54.在关于此方面的变型中,所述pcb可以进一步包括片上系统(soc)器件,所述片上系统器件包括耦合到所述过孔阵列的接触焊盘阵列。

55.本技术的一个方面提供了一种印刷电路板(pcb)的内层。所述内层可以包括:过孔阵列,所述过孔阵列包括多个行,所述多个行被配置为跨所述pcb的多个层连接信号;以及定位在所述过孔的相邻的第一行和第二行之间的第一信号迹线和第二信号迹线,所述第一信号迹线与所述第一行相邻定位,并且所述第二信号迹线与所述第二行相邻定位。所述第一信号迹线包括绕所述第一行中的对应过孔的实质部分弯曲的至少一个弯曲段,使得所述第一信号迹线与所述第二信号迹线之间的间隙沿着所述弯曲段变化。

56.在关于此方面的变型中,在所述第一行的相邻过孔之间的位置处所述第一信号迹线与所述第二信号迹线之间的所述间隙大于在所述第二行的相邻过孔之间的位置处所述第一信号迹线与所述第二信号迹线之间的所述间隙。

57.在具体实施方式部分中描述的方法和过程可以被体现为代码和/或数据,所述代码和/或数据可以被存储在如上所述的计算机可读存储介质中。当计算机系统读取并执行存储在计算机可读存储介质上的代码和/或数据时,所述计算机系统执行被体现为数据结构和代码并被存储在计算机可读存储介质内的方法和过程。

58.此外,上述方法和过程可以被包括在硬件模块或装置中。硬件模块或装置可以包括但不限于专用集成电路(asic)芯片、现场可编程门阵列(fpga)、在特定时间执行特定的软件模块或代码的专用或共享处理器、以及现在已知或以后开发的其他可编程逻辑器件。

在激活硬件模块或装置时,这些硬件模块或装置执行其中所包括的方法和过程。

59.已经仅出于说明和描述的目的呈现了前述描述。所述描述并非旨在是穷举的或将本公开的范围限制为所公开的形式。相应地,对于本领域普通技术人员而言,许多的修改和变化将是显而易见的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1